Цифровой нерекурсивный фильтр

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике. Цифровой нерекурсивный фильтр содержит регистр 1, блок 4 регистров, сумматор 5, блок 6 управления, блок 7 памяти, блок 8 регистров сдвига, коммутатор 9. Повышение быстродействия достигается введением в фильтр блока 2 элементов И, формирующего многострочный код, и преобразователя 3 кода, преобразующего многострочный код в двустрочный. 2 з.п. ф-лы, 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (I9) SU(II) 1 (5)) Н 03 Н 1 7/06

ОПИСАНИЕ ИЗОБРЕТЕНИЯ (5

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ

flQ ИЭОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ П<НТ СССР

К А ВТОРСКОМУ С8И4ЕТЕЛЬСТВУ

1 (2)). 4436825/24-09 (22) 06.06.88 (46) 23.05,90. Бк1л. У ) 9 (72) П.А. Брандис и В.Н.Пехота (53) 62) .374.334 (088.8) (56) Авторское свидетельство СССР

У 132242), кл. Н 03 Н 17/06, 1983. (54) ЦИФРОВОЙ НЕРЕКУРСИВНЬ Й ФИЛЬТР (57) Изобретение относится к радио2 технике. Цифровои нерекурсивныи фильтр содержит регистр 1, блок 4 регистров, сумматор 5, блок 6 управления, блок 7 памяти, блок 8 регистров сдвига, коммутатор 9. Повьппение быстродействия достигается введением и фильтр блока 2 элементов И, формиру ацего многострочньп" код, и преобразователя 3 кода, преобраэулцего многострочный код в двустрочный.

2 з.п. ф-лы, 5 ил.

1566472

М- у = ) а и =о х,; где х у — .входы чи-ел текуп их

II < - и отсчетов в х о,<«1«(1 Г о и

ПЫХОДНО1 О < И1 ПЛЛОВ устр<эй<с T«<;J < о(11<етственчо;

Изобретс ние <>тносится к радиотехгнп е, B члс тиос ти v шпЬровоР обрл— битке рлдио-, гидро — и эвуколокационных сигналов, и может быть применено для обработки сигнллс в с высо— кой частотой дискрети.<лпии в радиолокации, навиглпии, связи и других об— ла с тях техник и, где в о зможн<> и рименение КИХ вЂ” Филь тров . 10

Цеэп изобретения — п< вьппение быстродействия .

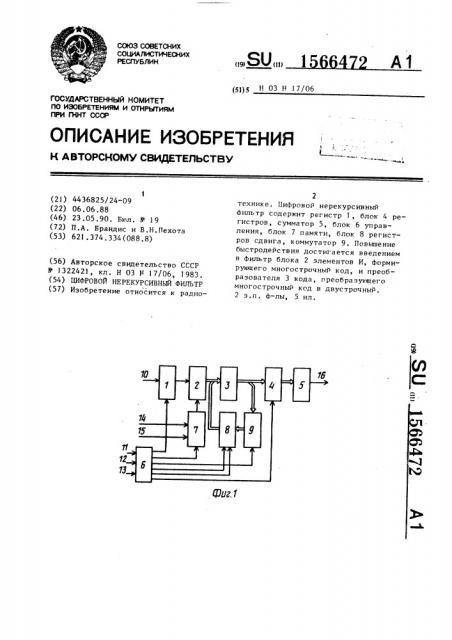

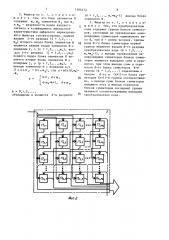

Нл фиг. I приведена электрическая структурная схема циФрового -«ерекурсивного фильтра; нл фиг. 2 — структур-15 ная электрическля схема блока элементов И на фиг. 3 — структурная электрическая схема преобразователя кода, ;«л Фиг. 4 — вид многострочного кода на выходе блока э«ементов И, входе и 20 выходе преобразователя кода, нл

Фиг. 5 — преобразовлние многострочного кода в двустрочньп< в преобразователе кода.

Цифровой нерекурсивный Фильтр со- 25 держит регистр 1, блок 2 элементов И, преобразователь 3 кодл, блок 4 регистров, сумматор 5, блок 6 управления, блок 7 памяти, блок 8 регистров сдвиг», коммутатор 9, вход 1 О, вход 11 нлчл:«ь-30 ной ус -.лновки, вход 1 2 устлновк«1 порядк.l тактовый вх< л 13, вход 14 .лп;«в си коэсЬФициентов, вход 1 5 разрешения записи к оэ<Ьфипиентов и выход 1 6, Блок

2 элел«ентов И сод<-ржит з>«еме>«ты И

17, < ...17 „> . Преобрл эовлтель 1. >цл

3 содержит группы блоков сумматор >в

18, с<><.тоящие из блоков суммлторо 1 1 9, клждьп< из которых содержит трехвходо— пые одноразрядные суммлторы 20. 40

Цифровой нерекурсивный Фильтр работает следунипим образом.

Предварительно р блок 7 памяти при наличии сигналов разрешения нл входе

15 с входа 14 заносятсч, к<» ..танты ло, R,<,..., л м< Фильтра соответственно по адресам Ь«-1, 1<«-2,,1,0, В рабочем режиме устройство работает в соответствии с уравнением нерекурсивного Фильтра 50 л — константы Фильтра, Г« — порядок Фильтра.

На вход 12 подается число Y-1, рлвное уменьшлемому на единицу порядку фильтрл. Злтем на вход 11 подается сигнал Логическая 1, соответству><>щий режиму начальнсн установки. 1«ри этом с первого и четвертого выходов блока 6 управления выдан тс я единич ные с иг налы. В первом такте рлботы (т.е. после первого тактового импульса) тактовь<х интервалов, Формируемых тактовыми импульсами, которые подают на вход 13, сигнал нлчаль ной установки с входа

11 снимают, переводя этим устройство в рабочий режим. При этом на п«естом выходе блока 6 упрлвления выдается управляющий сигнлл. Одновременно с пят< го выходл <лока 6 управления по"тупл<пт тактовые импульсы. В последнем 1-м такте рабочего цикла с первог(> выхода блока 6 управления выдас тся упрлвляк>щий сигнлл, а на третьем выходе блока 6 управления устанавливаетсяя сигнал, равный единице . Далее рабочий цикл повторяется в рабочем р жиме (т.е. пл первом входе блока

1( уll I>;l«Jëåí««>I 6 действует сигнал Логический !>, с оответству> щиР рабочему р ж>«м у), По у<«рлнлякщим сигналам с блока 6 в;.ежиме н»члльноР установки ци<Ьровой код гс.кущего с тсчета входного сигнл.пл зс<писывлется в регистр 1, происходит сброс блока 8 регистров сдвив нуль и устройство переводится раб<>чиР режим снятием сигнала начлэп.ной установки с входа 11. В первом такте рабочего цикла число из регистра 1 jjMH(»I:»åòñÿ в блоке 2 элементов И нл константу л, фильтра, результат умножения а;х „, в виде многострочного кодл (матрицы частичных произведений) поступает нл вход преобразователя 3 кода, на которьп« посту ; ет также двустрочный код с блока

8 регистров сдвига. На фиг.4с« и 4с> показаны соответственно матрица частичных произведений, поступающая с блока 2, и двустрочный код, поступакщий с блока 8. Результирунщи« многострочный код (шестистрочнь<й) на входе преобразовлтеля 3 кода показан нл фиг.4

Преобрлзов»тель 3 кодл содержит группы блок(>в сумматоров 1 8, состоящие из блоков сумматоров 19, обч,еди15664 няющие трехвходовые одноразрядные сумматоры 20 одинакового веса. В этом блоке осуществляется последовательное (за несколько тактов работы) преобра5 зование многострочного кода в двустрочньтй. На диаграммах этого преобразования (Фиг. 5) рамками обведены числа, подаваемые на вход одного трехвходового одноразрядного сумматора 20. Слева проставлены номера тактов преобразования. Многострочный код (Фиг.4 О) за три такта трехвходового одноразрядного сумматора 20 преобразуется в двустрочный код (фиг.5) . 15

Сформированный двустрочный код с преобразователя 3 кода записывается в блок 4 регистров путем подачи импульса записи с шестого выхода блока 6.

Двустрочный код результата, записанный в блок 4, с помощью сумматора 5 преобразуется к однострочному коду, причем на первый вход сумматора 5 подается первая строка, а на второй вход — вторая строка двустрочного кода. Однострочный код на выходе сумматора 5 есть результат фильтрации на данном такте работы устройства.

После записи кода в блок 4 (одновременно с работой сумматора 5) осуществляется М-1 сдвигов по кольцу содержимого блока 8 через преобразователь 3 кода и коммутатор 9. Синхронно с сдвигами на второй вход блока 2 элементов И подают константы ад, а<, ...,а „ < из блока 7. На выходе блока

2 элементов И формируются произведения числа из регистра 1 на константы 40

Фильтра (в виде многострочного кода) .

Полученные произведения суммируют с соответствующими двустрочными кодаИи чисел с выхода блока 8 и заносятся

В Hего дВустрОчным кОдОм с ВыхОда 45 преобразователя 3 кода через коммутатор 9, на управляющий вход которого поступают импульсы с третьего выхода блока 6.

Коммутатор состоит из payx rpynLI элементов 2И, первые входы элементов

2И обеих групп соединены между собой. и являются управляющим входом коммутатора. Вторые входы элементов 2И обеих групп элементов объединены в шину и являются инФормационным входом коммутатора 9. Входы обеих групп элементов 2И объединены в шину и являются выходом коммутатора 9. Каждая

72 6 из групп элементов 2И коммутирует одну из строк двустрочного кода.

В последнем М-м такте рабочегО цикла в блок 8 регистров сдвига записывается произведение а, х„, а в регистр 1 осуществляется запись нового значения текущего отсчета входного сигнала. Сдвиг информации (двус трочного кода) в блоке 8 регистров сдвига осуществляется под воздейст- . вием тактирующих импульсов, поступающих с пятого выхода блока 6. В М-м такте рабочего цикла производится установка в нуль блока 4 путем подачи сигнала с шестого выхода блока 6.

Далее рабочий цикл устройства повторяется.

Ф о р м у л а и з о б р е т е н и я

I . Цифровой нерекурсивгп Ф Фильтр, содержащий блок памяти, регистр, вход которого является входом цифрового нерекурсивного фильтра, входами записи и разрешения записи коэффициeH roB которого являются информационный вход и вход разрушения записи блока памяти соответственно, блок регистров, сумматор, блок регистров сдвига, коммутатор, выходы которого соединены с входами блока регистров сдвига, и блок управления, первь й, второй и третий входы которого являются входами начальной установки, установки порядка и тактовым входом цифрового нерекурсивного фильтра соответстственно, а выходы блока управления с первого по шестой соединены с входом записи регистра, адресным входом блока памяти, управляющич входом коммутатора, входами сброса и записи блока регистров сдвига и входом записи блока регистров соответственно, отличающийся тем, что, с целью повышения быстродействия, введены блок элементов И, первый и второй входы которого соединены с выходами регистра и блока памяти соответственно, и преобразователь кода, входы которого соединены с соответствукщими выходами блока элементов И и блока регистров сдвига, а выходы преобразователя кода соединены с соответствующими входами коммутатора и блока регистров, входы которого соединень с входами сумматора, выход которого является выходом цифрового нерекурсивпого Фильтра.

1566472

2. Фильтр по и. 1, о т л и ч а юшийся тем, что блок элементов И содержит m,. m элементов И где ш и ш — paэрядности кодов входного сигнала и коэффициента импульсной характеристики цифрового нерекурсивного фильтра соответственно, причем входом i-го разряда (i = 1,2,..., m ) второго входа блока элементов И являются первые входы элементов И с номерами r, i (г = ),2,...,ш,), вхо,дом j-f o разряда (j 1,2,...,ш„,) первого входа блока элементов И являются вторые входы элементов И с номерами ), р (р = ),2,...,ше), а выходы элементов И с номерами u v

15 с k+I, d

-k (d = 1,2,..., m<+m <-1) выхода блока элементов И.

3. Фильтр по и. 1, о т л и ч а юшийся тем, что преобразователь кода содержит группы блоков сумматоров, состоящих из трехвходовьж одноразрядных сумматоров, одинакового веса d, где d — номер разряда, причем вход d-го блока сумматоров первой группы является входом d-го разряда преобразователя кода (d = 1,2,..., m +m -1), а выходы трехвходовых одноразрядных сумматоров блоков сумматоров являются выходами сумм и переносов, при этом выходы сумм и переносов d-го блока сумматоров k-й группы (k = 1,2,....) подключены к входам d-ro и (d+1)-го блока сумматоров (k+I)-й группы соответственно, а выходы сумм блоков сумматоров младшего веса и выходы переносов блоков сумматоров последней группы являются соответствующими выходами преобразователя кода.

1566472

7 654521 д ° ° ° ° ° ° °

° ° ° ° ° у gp4531

Ю

° ° ° ° ° ° °

° ° ° ° ° ° °

76 Х4 У

° ° ° ° °

° ° ° ° ° ° °

° ° ° ° ° ° °

° ° ° ° °

° ° °

1566472 о 7 ЕХ4921

° ° ° ° ° ° ° °

° ° ° °

Со с тавитель С . Муэычук

Техред М. Ходанич Корректор 3.Лончакова

Редактор И. Шулла

Заказ 1228 Тирах 651 Подписное

ВНИКНИ Государственного комитета по иэобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, уп. Гагарина, 101

ПП