Устройство для контроля блоков памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для функционального контроля и определения области устойчивой работы блоков оперативной памяти. Целью изобретения является упрощение устройства и расширение области применения за счет возможности генерации произвольных тестовых последовательностей. Устройство содержит блок 1 сопряжения, первый регистр 2 данных, первый регистр 3 адреса, блок 4 задания частот, первый триггер 5 управления, триггер 6 записи/чтения, третий регистр 7 данных, блок 8 формирования временных диаграмм, триггер 9 ошибки, второй регистр 10 данных, второй регистр 11 адреса, элемент НЕ 12, второй триггер 13 управления, первый 14 и второй 15 цифроаналоговые преобразователи, элемент 16 задержки, первый 17 и второй 18 элементы И-НЕ, проверяемый блок 19 памяти, регистр 20 результата, блок 21 сравнения, вспомогательный регистр 22 результата, элемент И 23. Устройство позволяет проводить функциональный контроль блоков оперативной памяти на произвольных тестовых последовательностях на предельной (рабочей) частоте работы блока памяти. 6 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (1)э 6 11 С 29/00

OllH0AHHE ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

flPH ГКНТ СССР..1 (21) 4444565/24-24 (22) 20.06,88 (46) 07.06.90. Бюл, @21 (71) Московский энергетический институт (72) 1П.В.Сычев и Д.И.Дудукин (53) 681.327,6 (088,8) (56) Измерения параметров цифровых интегральных микросхем. /Под ред.

Д.N.ÝÉäóêàñà, Б.В,Орлова. M. Радио и связь, 1982, с.386.

Авторское свидетельство CCCP

0- 1236558, кл. G 11 С ?9/00, 1 984.

„.ЯО„„ЩЩЩД А1

2 (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ

ПАМЯТИ (57) Изобретение относится к вычислительной технике и может бытЬ использовано для функционального контроля и определения области устойчивой работы блоков оперативной памяти. Целью изобретения является упрощение устройства и расширение области применения эа счет возможности генерации произвольных тестовых последовательнс1стей. Устройство содержит блок 1 задания начальных условий и анализа результата, первый регистр 2 данных, ! 569903 первый регистр 3 адреса, блок 4 задания частот, первый триггер 5 управления, триггер 6 записи-чтения,третий регистр 7 данных, блок 8 формирования временных диаграмм, триггер

9 ошибки, второй регистр 10 данных, второй регистр 11 адреса, элемент

НЕ 12, второй триггер 13 управления, первый 14 и второй 15 цифроаналоговые преобразователи, элемент 16 заИзобретение относится к вычисли тельной технике и может быть использовано для функционального контроля оперативных запоминающих устройств ,(ЗУ) и определения их области устой- 20 чйвой работы, Целью изобретения является упрощение, устройства и расширение области применения за счет возможности генерации произвольных тестовых после- 25 довательностей.

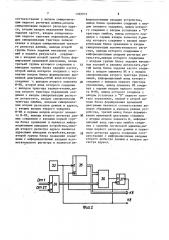

На фиг,l приведена функциональная схема устройства для контроля блоков памяти; на фиг,2 — функциональная схема блока задания частот, на, 30 фиг. 3 — функциональная схема блока формирования временных диаграмм; на фиг 4 — функциональная схема блока сравнения; на фиг,5 — функциональная схема блока задания начальных условий 35 и анализа результата ", на фиг. 6 функциональная, схема шинного формирователя.

Устрбйство содержит блок 1 задания начальных условий и анализа ре- 40 зультата, первый регистр 2 данных, первый регистр 3 адреса, блок 4 задания частот, первый управляющий триггер 5, триггер 6 записи-чтения, третий регистр 7 данных, блок 8 фор- g5 мирования временных диаграмм, триггер

9 ошибки, второй регистр 10 данных, второй регистр 11 адреса, элемент

HE 1 2, второй управляющий триггер 13, первый 14.и второй 15 цифроаналого- 50 вые преобразователи, элемент 16.задержки, первый 17 и второй 18 элементы И-НЕ, проверяемьй блок 19 памяти, регистр 20 результата, блок 21 сравнения, вспомогательный регистр 22 результата, элемент И 23, информационный вход 24 блока 1, управляющие выходы 25-31 блока 1, выход 32 управления блока формирования времендержки, первый и второй элементы

И-НЕ 17, 18, проверяемый блок 19 памяти, регистр 20 результата, блок 21 сравнения, вспомогательный регистр

22 результата, элемент И 23. Устройство позволяет проводить функциональный контроль блоков оперативной памяти на произвольных тестовых последо" вательностях на предельной (рабочейf частоте работы блока памяти. 6 ил. ных диаграмм, генератор 33 тактовых . импульсов, регистр 34, счетчик 35, схему 36 сравнения, триггер 27,регистры 38-43, схемы 44-49 сравнения, элементы И-НЕ 50-55, элемент НЕ 56, триггеры 57-59, элемент И-HE 60, элемент И-HE 61, элементы исключающее

ИЛИ 62-65,, элемент ИЛИ 66, элемент

И 67, шинный формирователь 68,буфер" ный усилитель 69, схему, 70 сравнения, элементы И 71 и 72, регистр 73, элемент И 14, элемент ИЛИ 75, триггер 76, дешифратор 77, резистор 78, конденсатор 79, буферный усилитель

80 входы 81 второй группы схемы сравнения, элементы 82 и 83 с открытым коллекторным выходом и элементы

HE 84 и 85.

Устройство для контроля блоков памяти работает следующим образом.

Устройство представляет собой адаптер, подключенный, например, к интерфейсу ЭВМ типа "ДВК" или "Электроника-60", и содержит программируемые регистры. в которые информация может записываться из ЭВМ. Один из регистров предназначен для чтения информации со стороны ЭВМ. В него заносятся результаты контроля. При этом старшие разряды адреса предназначаются для выбора адаптера, а млад" шие разряды — для выбора регистра внутри адаптера. На входах 81,схемы

70 сравнения задается код адреса,по которому адаптер подключается к ЭВИ.

Формирование тестовых последовательностей в устройстве осуществляется программным способом с помощью

ЭВМ.

Перед началом работы устройства

ЭВМ загружает регистры 2 и 3 кодами данных и адресов. В триггер 6 записывается код режима работы блока па- мяти (первоначальная команда — за5 5699 пись). В регистр 7 записывается кол напряжений питания, поступающих на клеммы питания блока памяти. В регистры 38-43 блока Формирования времен5 ных диаграмм записываются коды значений переднего и заднего фронтов сигналов, управляющих работой блока памяти, Триггеры 5, 9 и 13 также устанавливаются в исходное состояние 10 (цепи "Сброс" условно не показаны).

В регистр 34 блока задания частот записывается значение кода цикла записи-чтения проверяемого блока памяти. 15

Блок 1 представляет собой известное устройство для подключения к

ЭВМ типа "Электроника "60", На входы буферного усилителя поступают сигналы П1А, "Ввод", "Вывод", "Байт". 20

По команде на ЭВМ триггер 5 устанавливается в. единичное состояние, что приводит к тому, что по сигналу с блока задания частот триггер 13 изменяет свое состояние из логического "0" в логическую "1". По сигналу с выхода триггера 13 в регистры

10 и 11 переписывается содержимое регистров 2 и 3 и начинается контроль блока памяти. На выходе элемен- 30 та 17 вырабатывается сигнал логического "0", который сбрасывает триггер

5 в исходное состояние. Следующим импульсом с блока задания частот триггер 13 устанавливается в исходное (нулевое) состояние, что обеспечивает режим многократного считывания информации иэ блока памяти с ее сравнением.

Сравнение считываемой и записан- 40 ной в блок памяти информации осуществляется блоком 21 сравнения, В то время как блок памяти контролируется, ЭВМ перегружает регистры данных

2 и адреса 3, анализирует состояние 45 регистра 20 результата контроля, Предлагаемое устройство позволяет формировать произвольные тестовые последовательности и .программы контроля с помощью ЭВМ, обеспечивая контроль блоков памяти на их предельной (рабочей) частоте.

Кроме того, устройство позволяет определять область устойчивой работы блоков памяти-в; координатах напря- у жений питания и временных параметров за Возможности программного изменения значенйй напряжений питания и временных параметров, 03

Технико-экономическое преимущество предлагаемого устройства заключается в уменьшении яппаратурных затрат, воэможности контроля блоков памяти на их предельной частоте, возможности генерации произвольных тестовых последовательностей и программ контроля.

Формула изобретения

Устройство для контроля блоков памяти, содержащее первый и второй регистры адреса, блок сравнения, регистр результата, блок задания частот, первый регистр данных, блок задания начальных условий и анализа результата, входы-выходы которого являются управляющими входами-выходами и входами-выходами адрес-данные устройства, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства и расширения области применения

sa счет воэможности генерации произвольных тестовых последовательностей, в него введены второй и третий регистры данных, триггеры ошибки,триггер записи-чтения, вспомогательный регистр результата, элемент задержки, первый и второй цифроаналоговые преобразователи, два управляющих триггера, блок формирования временной диаграммы, элемент HE два элемента

И-HF. элемент И, причем выходы первого и второго цифроаналоговых преобразователей являются соответственно первым и вторым управлякщнми выходами устройства, входи грулль< первого и второго цифроаналоговых преобразователей соединены соответственно с выходами первой и второй групп третьего регистра данных, информационные входы которого соединены с выходами первой группы блока задания начальных условий и анализа результата, с информационными входами первого регистра данных, с информационньии входаии первого регистра адреса, с входами первой группы блока формирования временной диаграммы, с входами первой группы блока задания частот,информационньм входом первого триггера управления, информационным входом триггера записи-чтения, первый, второй, третий, четвертый, пятый и шестой выходы блока задания начальных условий и анализа результата соединены

7 1569903 в соответственно с входом синхронизации первого, регистра данных, входом .синхронизации первого регистра адреса, вторым входом управления блока задания частот, входом синхронизации первого триггера управления,входом синхронизации триггера записичтения и входом синхронизации третьего регистра данных, выходы второй группы блока задания начальных усло вий и анализа результата соединены с входами второй группй блока формирования временной диаграммы, входы третьей группы которого соединены с выходами группы блока задания частот, второй выход которого соединен с четвертым входом блока формирования временной диаграммы, пятый вход которого соединен с выходом второго элемента

И-НЕ, второй вход которого соединен с выходом триггера записи-чтения,выход второго триггера управления соединен с входом синхронизации регистра результата, входом синхронизации триггера ошибки, входами синхронизации вторых регистров данных и адреса, с вторым входом первого элемента

И-НЕ и первым входом второго элемента И-HF. выходы второго регистра данных соединены с входами первой группы блока сравнения и. являются информационными выходами устройства,выходы второго регистра адреса являются адресными выходами устройства, входы второй группы блока сравнения соединены с информационными входами вспомогательного регистра и являются1информационными входами устройства, выход блока сравнения соединен с входом элемента задержки, выход которо5 го соединен с входом установки в "0" триггера ошибки, выход которого соединен с первым входом элемента И,выход которого соединен с входом синхронизации,блока сравнения и входом синхронизации вспомогательного регистра, выходы которого соединены с информационными входами регистра результата,выходы которого соединены с входами группы блока задания началь15 ных условий и анализа результата,третий выход блока задания частот соединен с входом элемента HF. и с входом синхронизации второго триггера управлений, информационный вход которого соединен с выходом первого триггера управления» выход элемента HF. соединен с первым входом первого элемента И-НЕ» выход которого соединен с входом установки в "0" первого триггера .управления, первый и второй выходы блока формирования временной диаграммы являются соответственно .выходом обращения и выходом режима устройства, третий выход блока формиро30. вания временной диаграммы соединен с вторым входом элемента И, информационный вход триггера ошибки соединен с уровнем логической еднницы,выходы первого регистра данных и первового регистра адреса соединены соответственно с информационными входами второго регистра данных и второго ре" гистра адреса.

1569903

Фиг. 3

1569903

Составитель В,Чоботова

Техред M,Õîäaêè÷ . Корректор О,Циппе

Редактор А.Шандор

Заказ 1454 Тираж 486 Подписное

ВНЙИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

1 13035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101