Масштабный преобразователь кодов

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и предназначено для преобразования кодов с различными весовыми коэффициентами. Целью изобретения является повышение быстродействия и достоверности преобразования. Цель достигается тем, что в преобразователь, содержащий входной и выходной счетчики 3 и 7, первый и второй делители 5 и 6 частоты, генератор 1 импульсов, введены входной регистр 2, схема 4 сравнения, третий делитель 11 частоты и блок 12 управления. 1 з.п. ф-лы, 4 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБ Лик р)) Н 03 M 7/12

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСИОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4447403/24-24 (22) 25.04.88 (46) 07.06.90.- Бюл. У 21 (72) В.Г. Потопальский и В.К. Сопрунов (53) 681. 325 (088 ° 8) (56) Авторское свидетельство СССР

У 1206960, кл. Н 03 М 7/ 12, 1986.

Авторское свидетельство СССР

В 744545, кл. Н 03 М 7/ 12, 1980. (54) МАСШТАБНЫЙ ПРЕОБРАЗОВАТЕЛЬ КОДОВ (57) Изобретение относится к автомати„„80„„1569994 А 1

2 ке и вычислительной технике и предназначено для преобразования кодов с различными весовыми коэффициентами.

Целью изобретения является повышение быстродействия и достоверности преобразования. Цель достигается тем, что в преобразователь, содержащий входной и выходной счетчики 3 и 7, первый и второй делители 5 и 6 частоты генератор 1 импульсов, введены входной регистр 2, схема 4 сравнения, третий делитель 11 частоты и блок 12 управления. 1 з.п. ф-лы, 4 ил. !569994

Изобретение относится к автоматике и вычислительной технике и предназначено для преобразования кодов с различными весовыми коэффициентами.

Целью изобретения является повышение быстродействия и достоверности преобразования.

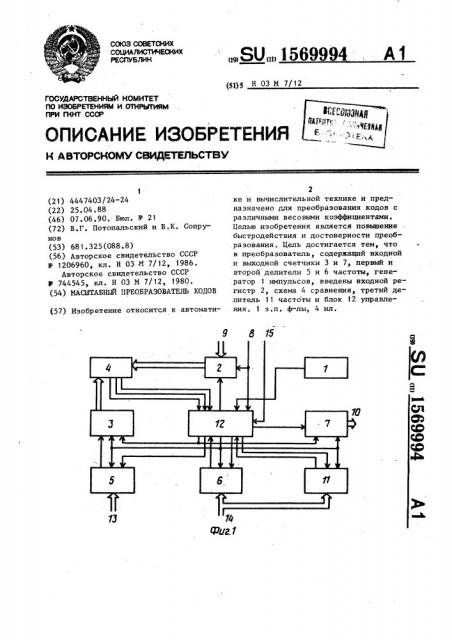

На фиг. 1 представлена функциональная схема преобразователя кодов; на фиг. 2 — схема блока управления; на фиг, 3 и 4 — временные диаграммы, по ясняющие работу преобразователя.

Преобразователь кодов (фиг. 1) со( держит генератор 1 импульсов, входной 15 регистр 2, входной счетчик 3, схему 4 сравнения, первый и второй 6 делители, частоты, выходной счетчик 7,вход на чальной установки преобразователя 8 кодо:в, информационный вход 9 преоб- 2О

i разователя, вход 10 преобразователя, третий делитель частоты 11, блок управления 12, вход 13 установки масштабного коэффициента входного счетчи à, вход 14 установки масштабного 25 коэффициента выходного счетчика, сигнал записи входного кода (ЗВК) 15.

Блок 12 управления содержит (фиг.2)

D-триггеры 16-21, элементы И 22-25, элементы ИЛИ 26-30, элемент ИСКЛЮЧАЮ- 3Q

4ЕЕ ИЛИ 31 RS-триггер 32, элементы

ИЛИ-НЕ 33-35.

Преобразователь работает следующим образом.

В исходном состоянии поступает ну-.3S левой сигнал записи входного кода на вход 15 и после поступления по входу

8 сигнала начальной установки появляется. нулевой код на выходах входного регистра 2. При этом на выходе сброса О блока 12 управления вырабатывается сигнал "Сброс" (фиг. 3)» по которому делители 5,6 и 11 частоты и счетчики

3 и 7 устанавливаются в исходное нулевое состояние. На выходе приема 45 блока 12 управления, соединенном со синхровходом записи входного регистра

2 появляется нулевой сигнал (Зап, фиг;, 3). Сигналом высокого уровня с выхода управления счетом блока 12 уп- 50 равления счетчики 3 и 7 установлены в режим прямого счета, с выходов блока 12 управления на счетные тактовые входы аоответственно делителей 5,6 и

11 (С1, С2, С3 фиг. 3) и счетный вход счетчика 7 не поступает импульсов и поэтому не поступают импульсы с выхода первого делителя 5 частоты (СИ1, фиг. 3) на счетный вход счетчика 3, с выходов делителей 6 и 11 (СИ2, СИЗ, фиг. 3) на входы блока 12 управления. В соответствии с функциональ» ным назначением входов схемы 4 сравЬ нения (соответственно а (—, а ) Ъ, а = Ъ, где а и Ъ вЂ” величины кодов на первых и вторых входах схемы сравнения) на ее первом и втором выходах сигнал низкого уровня, а на третьем— высокого, После установки на выходах 9 кода, на вход 15 подается сигнал записи входного кода (ЗВК, фиг. 3). По первому положительному фронту тактирующих импульсов, поступающих с выхода генератора 1, на выходе приема блока управления формируется сигнал записи во входной регистр 2 (Зап, фиг. 3) длительностью один такт тактирующих импульсов.

По этому сигналу производится запись входного кода преобразователя во входной регистр 2, а также разрешается формирование сигнала "Сброс" (фиг. 3) на выходе сброса блока 12 управления по отрицательному фронту тактирующих импульсов после появления логической "1" на первом выходе схемы

4 сравнения (при выполнении условия ас 2)

Ь

В случае, если величина вновь пришедшего кода не равна величине кода на выходах счетчика 3, т.е. по следующему положительному фронту тактирующих импульсов, разрешена работа второго 6 и третьего 11 делителей частоты. На тактовых входах указанных делителей частоты появляются счетные импульсы С2, СЗ с вйходов блока 12 управления (инвертированные счетные импульсы С1, С2, СЗ поступают с частотой тактирующих импульсов), Счет внутренних счетчиков делителей частоты осуществляется по положительному фронту счетных импульсов с коэффициентом деления равным коду на в .,одах 13 и 14 установки масштабного коэффициента счетчиков . Причем на выходах делителей формируются импульсы длительностью один такт счетных им пульсов, которые производят своим положительным фронтом счет выходного ,счетчика. Счет второго и третьего делителей частоты осуществляется до появления уровня логической "1" на их выходах СИ2, СИЗ. Так как первый код, 1569994 записанный во входной регистр после подачи внешнего сигнала начальной установки больше кода на выходах первого счетчика 3 (если не равен нулю), то на выходе Больше схемы 4 сравнеII tf 5 ния (а > b) к этому времени сформирован уровень логической "1" (по сигналу начальной установки на выходах первого счетчика 3 формируется код — все нули, а на выходах второго счетчика .

7 — код — все единицы). Блок управления, анализируя состояние схемы 4 сравнения, по первому положительному фронту тактирующих импульсов после по-15 появления логической "1" на выходах делителей 6 и 11 (СИ2, СИЗ) запрещает прохождение счетных импульсов на третий делитель СЗ (фиг. 3) и разрешает прохождение счетных импульсов на первый делитель 5 частоты С1. Поскольку прохождение счетных импульсов на тактовый вход делителя 11 запрещено, то на выходе указанного делителя поддерживается уровень логической "1". 25

Импульсы на выходах первого и второго делителей частоты СИ1, СИ2 возникают в соответствии с заданными коэффициентами деления (пропорциональными соотношению весов младшего разряда входного и выходного кода преобразователя кодов), до появления логической "1" на выходе "Равно" схемы 4 сравнения (a=b). По первому положительному фронту тактирующих импульсов с генератора импульсов запрещается прохождение счетных импульсов на все три делителя частоты. В результате на выходе первого делителя частоты сохраняется уровень логической "1", а во внутреннем счетчике второго де40 лителя частоты запоминается последний просчитанный код. Разрешается формирование сигнала "Запись 1 во входной регистр. Запоминается последний

45 просчитанный код в выходном счетчике (он же выходной код преобразователя).

В данном состоянии преобразователь остается до появления следующего сигнала ЗВК (фиг. 3) на входе блока

12 управления.

По первому положительному фронту тактирующих импульсов после появления сигнала ЗВК формируется сигнал записи во входной регистр.В случае, если ве55 личина вновь пришедшего кода меньше кода, хранящегося на выходах входного счетчика, но больше половины этого кода, то на всех трех входах блока сравнения возникает уровень логического "О". Блок управления, проанализировав эту ситуацию, разрешает прохождение счетных импульсов С2 и СЗ на второй и третий делитель частоты и запрещает прохождение С1 на счетный вход первого делителя до появления уровня логической "1" на выходе второго делителя. Этот уровень возникает при переполнении внутреннего счетчика второго делителя частоты. После этого блок управления запрещает прохождение счетных импульсов на тактовый вход второго делителя и разрешает прохождение счетных импульсов на тактовый вход первого делителя. К этому моменту внутренний счетчик третьего делителя накопил остаток внутреннего счетчика второго делителя до переполнения от счета предыдущего кода и работа третьего делителя продолжается. Теперь счетными для второго счетчика будут импульсы не второго,а третьего делителя частоты.

Направление счета входного и выходного счетчика при этом меняется на противоположное изменением логического уровня на выходе блока управления.

Таким образом поддерживается соответствие разрядных сеток входного и выходного счетчиков.. Счет первого и третьего делителей частоты продолжается до совпадения кодов входного счетчика и входного регистра.

Если после записи нового кода во входной регистр окажется, что этот код опять меньше кода входного счетчика, то процесс счета первого и третьего делителей частоты будет продолжен с величины кода хранимого во внутреннем счетчике третьего делителя и направление счета входного и выходного счетчиков не изменится.

Если величина вновь записанного во входной регистр 2 кода больше кода хранимого во входном счетчике 3, то блоком 12 управления разрешается прохождение счетных импульсов на тактовые входы второго и третьего делителей С2, СЗ и запрещено прохождение счетных импульсов на тактовый вход первого делителя 5 частоты до момента возникновения уровня логической "1" на выходе третьего делителя частоты.

Причем направление счета обоих счетчиков меняется именно в этот момент времени. На этот раз запрещается прохождение счетных импульсов СЗ на так1569994 товый вход третьего делителя и разрешается прохождение счетных импульсов

С1 и С2 первого и второго делителей.

Счет внутреннего счетчика второго де5 лителя осуществляется после изменения направления счета со значения, равного остатку до переполнения внутреннего счетчика третьего делителя.

В случае, если величина вновь при- 10 шедшего кода на входы преобразователя

9 меньше половины кода хранимого во входном счетчике, то блоком управления формируется сигнал "Сброс", переводящий преобразователь в исходное состояние, за исключением сброса входного регистра, поскольку в этом случае счет всего значения входного кода происходит быстрее, чем досчет от предыдущего значения хранящегося в вход- 20 ном счетчике.

Блок управления (фиг. 2) работает следующим образом.

В исходном состоянии сигнал ЗВК нулевой. Поэтому несмотря на то, что 25 на первый тактовый вход блока 12 управления, соединенный с .синхронизирующими входами D-триггеров 16 — 18, 20 и 21, а также первыми входами элементов ИЛИ-HE 33 — 35 поступают такто-30 вые импульсы с выхода генератора 1, на прямом выходе 9-триггера 17, сое. диненном через выход приема кода блока 12 управления с синхровходом записи входного регистра 2, сформирован потенциальный сигнал Зап уровнем логического "0". Этим же сигналом, независимо от сигналов на синхронизирующем входе D-триггера 20 и О-входе того же триггера на прямом выходе 40 .D-триггера 20 сформирован потенциальный сигнал уровнем логического "0".

Поэтому до прихода сигнала начальной установки с входной шины преобразователя 8 кодов, поступающего через 45 вход начальной установки блока 12 управления на первый вход элемента ИЛИ

28, на выходе этого элемента, соединенном через выход сброса блока 12 управления с входами сброса входного 50

3 и выходного 7 .счетчиков, первого

5, второго 6 и третьего 11 делителей частоты, установлен сигнал логического "0".

Сигнал (а=Ь) на прямом выходе

D""òðèããåðà 16 зависит от уровня входного сигнала, поступающего на вход

D а=Ь с входа блока 12 управления, соединенного с выходом схемы 4 сравнения.

Сигнал с выхода D-триггера 16 управляет формированием через элементы

ИЛИ 29 и 26 счетных импульсов С1 с выхода элемента ИЛИ-НЕ 35, поступающих через выход блока 12 управления на тактовый вход первого делителя 5 частоты, импульсов С2 с выхода элемента ИЛИ-НЕ 33 через выход блока 12 управления на тактовый вход второго делителя 6 частоты, импульсом С3 с выхода элемента ИЛИ-HE 34 через выход блока 12 управления на тактовый вход третьего делителя 11 частоты. Так как на синхронизирующем входе D-триггера

19 присутствует сигнал логической "1" с инверсного выхода D-триггера 17, то вне зависимости от сигнала на его

D-входе, на его выходах (прямом и инверсном) сохраняются сигналы, произвольно установленные в момент подачи питания на преобразователь кодов.Сигналы с выходов D-триггера 19 выполняют функцию аналогичную D-триггеру 16 (управление формированием счетных импульсов делителей 5,6 и 11), а также управляют RS-триггером 32. Сигналами с прямого и инверсного выходов RSтриггера 32 производится управление .элементами И 24 и 25, выполняющими роль коммутатора выходных импульсов

СИ2, СИЗ (фиг. 5) второго и третьего делителей б и 11 частоты. При этом второй вход элемента И 24 соединен с выходом второго делителя б, а первый вход элемента И 25 — с выходом третьего делителя 11 частоты. Сигналы с ,выходов элементов И 24 и 25 через элемент ИЛИ .30 проходят в виде сигна=лов СИ через выход блока 12 управления на счетный вход выходного счетчика 7, В зависимости от того на прямом или инверсном выходе триггера 19 устанавливает уровень логической "1", уев знавливается соответственно нулевой логический уровень на выходе D-триггера 18 (Х1, фиг, 3 и 4) либо на выходе D-триггера 21 (Х2, фиг. 3 и 4).

Другой сигнал из указанных двух "следит" за состоянием второго входа пересчетных импульсов блока 12 управления. Сигналы .Х1 и Х2 выполняют функцию управления формированием счетных импульсов С1, С2, СЗ поступакщих на

9 15699 тактовые входы первого 5, второго 6 и третьего 11 делителей частоты преобразователей, а также принимают участие в формировании сигнала направления счета.

После прихода сигнала начальной установки на вход начальной установки блока 12 управления уровнем логичесI кой "1" этот сигнал через элемент

ИЛИ 28 производит установку сигнала логической "1" на прямом выходе Dтриггера 19 (а ) b), сбрасывает в ноль внутренние счетчики делителей 5, 6 и

1 1 частоты, устанавливает в ноль на выходах входного счетчика 3, код— все единицы — на выходах выходного счетчика 7, а через элемент ИЛИ 27 устанавливает на прямом выходе RSтриггера 32 сигнал -„.-оовня логической 20

"1". Этот сигнал разрешает прохождение импульсов с выхода второго делителя СИ2 через элементы И 24 и ИЛИ 30 на счетный вход второго счетчика ? (СИ). Одновременно сигнал уровнем логического "0" с инверсного выхода

RS-триггера 32 запрещает прохождение импульсов с выхода третьего делителя

11 частоты преобразователя кодов СИЗ через элемент И 25. Сигналом с прямого 30 выхода D-триггера 19 устанавливается в ноль сигнал Х1 на выходе D-триггера

18, а так как импульсы СИЗ на выходе третьего делителя 11 частоты отсутст-, вуют, то сигнал Х2 на выходе D-триггера 21 устанавливается также в ноль по положительному фронту тактовых импульсон с выхода задающего генератора 1.. При этом сигналы Х1 и Х2 запрещают изменение сигнала на выходе R3 триггера 32 через элементы И 22 и 23 с выходов триггера 19.

Так как сигналом начальной установки преобразователя кодов по входу 8 производится сброс входного регистра

2, а сигналом с выхода сброса блока

t2 управления сбрасывается в ноль . код на выходах входного счетчика, то на выходе "Равно" схемы 4 сравнения, соединенном с входом IIpHsHRKB "Рав- 50 нс" блока 12 управления формируется сигнал уровнем логической "i". По очередному положительному фронту тактовых импульсов с задающего генератора этот сигнал появляется на выходе

D-триггера 16, также запрещая через элементы ИЛИ 29 и 26 формирование счетных импульсов на выходах элементов ИЛИ-.НЕ 33 — 35.

94 10

В рассмотренном состоянии блок управления находится до появления сигнала ЗВК,. По этому сигналу разрешается работа триггера 17 и по первому положительному фронту тактового сигнала с генератора 1 на прямом выходе триггера 17 формируется сигнал Зап (фиг. 4) уровнем логической "1", которым производится запись кода, предварительно сформированного на входе

9 преобразователя кодов, во входной регистр 2.

Поэтому к моменту прихода следук=. щего положительного фронта тактов;; импульса на синхронизирующие входы

1 триггеров 16 и 17 íà D-входах триггеров 16 и 17 сформирован уровень логического "0", а на D-входе триггера

19 сформирован с выхода "Больше" схемы 4 сравнения сигнала а ) Ь уровнем логической "1". По очередному положительному фронту тактового импульса н синхронизирующих входах триггеров 1 и 17 на прямых выходах этих триггерсформируются уровни логического "0"„ положительным фронтом с инверсного выхода триггера 17 сигнал а > Ь уровен"логической "1" на; входе триггера 19 переписывается на прямой выход последнего (в данном случае подтверждая установку триггера в единицу сигналом с входа сброса блока 12 управления).

Уровень логического "0" с прямого вы.хода триггера 16, формируя уровни логического "0" на выходах элементов

ИЛИ 29 и 26, разрешает прохождение тактовых импульсов генератора 1 с первого тактового входа блока 12 управления через элементы ИЛИ-НЕ 33 и 30 (сигналы С2, СЗ, фиг. 3) на счетные входы второго 6 и третьего 11 делителей частоты и формированием уров»:-.-: -.1;. — . гической "1" на инверсном выходе эле:— мента ИСКЛЮЧАЮЩЕЕ ИЛИ 31 запрещает поступление тактовых импульсов через элемент ИЛИ-НЕ 35 на тактовый вход первого делителя 5 частоты (сигнал

C1). !

Счет второго 6 и третьего 11 делителей частоты производится до появления на их выходах уровня логической

1I II

1 при переполнении внутренних счетчиков указанных делителей частоты .

Так как счет делителей осуществляется по отрицательным фронтам тактовых импульсов с задающего генератора

1 (за счет инверсии на элементах ИЛИНЕ 33 — 3 5 ), то при возникновении

1569994 уровня логической "1" на выходах делителей 6 и 11 по следующему положи тельному фронту тактовых импульсов этот сигнал с входа блока 12 управлеяия появляется на прямом выходе триггера 21 (сигнал Х2, фиг. 3). На вы ходе триггера 18 сохраняется уровень логического "0", сигнала Х1 так как он удерживается в этом состоянии еди, ничным уровнем на установочном входе ! ,К. Сигнал Х2 формирует уровень логи ческой "1" на выходе элемента ИЛИ 26, (разр.сч. -3, фиг.3), а тот, в свою ,, очередь, формирует уровень логическо;го "0" на инверсном выходе элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ 31.

При этом разрешается прохождение ,тактовых импульсов с входа блока 12, управления через элементы ИЛИ-НЕ 33 и

35 и запрещается через элемент ИЛИ-НЕ

55 34„ Поэтому на выходе третьего дели;теля 11 частоты поддерживается высо кий уровень, первый делитель 5 начинает, а второй 6 продолжает с нуля

"чет счетных импульсов с выходов блока 12 управления. Этот счет продолжается до выравнивания кодов на выходах

ao" блока .12 управления возникает уровень логической " 1" (a=b, фиг. 3),,который, появившись на прямом выходе (а=Ь) триггера 16 по очередному поI ложительному фронту тактовых импульсов с выхода генератора 1, запрещает прохождение этих импульсов на счетные входа всех делителей частоты через элементы ИЛИ-НЕ 33 — 35 из-за формирования сигнала логической "I" на выходах элементов ИЛИ 29 и 26, а псом и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 31.

Работу блока 12 управления с этого момента времени можно проследить по временным диаграммам (фиг, 4).

Формула изобретения

1. Масштабный преобразователь кодов, содержащий генератор импульсов, входной и выходной счетчики, первый и второй делители частоты, управляющие входы которых являются входами установки масштабных коэффициентов входного и выходного счетчиков соответственно„ выход первого делителя частоты соединен со счетным входом входного счетчика, вход сброса которого соединен с входами сброса первого и втовходного регистра 2 и первого счетчи- ка 3. При этом на входе признака "Pasl2 рого делителей частоты и выходного счетчика, выход которого является выходом преобразователя, о т л и ч а юшийся тем, что, с целью повышения быстродействия и достоверности, в него введены схема сравнения, третий делитель частоты, блок управления и входной регистр, информационный вход которого является информационным входом преобразователя, вход начальной установки которого соединен с входом начальной установки блока управления и входом сброса входного регистра, синхровход которого соединен с выходом приема блока управления, входы признаков "Больше", "Равно" и

"Меньше" которого соединены с соответствующими выходами схемы сравнения, первый и второй входы которой соединены соответственно с выходами входного регистра и входного счетчика, вход направления счета которого соединен с выходом управления счетом блока управления и входом направления счета выходного счетчика, счетный вход которого соединен с выходом счетных импульсов блока управления, выход сброса которого соединен с входами сброса входного счетчика и третьего делителя частоты, информационный вход которого соединен с входом установки масштабного коэффициента второго счетчика, вход записи преобразователя соединен с входом записи блока управления, выходы первой, второй и третьей серий импульсов которого соединены соответственно с тактовыми входами первого, второго и третьего делителей частоты, выходы второго и третьего делителей частоты соединены с первым и вторым входами пересчетных импульсов блока управления, тактовый вход которого соединен с выходом генератора импульсов.

2, Преобразователь по п. 1, о т— л и ч а ю шийся тем, что блок управления содержит шесть D-триггеров, четыре элемента И, пять элементов

И1Я, RS-триггер, элемент ИСКЛЮЧАЮЩЕЕ

ИЛИ, первый, второй и третий элементы ИЛИ-НЕ, выходы кбторых являются соответственно выходами первой, второй и третьей серии импульсов блока управления, выход сброса которого соединен с выходом первого элемента ИЛИ, первым входом второго элемента ИЛИ и

S-входом первого D-триггера, прямой выход которого соединен с К-входом

1569994

14 второго триггера и первым входом первого элемента И, второй вход которого соединен с прямым. выходом третьего D-триггера и первым входом третье5 го элемента ИЛИ, второй вход которого соединен с прямым выходом четвертого триггера и первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом второго триггера и первым входом второго элемента

И, второй вход которого соединен с инверсным выходом первого триггера и

К-входом третьего D-триггера, D-вход которого является вторым входом пересчетных импульсов блока управления и соединен с первым входом третьего элемента И, второй вход которого соединен с инверсным выходом RS-триггера, выход которого является выходом управления ечета блока управления и соединен с первым входом четвертого элемента И,второй вход которого является первым входом пересчетных импульсов блока управления и соединен с 25

D-входом второго триггера, С-вход которого соединен с тактовым входом блока управления и с С-входами третье го, четвертого, пятого и шестого Dтриггеров и первыми входами первого, второго и третьего элементов ИЛИ-НЕ, вторые входы которых соединены соответственно с выходами элемента ИСКЛЮЧИ)ЦЕЕ ИЛИ, третьего и четвертого элементов ИЛИ, соединенных с входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход первого элемента И соединен с вторым входом второго элемента ИЛИ, выход которого соединен с S-входами RS-триггера, R-вход которого соединен с выходом второго элемента И, выходы третьего и четвертого элементов И соединены с входами пятого элемента ИЛИ, выход второго является выходом счетных им"пульсов блока управления, входы приз наков "Меньше"1",Равно",и "Больше" которого соединены соответственно с

D-входами пятого, четвертого и первого D-триггеров, С-вход которого соединен с инверсньпч выходом шестого

D-триггера, прямой выход которого является выходом приема блока управления и соединен с R-входом пятого D-.. триггера, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого является входом начальной установки блока управления. вход записи которого соединен с R-вх.. дом шестого D-триггера, D-вход которого соединен с входом признака . Рав-.

11 но" блока управления.

1569994

«grp. й

Редактор М. Бпанар

Заказ 1458 Тираж б60 Подписное

ВНИИПИ Государственного комитета по изобретениям и открьггиям при ГКНТ СССР

113035, Москва, Ж 35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101

JN сфюс аЬ

aigZ аЬ

5ort сш

ШР .СО

Мпла.

cr сг и

ЬЬЯ фвЬ

Эдй

) 8J фьЬ (e>8)

С7 сс сю гис

ШЮ и

«с

М. с

t с с

t

t с с

t

t

t

t

t с

Составитель М. Аршавский

Техред И. Дидык Корректор М. Максимишинец