Устройство для подсчета числа единиц двоичного кода

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике. Его использование в системах обработки и передачи цифровой информации позволяет повысить быстродействие. Устройство содержит генератор тактовых импульсов, многоканальный преобразователь параллельного кода в последовательности импульсов, триггер, два элемента ИЛИ, элемент И, счетчик импульсов, блоки подсчета единиц, две группы элементов И, группу элементов ИЛИ. Благодаря введению группы элементов И и группы элементов ИЛИ в устройстве обеспечивается более быстрый, чем в прототипе, подсчет как числа единиц входного кода, так и того же числа по модулю К. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (Si)S Н 03 М 7/20

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К A ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21 ) 4340296/24-24 (22) 08. 12.. 87 (46) 07 ° 06.90. Бюл. № 21 (72) О.н. музыченко (53) 681 325(088.8) .(56) Авторское свидетельство СССР № 1357960, кл. G 06 F 11/10, 1983 °

Авторское свидетельство СССР по заявке ¹ 4250845, кл. Н 03 М 7/20, 1987, (54) УСТРОЙСТВО ДЛЯ ПОДСЧЕТА ЧИСЛА

ЕДИНИЦ ДВОИЧНОГО КОДА (57) Изобретение относится к вычислительной технике ° Его использование в

Изобретение относится к вычислительной технике и может быть использовано в системах обработки и передачи цифровой информации.

Цель изобретения — повышение быстродействия.

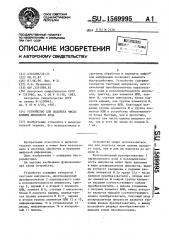

На чертеже изображена функциональная схема устройства °

Устройство содержит генератор 1 тактовых импульсов, многоканальный преобразователь 2 параллельного кода в последовательности импульсов, триггер 3, первый 4 и второй 5 элементы

ИЛИ, элемент И 6, счетчик 7 импульсов, блоки 8 подсчета единиц, первая-третья группы элементов И 9-11, первая и вторая группы элементов ИЛИ 12 и 13, информационные 14 и установочные 15 входы, информационные 16 и контроль;ный 17 выходы.

„.,SU„„1569995 A I

2 сис темах обработки и передачи цифровой информации позволяет повысить быстродействие. Устройство содержит генератор тактовых импульсов, многоканальный преобразователь параллельного кода в последовательности импуль,— сов, триггер, два элемента ИЛИ, элемент И, счетчик импульсов, блоки подсчета единиц, две группы элементов И, группу элементов ИЛИ. Благодаря введению группы элементов И и группы элементов ИЛИ в устройстве обеспечивается более быстрый, чем в прототипе, подсчет как числа единиц входного кода, так и того же числа по модулю К.

1 ил.

Устройство может использоваться . как для подсчета числа единиц входного кода, так и для их подсчета по модулю К. Яд.

Многоканальный преобразователь 2 м параллельного кода в последовательность импульсов может быть выполнен р в виде распределителя импульсов, выходы которого соединены с первыми входами элементов И 2р групп (2 р — число каналов преобразователя), вторые входы элементов И каждой группы являются входами соответствующего канала преобразователя, а выходы соединены с входами элемента ИЛИ, выход которо- 3 го является выходом соответствующего аеас канала преобразователя, тактовый вход распределителя импульсов является тактовым входом преобразователя, а выход последнего разряда преобразователя— выходом конца преобразования.

1569995

Многоканальный преобразователь 2 параллельного кода в последовательность импульсов может быть также выполнен в виде 2р регистров сдвига, соединенных информационными входами

5 с информационными входами преобразователя, тактовыми входами — с тактовым входом преобразователя, а выходами переноса — с выходами каналов пре1О образователя, инверсные выходы каждого регистра сдвига соединены с входами своего элемента И, а выходы последних — с входами элемента И, выход которого является выходом конца преобразования, входы разрешения записи регистров сдвига соединены с входом разрешения записи преобразователя.

Триггер 3 выполняется в виде RSтриггера или в виде счетного тригге- 20 ра, в зависимости от выполнения многоканального преобразователя 2. Для второго из описанных вариантов реализации преобразователя 2 он выполняется в виде КБ-триггера, а для пеРвого 25 варианта — в виде RS-триггера или счетного триггера в зависимости от того, синхронизирован импульс на выходе конца преобразования преобразователя 2 с паузой между тактовыми им- 0 пульсами или с тактовым импульсом.

При работе в режиме подсчета количества единиц счетчик 7 и блоки 8 подсчета единиц выполняются следующим образом.

Счетчик 7 выполняется в виде реверсивного двоичного счетчика с двумя счетными входами на )log (и+1) ,разрядов, где и — Разрядность входного кода.

Блок 8 подсчета единиц выполняется в виде реверсивного двоичного счетчика с коэффициентом пересчета, равным

r r,è;,:,+ и+ „,, где n;... и „„- число входов соответствующей группы, число разрядов которого равно

flog (и;„+ n,„,+ 1) Р, i=1,р-1, вычитающий и суммирующий счетные входы счетчика являются соответственно первым и вторым входами блока, и двух пороговых блоков, а также элемента И.

Первый пороговый блок соединен входами с прямыми выходами реверсивного счетчика, имеет веса входов 2 и поО рог А < m,, а втор и пороговый блок I соединен входами с инверсными выходами реверсивного счетчика, имеет веса выходов, равные 2, и порог A=2 -m ..+ . 0(+ 1, где оптимальное значение

1Г Г и . +Il y+ иl 1 п + +па+ (- Г

Элемент И соединен входами с прямыми выходами разрядов реверсивного счетчика с номерами, равными номерам единичных разрядов в двоичном представлении числа (m -1), инверсными выходами остальных разрядов счетчика.

Выход элемента И является первым выходом блока, выход первого порогового блока — вторым выходом блока, а выход второго порогового блока — третьим выходом блока. В исходном состоянии в счетчик блока 8 записан код числа п,;, информационных входов 14,.; „ группы преобразователя 2.

При работе в режиме подсчета количества единиц по модулю К счетчик 7 и блоки 8 подсчета единиц выполняются следующим образом.

Счетчик 7 выполняется в виде реверсивного двоичного счетчика по модулю К с двумя счетными входами на

)log (К+1)C разрядов.

Ълок 8 подсчета единиц выполняется аналогичным описанному. Он содержит реверсивный счетчик по модулю К, два . пороговых блока и элемент И. Разрядность счетчика равна t=j log (К+1) .

Пороговые блоки реализуют пороговые функции с весами входов 2 и порогами А = m и А=2 -г +1 соответствен1

"> но, где оптимальное значение ш . g 1-,), ) — (+1 ). Первый пороговый

1 блок соединен входами с прямыми выходами разрядов счетчика, второй порого= вый блок - с инверсными. Элемент И соединен входами с прямыми выходами разрядов счетчика с номерами, равными номерам единичных разрядов в двоичном представлении числа (m-, 1), и инверсными выходами остальнй» разрн дов счетчика. Выход элемента И и выходы первого и второго пороговых блоков являются соответственно первым, вторым и третьим выходами блока 8 подсчета единиц.

В исходном состоянии в счетчик.. блока 8 записывается код :.числа (г. р ) mod К = д путем подачи сигнала сброса на прямые установочные входы триггеров разрядов, счетчика с номерами, равными номерам единичных разрядов двоичного представления числа, и инверсные установочные входы остальных разрядов (входы 15;).

156999

Функционирование устройства в ре жиме подсчета количества единиц происходит следующим образом.

В исходном состоянии счетчик 7, блоки 8 подсчета единиц, многоканальный преобразователь 2 параллельного кода в последовательность импульсов и триггер 3 сброшены.

На выходе триггера 3 нулевой логический сигнал, запрещающий прохожде-. ние тактовых импульсов через группы элементов И 9 и 10. На информационные входы 14 устройства подан входной код, причем на входы групп 14 — 14 он подан в прямом виде, а на входы групп

14 — 14 — в инверсном либо в пряps 2р мом, но инвертируется устанавливаемыми на входах инверторами, либо выполнением соответствующих входов преоб- 20 разователя 2 инверсными.

В .счетчик 7 в исходном состоянии с входов 15 Р записан код числа р t

С = и „+,» (m;-1). 25 ! $

В счетчик блока 8; подсчета единиц (i=1, р-1) в исходном состоянии со входов 15; записан код числа

С

При выполнении многоканального преобразователя 2 на регистрах сдвига входной код записан в них.

При поступлении тактовых импульсов с выхода генератора 1 на тактовый вход З5 многоканального преобразователя 2 последний преобразует количество единиц входного кода на входах 14 в соответствующее количество импульсов на его 1-м выходе (1=1,...,р) и коли- . 40 чество нулей входного кода на входах

14 (Р+ e) в соответствующее количество импульсов на (р+1)-м выходе.

Импульсы с первого и (р+1)-го выходов многоканального преобразователя 45

2 поступают через .элементы ИЛИ 4 и 5 на соответствующие входы элементов И

112, и 11 . Если импульс поступает только с одного элемента ИЛИ 4, то он поступает на суммирующий вход счетчи- 50 ка 7, к содержимому которого при этом прибавляется единица. Если импульс поступает только с одного элемента

ИЛИ 5, то он поступает на вычитающий вход счетчика 7,от содержимого которо- 55 го при этом вычитается единица. Если импульсы поступают одновременно с обоих элементов ИЛИ 4 и 5, то импульсы на входы счетчика не поступают.

5 б

Импульсы с 1-го и (р+1)-ro выходов многоканального преобразователя 2 поступают на соответствующие пары элементов И 11, которые работают так же, как описано.

Работа продолжается таким образом до окончания опроса входного кода преобразователем 2, для чего требуется

)п/2р Г тактов. При этом многоканальный преобразователь 2 самоблокируется и далее импульсов на информационных выходах не формирует, а на его выходе окончания работы появляется импульс,, переключающий триггер 3, на выходе к;;торого при этом появляется единичный сигнал, разрешающий прохождение тактовых импульсов через группы элементов

И 9 и 10.

В результате к моменту окончания работы многоканального преобразователя 2 в блоке 8 подсчета единиц оказывается записан код числа единиц контролируемого кода на группах 14.

isa и 14,;+„ а в счетчике 7 — код числа р-с

S = W + y (m.-1), i-1 где W — число единиц контролируемого

1 кода на входах 14 и 14Р+ .

Все блоки подсчета единиц оказываются разбиты на две подгруппы. В первой подгруппе блоков 8 в их счетI чики записан код числа q . .) m . и на

1 1 их втором выходе имеется единичный сигнал, а на третьем — нулевой. Во второй подгруппе блоков 8 в счетчики записан код числа q > c п „-1 и на их третьем выходе имеется единичный сигнал, а на втором — нулевой.

Далее в каждой из указанных подгрупп последовательн9, а в обоих: группах одновременно происходит процесс пересчета содержимого блоков 8 подсчета единиц в счетчик 7 путем приведения каждого из блоков 8;в состояние, при котором в его счетчик записан код числа m.— 1.

Пусть 8. наименьший номер блока.

1 подсчета единиц первой подгруппы. На

его втором выходе — единичный сигнал, поступающий на вход элемента И 10;, на инверсных входах которого, соединенных с вторыми выходами блоков 8—

8 ., — нулевые сигналы, что разрешает прохождение тактовых импульсов на выход элемента И 10 . Импульсы с выi хода последнего поступают через элемент ИЛИ 4 на соответствующие входы элементов И 11 2Р и 11ЯР,а та *е на

1569995 оответствующие входы элементов И 11.

11 ;,, проходя при этом через элеент ИЛИ 12, на вычитающий вход блоа 8 . подсчета единиц от содержимо1

Э

5 о которого при этом каждый раз отмается единица. Работа продолжаетя таким образом до .появления в счетике блока 8. кода числа:m-1. . При

I том на втором и третьем выходах бло- 10 а 8. появляются нулевые сигналы, а

1 а его первом выходе — единичный. В ечение всего времени работы блока 8

1 одсчета единиц он единичным сигналом а своем втором выходе запрещает ripo- 1 ождение тактовых импульсов на выходы лементов И 10;,, — 10

Пусть 8 наименьший номер блока . одсчета единиц второй подгруппы. На

ro втором выходе — нулевой сигнал, à 20 а третьем — единичный, поступающий а вход элемента И 9, на инверсных ходах которого, соединенных с третьии выходами блоков 8 — 8 1, нулевые игналы, что разрешает прохождение 25 .га;<товЫх импульсов на вход элемента

И 9 . Импульсы с выхода последнего поступают через элемент ИЛИ 5 на со:ответствующие входы элементов 11 .,,:и 11, а также на соответствующие щ входы элементов 11, и 11p+gi проодя через элемент ИЛИ 13 1„ на суммирующий вход блока 81, к содержимому которого при этом прибавляется едини.-. ца. Работа продолжается таким образом до появления в счетчике блока 81 кода числа m - 1. При этом на его втором и третьем выходах имеются нулевые сигналы, а на первом — единичный.В течение всего времени работы блока 8 .одсчета ециниц он единичным сигналом на своем третьем выходе запрещает про..хождение тактовых импульсов на выходы элементов И 9 1„„- 9, Пока происходит процесс пересчета 45 содержимого блоков подсчета единиц в обеих группах, тактовые импульсы проходят на оба элемента 11, и 11 р и на их выходах импульсы не формируют- . ся. Далее в зависимости от того, какая из подгрупп блоков 8 первой возвращается в состояние, при котором в их счетчики записан код числа m .. -— 1, а тактовые импульсы проходят на выход либо первого, либо второго из указанных элементов И 11, при этом они поступают на суммирующий нли вычитающий входы счетчика 7 соответственно. Работа происходит таким образом до приведения всех блоков 8, подсчета единиц

I в состояние, при котором в их счетчики записан код числа m .. -— 1, при этом на первых выходах всех блоков 8 оказываются единичные сигналы, что вызывает единичный сигнал на выходе элемента И 6„, являющемся выходом 17 конца контроля устройства. Результат (код числа единиц входного кода) снимается с выходов 16 счетчика 7.

Функционирование устройства в режиме подсчета количества единиц двоичного кода по модулю К осуществляется в том же порядке, как описано. Разница заключается в том, что с входов

15 в исходном состоянии в счетчик 7 записывается код числа

p-!

С =(и +, + g (ш-.1))modK,, 1 1 а в счетчики блоков 8. подсчета еди1 ниц в исходном состоянии записывается код.числа (и ;+,)modK.

В процессе. функционирования подсчет числа импульсов, поступающих на входы счетчика 7 и блоков подсчета единиц, осуществляется по-модулю К.

В остальном порядок функционирования сохраняется.

Возможен несколько иной порядок функционирования предлагаемого устройства, когда при пересчете в счетчик

7 содержимого блоков 8 подсчета единиц пРоизводится обнуление счетчиков этих блоков, а не приведение в состояние, когда в счетчик блока 8. записан

1 код числю ш-1. При этом несколько изменяется выполнение блока 8; . в него вводится дополнительный элемент И, соединяемый прямым входом с выходом второго порогового блока инверсным входом с выходом первого элемента И, причем выбирается для первого порогового блока А=в,, а для второго А =

=2-m;.

Выход первого элемента И является р-рвым-выходом блока 8 подсчета единиц, выход второго элемента И - его вторым выходом, а выход первого порогового блока — третьим выходом. Первый элемент И блока подсчета единиц соединяется входами с инверсньии выходами разрядов счетчика блока 8,фиксируя нахождение счетчика блока 8 в нулевом состоянии.

1569995 цроцесс функционирования устройства происходит в порядке, аналогичном описанному. Разница заключается в том, что если по окончании работы многоканального преобразователя 2 в

5 счетчик блока 8 ; оказывается записан код числа q с m,, то пересчет его содержимого осуществляется путем последовательного вычитания единиц из счет- 0 счетчика в блоке 8. до его обнуле-.

1 ния. Если q y m., та пересчет осуществляется последовательным прибавлением единиц к содержимому счетчика в блоке 8 . до его переполнения.и о6- 15

1 нуления, причем С p=(n p+>)modK.

Формула изобретения

Устройство для подсчета числа единиц двоичного кода содержащее 20 многоканальный преобразователь параллельного кода в -последовательности импульсов, 2р групп информационных вхо",ов которого являются соответствующими информационными входами устройства, 25 счетчик импульсов, выходы которого являются информационными выходами устройства, первый — (р-1)-й блоки подсчета единиц, первые выходы которых соединены с соответствующими входами элемента И, выход которого является

KoHTpoJIbHbM выходом устройства, второй выход i-ro блока подсчета единиц (i=1, р-1) подключен к первому прямому входу i-ro элемента И первой группы, выход которого соединен с

i-м входом первого элемента ИЛИ и первым входом i-ro элемента ИЛИ первой группы, выход которого подключен к первому счетному входу 1-го блока .подсчета единиц, третий выход которо40 го соединен с первым прямым входом

i-го элемента И второй группы, выход которого подключен к i-.ìó входу второго элемента ИЛИ, генератор тактовых импульсов, выход которого:.соединен с

45 вторыми прямыми входами всех элементов

И первой и второй групп и тактовым входом многоканального преобразователя параллельного кода в последовательности импульсов, выход окончания рабо50 ты которого подключен к входу триггера, выход которого соединен с третьими прямыми входами всех элементов И первой и второй групп и р-м входом элемента И, первый информационный выход многоканального преобразователя параллельнога кода в последовательности импульсов подключен к р-му входу первого элемента ИЛИ, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия, в устройство введены третья группа элементов И и вто-. рая группа элементов ИЛИ, первый вх ..g и выход i-ro элемента ИЛИ второй гр,:.-. пы подключены соответственна к вых::.„-, i-го элемента И второй группы и второму счетному входу i-ro блока подсчет."-. единиц, установочные входы которого являются i-ми установочными входамн устройства, i-e инверсные входы j-x элементов И (i (j (р) первой и второй групп подключены соответственно к а-;,:-рым и третьим выходам i-ro блока подсчета единиц, (i+1)-й информационн .:: выход многоканального преобразовател-. параллельного кода в последовательн, ти импульсов соединен с прямым входо,i-го и инверсным входом (p+i-1)-го элементов И третьей группы, выходы которых подключены к вторым входам i-x .элементов ИЛИ соответственно первой и второй групп, (р+1)-й информационный выход многоканального преобразователя параллельного кода в последовательности импульсов соединен с р-м входом второго элемента ИЛИ, (p+i+1)-й информационный выход многоканального преобразователя параллельного кода в последовательности импульсов подключен к инверсному входу i-га и прямому входу (p+i-1)-го элементов И третьей группы, выходы первого и второго элементов ИЛИ подключены соответственна. к прямому входу (2р-1)-го и инверсно-му входу 2р-ro элементов. И третьей группы и к инверсному входу (2р-1)-го и прямому входу 2р-го элементов И третьей группы, выходы которых соединены соответственно с первым и вторым счетными входами счетчика импульсов, установочные входы которого являются р-ми установочными входами устройства.

1569995

Редактор М. Бланар

Заказ 1458 Тираж 659 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям лри ГКНТ СССР

11303S, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101 ри

14r

Н2

Ир+д

/ар) и .g

Составитель О, Ревинский

Техред M. Дидык Корректор В- Кабаций