Устройство для приема относительного биимпульсного сигнала

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи и может использоваться в цифровых системах передачи информации. Цель изобретения - повышение помехоустойчивости при наличии дроблений принимаемого сигнала. Для достижения указанной цели дешифратор 5 сигнала выполнен в виде трех логических блоков 7 - 9, блока 10 декодирования информации, блока 11 памяти и формирователя 12 импульсов фазирования. Блок 10 деподирования дешифратора 5 сигнала вырабатывает на первом своем выходе сигнал, определяющий зону переходов сигнала, на втором выходе - декодированный сигнал, а на третьем выходе - сигнал ошибки. Эффективность подавления дроблений увеличивается с увеличением частоты опорного колебания, поступающего на вход блока 11 памяти. 2 ил.

СОЮЗ С08ЕТСННХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

09) (f));

Al (5) ) 5 Н 04 L 5/14.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ (54) УСТРОЙСТВО ДЛЯ ПРИЕМА ОТНОСИТЕЛЬНОГО БИИМПУЛЬСНОГО СИГНАЛА (57) Изобретение относится к электросвязи и может использоваться в цифровых системах передачи информации.

Цель изобретения — повышение помехоус тойчивости при наличии дроблений при-.

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

r)g ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

f (2) ) 4407147/24-09 (22) 11.04.88 ,(46) 07.06.90. Бюл,, ¹ 21 (72) А.,Г.Бригинский, С.M.Первушкин и B„A.Титков (53) 621 . 394. 62 (088, 8) (56) Авторское свидетельство СССР № ) 425863, кл. Н 04 ). 5/14, 1987.

7 нимаемого сигнала. Для достижения указанной цели дешифратор 5;.сигнала выполнен в виде трех логических блоков

7-9, блока 10 декодирования.информации, блока 11 памяти и формирователя

12 импульсов фазирования. Блок 10 деподирования дешифратора 5 сигнала вырабатывает на первом своем выходе сигнал, определяющий зону переходов сигнала, на втором выходе — декодированный сигнал, а на третьем выходе — сигнал ошибки.: Эффективность подавления дроблений увеличивается с увеличением частоты опорного колебания, поступающего на вход блока 11 памяти. 1 з.п, ф-лы, 2 ил.

ИкЦВЯЯЦУОЯ4ыВ Й66Ь

1570013

Изобретение относится к электросвязи и может использоваться в цифровых системах передачи информации.

Цель изобретения - повышение поме5 хоустойчивости при наличии дроблений принимаемого сигнала.

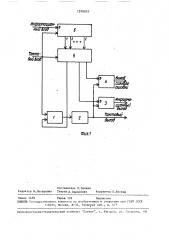

На фиг.1 изображена структурная электрическая схеиа устройства для приема относительного биимпульсного сигнала; на фиг.2 - структурная элен трическая схема дешифратора сигнала, входящего в .состав устройства, Устройство для приема, относительного биимпульсного сигнала содержит выделитель 1 импульсов, делитель .2 частоты, первый 3 и второй 4 триггеры, дешифратор. 5 сигнала и регистр

6 сдвига. Дешифратор 5 сигнала (фиг.2), содержит первь1й-третий логические бло-20 ки 7-9, блок 10 декодирования информации, блок 11 памяти и формирователь 12 импульсов фазирования, Устройство работает следующим об разом, 25

Входной сигнал поступает на ин*формационный вход. регистра б сдвига, на тактовый вход котррого и тактовые входы дешифратора 5 сигнала и выделителя 1 импульсов поступает опорная тактовая последовательность с частотой следования импульсов

Кб = 2пйс у где f с — частота следования информаци-35 онных посылок; целое четное число.

Число ячеек регистра 6 сдвига должно быть таково, чтобы обеспечивалась запись в него трех последовательных посылок относительного биимпульсного сигнала, Выделитель 1 импульсов, работающий в режиме деления частоты, вырабатывает на своем выходе тактовую последовательность, соответствующую удвоенной частоте следования посылок входного сигнала.

Делитель 2 частоты имеет коэффициент деления, равный двум, и сигнал с его выхода поступает на тактовые входы первого и второго триггера 3 и 4, на информационные входы которых с первого и второго выходов дешифратора. 5 сигнала поступают соответственно сиг55 нал ошибки и информационный сигнал.

Синхронизация выделителя 1 импуль. сов осуществляется через его управляющий вход сигналами, вырабатываемыми на третьем выкоде дешифратора 5 сигнала, Рассмотрим работу дилифратора 5 сигйала для случая п=8. Каждый из трех логических блоков 7"9 имеет в этом случае восемь входов и два выхода и производит анализ (усреднение) элементарной посылки длительностью

1 — поступающей в виде восьми

2 с дискретных отсчетов. 1Три этом сигналы на выходах логических блоков форми руются по следующему правилу (0при а, с а

f1 если а„= а,;

i (Оеслиa„Фаб,у где а„; - количество дискретных отсчетов .на входе i-го логического блока, равных логической "1";

a ; — количество дискретных отсчетов на входе i-го логического блока, равных логическому "0". а„+а; =n=-8 усредненные значения трех последовательных посылок поступают на блок 10 декодирования информации, имеющий шесть входов и три выхода, цричем на первом выходе вырабатывается сигнал, определяющий зону переходов фазы относительного биимпульсного сигнала, на втором выходе — декодированный сигнал, а третьем выходе — сигнал ошибки. Логические функции, связывающие входные и выходные сигналы блока декодирования информации, имеют вид

F,=(А А +А A>+A, А ) В, В .m, (А А A +A Аг A3) B, B B 1

Р =(А, А,. А +А,. А -А ) (В +В +Вз), Сигнал с первого выхода блока 10 декодирования информации поступает на вход блока 11 памяти, выполненного в виде регистра сдвига, тактируемого опорной тактовой последовательностью. Сигналы с выходов блока 11 памяти поступают на входы формирователя 12 импульсов фазирования, выхоцной сигнал которого определяется в соответствии с логической функцией

F C,C C C C C C +C„C C C C C С +

+Сt С С С С С7С +С1Г С C5C С. Сg, 1. Устройство для приема относительного биимпульсного сигнала, содержащее выделитель импульсов, делитель частоты, первый и второй триггеры, дешифратор сигнала и .регистр сдвига, выходы которого соединены с сигнальными вкодами дешифратора сигнала, первый выход которого соединен с информационным входом первого триггера., при этом выход делителя частоты подключен к тактовому входу второго триггера и является тактовым выходом устройства, информационным выходом которого является выход второго триггера, о т л и ч а ю щ е е с я тем, что, с целью повьппения помехоустойчивости при наличии дроблений принимаемого сигнала, второй и третий выходы дешифратора сигнала соединены соответственно с информационным входом второго триггера и управляющим входом выделителя импульсов, тактовьй вход которого соединен с тактовыми входами дешифратора сигнала и регистра сдвига и является тактовым входом устройства, инфсрмационным входом и сигнальным выходом которого являются соответственно информационный . вход регистра сдвига и выход первого триггера, тактовый вход которого подключен к выходу делителя частоты, вход которого соединен с выходом выделителя импульсов, ?. Устройство по и„ 1, о т л и ч аю щ е е с я тем, что дешифратор сигнала содержит три логических блока, блок декодирования информации, блок памяти и формирователь импульсов фазирования, выход которого является третьим выходом дешифратора сигнала, сигнальными и тактовым входами которого являются соответствующие входы логических блоков и тактовый вход блока памяти, выходы и сигнальный вход которого соединены с нходами Аормирователя импульсов фазирования и пер" вым выходом блока декодирования информации, входы которого подключены к соответствующим выходам логических блоков, при этом первым и вторым выходами дешифратора сигнала являются второй и третий выходы блока декодирования информации, 5 .1 5700 где С вЂ” сигнал на выходе j-й ячейки

J блока 11 памяти, Импульс на выходе формирователя

12 импульсон фазирования оказывается задержанным относительно середины зоны фазовых переходов на время, равное половине длительности элементарной по-. сылки входного сигнала, При этом длительность эоны фазовых переходов меняется в зависимости от интенсивности дроблений и величины краевых искажений нходного сигнала, но ее середина совпадает по времени с иатематическим ожиданием момента фазового перехода относительного биимпульсного сигнала, приведенные алгоритмы (логические уравнения) формирования сигналов осно- р(1 наны на свойствах относипельного биимпульсного сигнала, а именно наличии обязательного перехода в середине каждого тактового интервала- и наличии дополнительного. перехода в на- 25 чале тактового интервала в случае передачи логической "1". Формирование сигнала ошибки происходит либо в случае отсутствия входного сигнала, либо в случае не предусмотренного для данного сигнала порядка чередования переходов, Данное устройство обеспечивает одновременно и малое время вхбждения в синхронизм. Импульс фазировки выделителя 1 импульсов вырабатывается пос.35 ле правильного прием; трех последовательных элементов сигнала, е

Для нормальной работы устройства максимальная относительная рас- 4Q стройка частоты сигнала и опорной тактовой последовательности должна быть

Такова, чтобы за время прохождения сигнала по регистру 6 сдвига временная ошибка, вызванная асинхронностью, 45 частот, не превышала один период опорной тактовой последовательности, что легко обеспечить использованием

- генераторов, стабилизируемых кнарцевыми резонаторами. Конкретная реа- 50 лизация блоков дешифратора 5 сигнала определяется выбираемой элементной базой и приводимыми выше уравнениями.

Применение предлагаемого устройства эффективно при использовании кана лов связи, подверженных дроблениям пе-. редаваемых сигналов и по мере увеличения интенсивности дроблений следует

13 6 унеличинать частоту опорного колебания, т,е, число h, Формула изобретения

1570013

Составитель В,Зенкин

Редактор Н,Лазаренко Техред Л,Сердюкова Корректор Л.Бескид

Заказ !459 Тираж 529 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, уп. Гагарина, 101