Дифференциальный импульсный кодер телевизионного сигнала

Иллюстрации

Показать всеРеферат

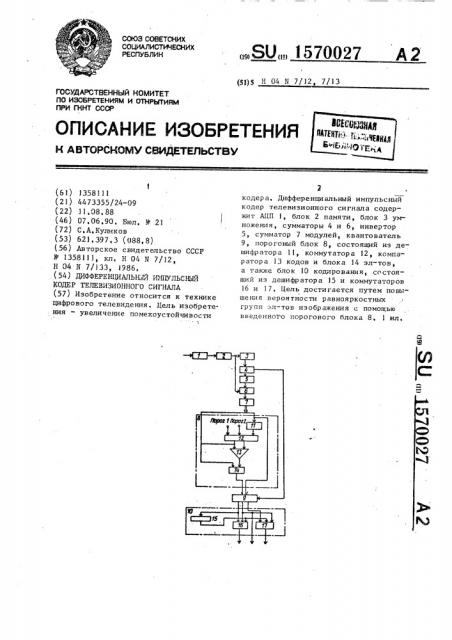

Изобретение относится к технике цифрового телевидения. Цель изобретения - увеличение помехоустойчивости кодера. Дифференциальный импульсный кодер телевизионного сигнала содержит АЦП 1, блок 2 памяти, блок 3 умножения, сумматоры 4 и 6, инвертор 5, сумматор 7 модулей, квантователь 9, пороговый блок 8, состоящий из дешифратора 11, коммутатора 12, компаратора 13 кодов и блока 14 эл-тов И, а также блок 10 кодирования, состоящий из дешифратора 15 и коммутаторов 16 и 17. Цель достигается путем повышения вероятности равнояркостных групп эл-тов изображения с помощью введенного порогового блока 8. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

А2

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (61) 1358111 (21) 4473355/24-09 (22) 11,08,88 (46) 07.06.90. Бюл, У 21 (72) С.А.Куликов (53) 621,397,3 (088.8) (56) Авторское свидетельство СССР

11 1358111, кл, Н 04 N 7/12, Н 04 0 7/133, 1986. (54) ДИФФЕРЕНЦИАЛЬКЙ ИМПУЛЬСНЫЙ

КОДЕР ТЕЛЕВИЗИОННОГО СИГНАЛА (57) Изобретение относится к технике цифрового телевидения, Цель изобретения — увеличение помехоустойчивости

„„SU„„1570027 (У1)5 Н 04 N 7/12, 7/13

2 кодера, Дифференциальный импульсный кодер телевизионного сигнала содержит АЦП 1, блок 2 памяти, блок 3 умножения, сумматоры 4 и 6, инвертор

5, сумматор 7 модулей, квантователь

9, пороговый блок 8, состоящий из дешифратора 11, коммутатора !2, компаратора 13 кодов и блока 14 эл-тов, а также блок 10 кодирования, состоящий из дешифратора 15 и коммутаторов

16 и 17. Цель достигается путем повыше ля вероятности равнояркостных групп эл-тов изображе ыя с помощью введенного порогового блока 8. 1 ил.!

570027.

Изобретение относится х технике .цифрового телевидения, может быть использовано для уменьшения цифрового потока видеоданных с сохранением качества кодируемых изображений. и являS ется усовершенствованием изобретения по авт. св, У 1358111.

Целью изобретения является увеличение помехоустойчивости кодера путем повышегыя вероятности равнояркостных групп элементов изображения, На чертеже представлена электри ческая структурная схема дифференциального импульсного кодера телевизи- 5 он но го си гнал а, Дифференциальный импульсный кодер телевизионного (ТВ) сигнапа содержит аналогоцифровой преобразователь (АЦП) I, блок 2 памяти, блок 3 умножения, пер- вый сумматор 4, инвертор 5, второй сумматор 6, сумматор 7 модулей, пороговый блок 8, квантователь 9, блок

IO кодирования, при этом блок 8 со-. держит дешифратор 11, коммутатор 12, компаратор 13 кодов и блок 14 элемен25 тов И, а блок .10 кодирования содержит дешифратор 15, первый 16 и второй 17 коммутаторы, Устройство работает следующим образом, ЗО

В АЦП 1 исходный аналоговый сигнал преобразуется в цифровой поток, например, по методу ИКМ. В блоке 2 памяти благодаря задержке цифрового потока создается ряд цифровых пото- 35 ков, каждый из которых соответствует бдному из элементов многоэлементной апертуры — группе 4 соседних элементов ТВ изображения. После умножения каждого потока на весовой коэффици — ® ент 1/4 в блоке 3 эти потоки одновременно поступают в первый сумматор 4, где путем их суммирования вычисляют среднее: значение а, по кодируемой группе. Во втором сумматоре б из цифровых потоков многоэлементной аперту- . ры, поданных туда из блока 2 памяти, вычитается среднее значение а, поданное через инвертор 5, В сумматоре 7 модулей производится вычисление полусуммы модулей отклонений яркостей элементов от аг, а также матрицы знаков S.

Коды а и S поступают в пороговый блок 8, где производится пороговая обработка а, Четырехраэрядгый код S подается на вход дешифратора Il> с которого считывается одноразрядный код.

Сигнал с выхода дешифратора 11 является управляющим для коммутатора 12, на один сигнальный вход которого подается первое пороговое значение, на другой — второе, Если управляюций сигнал равен единице, к выходу коммутатора подключается меньшее из двух пороговых значений. Меньшее пороговое знач ние соответствует горизонтальным и вертикальным контурам, большее †наклонным контурам и линиям кодируемой группы 2 2, В компараторе 13 кодов сравниваются код а и код с выхода коммутатора 12. Если а< не больше порогового значения с выхода коммутатора 12, то сигнал на выходе компаратора 13 равен нулю, В блоке 14 производится умножение (поразрядное) восьмиразрядного кода а на сигнал с выхог да блока 13, т, е, если этот сигнал равен нулю, то код а обнуляется, Код а.< после пороговой обработки, код S и код а„поступают в квантова— тель 9, где осуществляется грубое равномерное квантование а и выравнивание а„, àz u S во времени, После квантовагия в квантователе

9 коды а,, а и S передаются в блок

iO кодирования, Код а поступает в дешифратор 15 сигнал на выходе котор рого ранен единице, если а =0 и на коммутаторе 16, на второй вход которого поступают пять разрядов Е сеьиразрядного кода а, — Е„Е Е,Е Е,Е Е7, где Š— ст арший р аз ряд, Сигнап с выхода дешифратора 15 является управляюцггм для коммутаторов 16 и 17. Если он равен единице, к выходу блока 16 вместо пятиразрядного кода а передается пять разрядов Е, т,е. все разряды а приравниваются к Е .

На один сигнальный вход коммутатора

17 поступают четыре разряда Е < кода а, на другой — четырехразрядный код

S. Если а = О, к выходу коммутатора

17 подключаются четыре р азряда Е т, е. все разряда S заменяются Е, . В противном случае, т, е. при a>g0, к выходу коммутатора 17 подключается код S. формула изобретения

Дифференциальный импульсный кодер телевизионного сигнала по авт, св. II"- 1358111, о т л и ч а ю щ и и с я. тем, что, с целью увеличегия помехоустойчивости кодера путем повышения вероятности равнояркостных групп элементов изображения„выход сумматора модулей соединен с дополнительным входом кван-.ования через введенный пороговый блок, содержащий дешифратор, 1570027

Составитель И. Грицианская

Техред Л.Сердюкова Корректор О,Циппе

Редактор Н,Лазаренко

Заказ 1460

Подписное

Тираж 538

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101 вход которого является входом порогового блока, а выход соединен с управ" ляющим входом коммутатора, первый и второй сигнальные входы которого являются входами первого и второго пороговых уровней, а выход коммутатора соединен с первым входом блока элементов И через первый вход компаратора кодов, к второму входу которого под5 . ключены вход дешифратора и второй вход блока элементов И, выход которого является выходом порогового блока,