Устройство для регистрации сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной технике. Цель изобретения - расширение частотного диапазона регистрируемых сигналов. Каждый импульс генератора 9 импульсов запускает формирователь 8 синхронизирующих импульсов, который вырабатывает последовательность импульсов. По импульсу на входе запуска аналого-цифровой преобразователь 1 преобразует в код сигнал, поступающий по входной шине 3. По импульсу на входе записи в блок 4 памяти заносится этот код. По импульсу на входе управления через двухканальный мультиплексор 12 на адресные входы блока 4 памяти подается модифицированный код адреса. Содержимое ячейки блока 4 памяти, адрес которой определяется этим модифицированным кодом адреса, по импульсу на первом входе стробирования дешифратора заносится в один из внутренних регистров цифроаналоговых преобразователей 5, выходные сигналы которых регистрируются блоком 6 регистрации. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (Si)S С 01 0 9/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ .К СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ HOMHTET

ПО ИЗОБРЕТЕНИЯМ И OTHPblTHRM

ПРИ ГКНТ СССР (21) 4634266/24-10 (22) 09.01.89 (46) 15.06.90. Бюл, М - 22 (71) Производственное объединение

"Краснодарский ЗИП" (72) Э,П.Васильев и О.Л.Карасинский (53) 621.317.7(088.8) (56) Авторское свидетельство СССР

Ф 1280323, кл. С Oi П 9/00, 1985.

Авторское свидетельство СССР

У 1323856, кл. С Ol D 9/00, 1986.,(54) УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ СИГНАЛОВ (57) Изобретение относится к измерительной технике. Цель изобретения— расширение частотного диапазона регистрируемых сигналов. Каждый импульс генератора 9 импульсов запускает формирователь 8 синхронизирующих импуль„.80„„1571397 А 1

2 сов, который вырабатывает последовательность импульсов. По импульсу на входе запуска аналого-цифровой преобразователь I преобразует в код сигнал, поступающий по входной шине 3.

По импульсу на входе записи в блок

4 памяти заносится этот код. По импульсу на входе управления через двухканальный мультиплексор 12 на адресные входы блока 4 памяти подается модифицированный код адреса. Содержимое ячейки блока 4 памяти, адрес которой определяется этим модифицированным кодом адреса, по импульсу на первом входе стробирования дешифратора заносится в один из внутренних регистров цифроаналоговых преобразователей 5, выходные сигналы которых регистрируются блоком 6 регистрации, 1 ил, 1571397

Изобретение относится к измерительной технике, а именно к устройствам для регистрации сигналов.

Цель изобретения — расширение

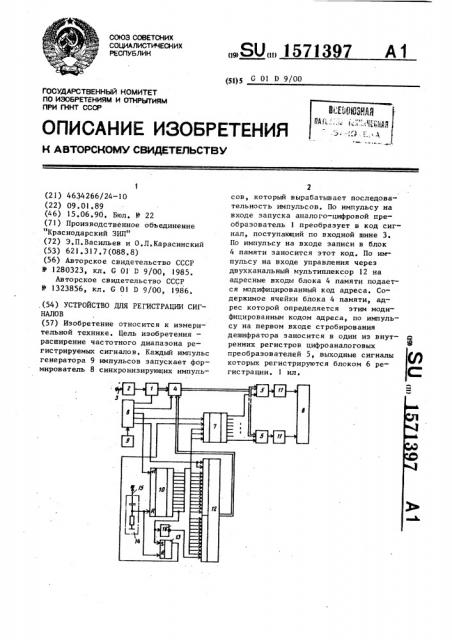

5 частотного диапазона регистрируемых сигналов, На чертеже изображен один из возможных вариантов предлагаемого устройства, 10

Устройство содержит аналого-цифра" вой преобразователь 1, который под-. совдинен информационным входом через нормирующий элемент 2 к входной

1 шине 3 и соединен выходами с инфор1

1 мационными входами блока 4 памяти, подключенного выходами к информационным входам цифроаналоговых преобразователей 5, блок Ь регистрации, дешифратор 7,, формирователь 8 синхронизи- 20 ! рующих импульсов генератор 9 импульсов и счетчик 10. Цифроаналоговые ( преобразователи 5 соединены вьмодами через интерполирующие элементы 11

: с входами блока 6 регистрации и 25 подсоединены входами синхронизации записи к выходам дешифратора 7. Дешифратор 7 соединен первым входом стробирования с формирователем 8 синхронизирующих импульсов, который подсоединен тактовым входом к выходу генератора 9 импульсов и подключен ко входу запуска аналого-цифрового преобразователя 1, к входу записи блока 4 памяти и к счетному входу счетчика 10.

Устройство также содержит двухканальный мультиплексор 12, подключенный выходами к адресным входам блока 4 памяти, соединенный входом управления с формирователем 8 синхронизирующих импульсов и подсоединенный разрядными входами первого канала к разрядным выходам счетчика

10, триггер ?3 подключенный прямым вьмодом к второму входу стробирования дешифратора 7, дифференцирующий элемент 14 подсоединенный входом к шине 15 питания, и элемент НЕ 16.

Двухканальныи мультиплексор 12 под- 50 соединен первыми разрядными входами второго канала к предпоследним раз-,. рядным выходам счетчика 10, соединен предпоследними разрядными входами второго канала с первыми разрядными выходами счетчика 10 и подключен последним разрядным входом второго канала к выходу элемента НЕ 16, Элемент НЕ 16 соединен входом с послед. ним разрядным выходом счетчика 10, подключенным ко. входу установки триггера 13, подсоединенного входом сброса к выходу дифференцирующего элемента 14, соединенному со входом сброса счетчика 10, При этом первые разрядные выходы счетчика 10 подключены к адресным входам дешифратора 7, Устройство работает следующим образом.

Каждый импульс с генератора 9 импульсов запускает формирователь 8 синхронизирующих импульсов, который вырабатывает последовательность импульсов, поступающих на вход запуска аналого-цифрового преобразователя 1, на вход записи блока 4 памяти, на счетный вход счетчика 10 на первый вход стробирования дешифратора 7 и . на вход управления двухканального мультиплексора 12, По импульсу на входе запуска аналого-цифровой преобразователь 1 преобразует в код сигнал, поступающий со входной шины 3 через нормирующий элемент 2, По импульсу на входе записи код с аналого-цифрового преобразователя 1 заносится в блок

4 памяти. При этом адрес ячейки блока

4 памяти определяется счетчиком 10 через двухканальный мультиплексор 12.

По импульсу на входе управления через второй канал двухканального мультиплексора 12 на адресные входы блока 4 памяти подается модифициро-ванный код адреса. Содержимбе ячейки блока 4 памяти, адрес которой определяется:этим модифицированным кодом адреса, по импульсу на первом входе стробирования дешифратора 7 заносится в один из внутреннчх регистров цифроаналоговых преобразователей 5.

Вьмодные сигналы цифроаналоговых преобразователей 5 после сглаживания интерполирующими элементами 11 регистрируются н блоке 6 регистрации.

Так как темп вывода кодов из соседних ячеек блока 4 памяти в цифроаналоговые преобразователи 5 меньше, чем при занесении в блок 4 памяти, то на выходах цифроаналоговых преобразователей 5 происходит растяжение соответствующих участков сигнала, что эквивалентно сжатию его частотного диапазона, Последнее обеспечивает возможность регистрации сигналов, частотный диапазон которьм превосхо-..; дит частотный диапазон блока 6 региформула изобретения

Состави мль К.Розенкранц

Техред Л,Сердюкова Корректор Н.Король

Редактор А,Ревин

Заказ 1503 Тираж 461 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбикат "Патент", г.Ужгород, ул. Гагарина,101

5 157 страции в число раз, равное числу цифроаналоговых преобразователей 5.

Триггер 13 и дифференцирующий элемент 14 обеспечивают исключение неправильного вывода информации при включении, когда в блоке 4 памяти информация о сигнале еще не накопилась. При включении.дифференцирующий элемент 14 формирует импульс, сбрасывающий счетчик 10 и триггер 13. После заполнения блока 4 памяти наполовину сигнал с последнего разрядного выхода счетчика 10 устанавливает триггер 13 в состояние, при котором происходит разблокирование дешифратора 7. Благодаря этому по импульсу на первом входе.;стробирования дешифратора 7 во внутренние регистры цифроаналоговых преобразователей 5 заносятся соответствующие коды из ячеек блока 4 памяти.

Устройство для регистрации сигналов, содержащее аналого-цифровой преобразователь, подсоединенный входом к входной шине и соединенный выходами с информационными входами блока памяти, подключенного выходами к информационным входам цифроаналоговых преобразователей, которые соединены выходами с входами блока регистрации и подсоединены входами синхро= низации записи к выходам дешифратора, соединенного первым входом стробирования с формирователем синхронизи1397 6 рующих импульсов который подключен к входу запуска аналого-.цифрового преобразователя, к входу записи блока памяти и к счетному входу

5 счетчика и соединен тактовым входом с выходом генератора импульсов, и шину питания, о т л и ч а ю щ е е— с я тем, что, с целью расширения частотного диапазона регистрируемых сигналов, в него введены двухканальный мультиплексор, подключенный выходами к адресным входам блока памя-. ти, соединенный входом управления с

15 формирователем синхронизирующих импульсов и подсоединенный разрядными входами первого канала к разрядным выходам счетчика, триггер, подключенный прямым выходом к второ20 му входу стробирования дешифратора, дифференцирующий элемент, подсоединенный входом к шине питания, и элемент НЕ, причем двухканальный мугьтиплексор подсоединен первыми разряд-.. ными входами второго канала к предпоследним разрядным выходам счетчика, соединен предпоследними разрядными входами второго канала с первыми разрядными выходами счетчика, подключен30 ными.к адресным входам дешифратора, и подсоединен последним разрядным входом второго канала к выходу эле-, мента НЕ, соединенного входом с последним разрядным выходом счетчика, 3 подключенным к входу установки триггера, подсоединенного входом сброса к выходу дифференцирующего элемента, сОединенному с входом сброса счетчика.