Устройство для измерения скорости перемещения

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной технике и может найти применение в качестве датчика обратной связи по скорости в прецизионных приводах. Целью изобретения является повышение точности. Наличие в схеме устройства для измерения скорости перемещения многоканального распределителя импульсов 6, многоканального формирователя 7, многовходовой логической схемы 8 и формирователя импульсов стабильной амплитуды 9 позволяет сформировать в каждом периоде выходного сигнала фазовращателя 4 импульс с длительностью, пропорциональной модулю разности периодов питающего и выходного напряжений фазовращателя /коэффициент пропорциональности равен числу каналов/, и полярностью, соответствующей знаку этой разности. На выходе блока осреднения 10 эти импульсы преобразуются в постоянное напряжение, по величине которого и судят о скорости и направлении перемещения подвижной части фазовращателя. 2 з.п. ф-лы, 4 ил.

А1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (И) (1)5 G 01 Р 3/489

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н A ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

@Uz.1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ1

ПРИ ГКНТ СССР (21) 4333106/24-10 (22) 25.11.87 (46) 15;06,90. Бюл. ¹ 22 (71) Научно-производственное объединение "Ротор" (72) M.È. Ярославцев (53) 536,77 (088.8) (56) Авторское свидетельство СССР № 837197, кл, (: 01 Р 3/48, 3/489, 1978.

Авторское свидетельство СССР № 1173319, кл. G 01 P 3/489, 1984. .(54) УСТРОЙСТВО длЯ ИЗИКРКНИЯ СКОРОСТИ ПЕРЕМЕЩЕНИЯ (57) Изобретение относится к измерительной технике и может найти применение в качестве датчика обратной связи по скорости в прецизионных приводах. Целью изобретения является повьппение точности. Наличие в схеме

2 устройства для измерения скорости перемещения многоканального распределителя импульсов 6, многоканально.го формирователя 7, многовходовой логической схемы 8 и формирователя импульсов стабильной амплитуды 9 позволяет сформировать в каждом периоде выходного сигнала.фазовращателя

4 импульс с длительностью, пропорциональной модулю разности периодов питающего и выходного напряжений фазовращателя (коэффициент пропорциональности равен числу каналов); и полярностью, соответствующей знаку этой разности. На выходе блока осреднения 10 эти импульсы преобразуются в постоянное напряжение, по величине которого и судят о скорости и направлении перемещения подвижной части фазовращателя. 2 з.п.ф-лы,4 ил.

1571509

Изобретение относится,к измерительной технике и может быть использовано в качестве датчика обратной связи по скорости в прецизионных приводах.

Целью изобретения является повышение точности измерения.

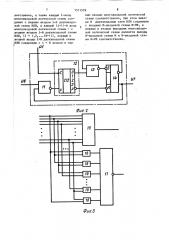

На фиг.1 представлена схема устройства для измерения скорости пере- 1О мещения; на фиг,2 — схема одного ка ала многоканального формирователя порных импульсов; на фиг.3 — схема ноговходовой логической схемы, на иг.4 — временные диаграммы работы я трехканального варианта устрой, тва.

Устройство для измерения скорости перемещения (фиг.1) содержит последовательно соединенные генератор 1 талонной частоты, делитель 2 частоты, блок 3 питания, фазовращатель компаратор 5, многоканальный рас пределитель 6 импульсов, многоканальный формирователь 7 опорных импульleos многовходовую логическую схему

Формирователь 9 импульсов стабильиой амплитуды и блок 10 соединения

Дополнительный вход формирователя (7 соединен также с выходом генера тора 1.

ЗО

Каждый канал многоканального фор ирователя 7 (фиг.2) содержит схему

2ИЛИ 11, двоичный счетчик 12, схемку 2И 13 и RS-триггер 14, причем

1 ервый вход схемы 2ИЛИ 11 является йнформационным входом канала, второй ход соединен с прямым выходом

gS-триггера 14 и выходом канала, а выход схемы 2ИЛИ 11 соединен с входом сброса двоичного счетчика 12, счет, ный вход которого является дополни гельным входом канала, а первый выход соединен с первым входом схемы 2И 13, второй вход которой соединен с инверсным выходом RS-триггера 14, а

45 выход - с установочным входом этого триггера, вход сброса которого соединен с выходом переполнения счетчика 12.

I 50

Иноговходовая логическая схема 8 (фиг.3) содержит N-входовую схему

Й 15, N двухвходовых схем ИЛИ 16 и

N-вх6довую схему И-НЕ 1I7, где N— число каналов в устройстве.

Устройство работает следующим об55 разом.

Высокочастотные импульсы с генератора 1 поступают через делитель 2 на вход блока 3 питания фазовращателя и на дополнительный вход многоканального формирователя 7 опорных импульсов. Блок 3 вырабатывает питание датчика 4 в виде синусоидальных напряжений с частотой выходного сигнала делителя 2. Компаратор 5 преобразует выходной сигнал фазовращателя 4 и последовательность прямоугольных импульсов, которые блоком 6 распределяются по и каналам формирователя 7, В каждом канале по переднему фронту входных импульсов запускается схема формирования опорных импульсов, Длительность опорных импульсов равна сумме п-1 периодов питающего сигнала фазовращателя 4. С выходов Формирователя 7 опорные импульсы поступают на соответствующие входы логической схемы 8, Этот блок вырабатывает последовательность импульсов с частотой выходного сигнала фазовращателя 4 и длительностью, пропорциональной модулю разности и .периодов питающего и выходного сигналов фазовращателя 4.

При положительной разности периодов сформированная последовательность импульсов выдается с первого выхода блока 8 и поступает на прямой вход формирователя 9. Когда эта разность отрицательная, то последовательность импульсов выдается на инверсный вход формирователя 9. Формирователь 9 преобразует входной сигнал а последовательность импульсов с постоянной стабильной амплитудой, с длительностью, равной длительности входных импульсов, и полярностью, соответствующей входу, на который поступает сигнал.

Блок 10 выдает среднее значение сформированной блоком 9 последовательности импульсов, которое и принимается в качестве сигнала скорости перемещения.

В кажцом канале блока 7 формирование опорных импульсов может быть выполнено, например, по схеме, представленной на фиг,2. Схема содержит элемент ИЛИ 11 с инверсией, счетчик

12 импульсов, элемент И 13 с инверсией и В.Я триггер 14.

B исходном состоянии счетчик 12 и триггер 14 обнулены. С приходом запускающего импульса Uq снимается запрет со счетчика 12 по входу R u начинается подсчет высокочастотных импульсов, поступающих на вход С. Первый входной импульс своим передним

5 15 фронтом перевалит выход 0" счетчика 12 в еди|н ч|»ае состояние. Вследствие этого на выходе элемента И 13 инверсией появляется нулевой импульс, который устанавливает триггер 14 в единичное состояние. После прихода импульсов, количество которых соответствует требуемой длительности опорного импульса, на выходе Р счетчика 12 появляется отрицательный импульс, сбрасьвающий триггер 14 в нулевое сос гояние. По цепи обратной связи (триггер 14 — элемент ИЛИ 11 с инверсией) обнуляется и счетчик 12

Тем самым схема возвращается в исходное остояние. Формируемы»» опорный чмпу Ibc с»»и».lacò я с прямого выхода григгера 1», Далее цикл повторяется. 1огическая схема 8 построена в соответствии c .л оги.-ческими уравнениями: .) Х» х X pre е erX

n (х, "x )х(х + x ) х ... х (х„+

+ х,, ) х (х„+ х,), где х — к о ныон к ция, + — дкз|ыонкцчя, -»нв ерсия, Когд период выходного сигнала датчика. 4 меньше периода его пита|ощих напряжений, то имеет место одновременное перекрытие опорных импульсов, jIIocTQiIRE01iIIix на все входы блока Я (|»Т 1, Ь 7, с» » э для и = 3) . Это перекрытие равно удвоенной, разности периодов питаюшего и выходного сигналов датчика 41, В соответствии с логикой блока в каждом периоде выходного сигнала датчика формируется импульс, длительно ть которого равна перекрытию опор»|ых импульсов, Сформированная последонатег»ьность импульсов выдается по первому вьгходу блока 8 (фиг.4 .U В-». °

Когда период выходного сигнала датчика 4 оказывается больше периода питаюших его напряжений, то вместо перекрытия импульсов возникает промежутОк зреь|ени между импульсами пас— тупаю»1||1| |и на входы блока 8 (фиг.4) .

Зтат врсменнай и-|тервал равен модулю удвоенной разности периодов питающего, и выходного сигналов датчика 4. Схема блока обеспечивает формирование

||а ега втором выходе (фиг.4 — Ui ) последовательности импульсОв с частО713U9

TOii E»bIX0itllOI A C1li" |»ала i»eTri:IKB 4 rl дЛИтельнастью, раьной промежутку време--|»и межд к аз я l»ными ап ар ныл »1 импуп ь с а» »1.

Формула изобретения

1. Устройство для измерения скорости перемещения, содержащее генератор эталонной частоты, делитель частоты и последовательно соединенные олок питания. фазавращатель, компаратОр распределитель и. ульсов, многоканальный формироват ль опорных импульсов, многавходавую логическую схему и блок ocредне:|ия, выход генератора эталoi»íoé частоты соединен с дополнительным входом мно20 гаканальнаго формирователя опорных иы|»ульсов, отличающееся тем, что, с целью повышения точности измерения, в неге введен формирователь и мпул ь с О в C T ß á EI JI ü í oé a i IIIJII I T „ Äû ii e рвый и второй входы которого соединены соответственно с первым и вторым выходами многовхадовой логической схех»ы, а выход — с входом блока осреднения, при этом выход генератора

3р эталонной час-.о ы соединен через делителЬ частоты с входом блока питания .2. Устройства по п. 1, о т л ич а ю щ е е с я тем, что каждый из и каналов многоканального формирователя Опорных импульсoB состоит из схемы ИЛИ, двоичного счетчика, схемы И и RS-триггера, причем первый вход схемы 1ПИ является информационным входам канала, второй вход coerri Q динен с прямы| выходом RS-триггера и выходом канала, а вьасод схемы ИЛИ . соединен с входом сброса двоичного счетчика, счетный вход которого является допол|н|тельным входом канала, а »5 первый выход соединен с первым входом схемы И, второй вход которой соединен с инверсным выходом КБ-триггера, а выход — с установочным входом

RS — триггера, вход сброса которого

50 соединен с выходом переполнения двоичного счетчика„

3. Устройство по и. 1, о т л иЧ а 10 Щ P P, С H Teм r»ÒО .МЕГОГОВХО» давая логическая схема содержит

N-входовую схему И, И двухвходовых схем ИЛИ и _#_-гхадавую схему И-НЕ, причем входы . и каналов соединены с

N входами»1-D:. o;Iol»oé cxe» lbi И сооТ

1571509 ветственно, а также каждьй i-вход многовходовой логической схемы соединен с первым входом i-й двухвходовой схемы ИЛИ, а каждый (+1)-й вход многовходовой логической схемы - с вторым входом i-й двухвходовой схемы

ИЛИ, (i 1,2,...(N-1)), первый и второй входы i=N двухвходовой схемы

ИЛИ соединены с i = N входом и пер

ИФ вым входом многовходовой логической схемы соответственно, при этом выходы N двухвходовых схем ИЛИ соединены

5 с входами Ж-входовой схемы И-НЕ а

Э первым и вторым выходами многовходовой логической схемы являются выходы

И-входовой схемы И H Ы-входовой схемы И-НК соответственно.

1571509

Составитель А. Кирилюк

Техред М.Дидык Корректор С. Черни

Редактор А. Маковская

Заказ 1509 Тираж 459 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 1О)