Устройство для сопряжения процессора с внешней памятью

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в многофункциональных устройствах цифровых систем обработки данных на базе микроЭВМ. Целью изобретения является повышение эффективности использования адресного пространства процессора. Устройство содержит блок 1 распределения адреса, первый 2, второй 3 блоки переключателей, первую 4 и вторую 7 группы элементов сравнения и группу 8 дешифраторов адреса. Устройство обеспечивает подключение к магистрали микроЭВМ внешней памяти, по емкости превосходящей адресное пространство процессора. 2 ил.

СОЮЗ СОВЕТСКИХ

COLIHAËÈÑÒÈ×ЕСКИХ

РЕСПУБЛИК (я) С 06 Р 13/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

508.1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

tlPH ГКНТ СССР (21) 4431520/24-24 (22) 1 8. 04. 88 (46) 15,06.90. Бюл. ¹ 22 (72) Л.И. Балановский, Н.И. Каплинский, П. В. Берштейн и Е. П. Плитко (53) 681.3(088.8) (56) Диалоговый вычислительный комплекс "Электроника HNC 01100,1-07"

У10э 170.001 ФО.

Авторское свидетельство СССР. № 1177820, кл, G 06 F 13/00, 1983. (54) УСТРОЙСТВО ДЛЯ СО11РЯЖЕНИЯ ПРОЦКСС()РА С ВНЕШНЕЙ ПАМЯТЬЮ (57) Изобретение относится к области вычислительной техники и может

„„SU„„1571597 А 1

2 быть использовано в многофункциональных устройствах цифровых систем обработки данных на базе микроЭВМ.

Целью изобретения является повышение эффективности использования адресного пространства процессора.

Устройство содержит блок 1 распределения адреса, первый 2, второй 3 блоки переключателей, первую 4 и вторую 7 группы элементов сравнения и группу 8 дешифраторов адреса.

Устройство обеспечивает подключение к магистрали микроЭВМ внешней памяти, по емкости превосходящей адресное пространство процессора.2 ил.

1571597

Изобретение относится к вычислительнои технике и может быть использовано в многофункциональных устройствах цифровых систем обработки данных на базе микроЭВМ.

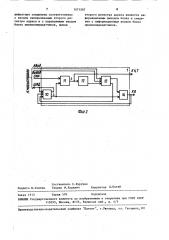

Цель изобретения — повышение эффективности использования адресного пространства процессора, На фиг.1 представлена блок-схема

:устройства;„на фиг.2 — схема блока распределения адреса.

Устройство содержит блок 1 распределения адреса, первый 2 и второй 3 блоки переключателей, первую группу 4 элементов сравнения, На фнг.1 представлена группа 5 блоков

1 б памяти. Устройство также содержит вторую группу 7 элементов- сравнения, группу 8 дешифраторов адреса выходы которых соединены со вхо дамии выборки группы 9 блоков внеш1 ней памяти.

Блок 1 распределения адреса содержит Ьлок 10 приемонередатчиков, первый регистр 11 адреса, первый дешифратор 12, второй дешифратор 13, второй регистр 14 адреса.

Устройство работает следующим образом. :. 30

Включение режима начальной загрузки осуществляется при механическом ,подключении к устройству (через разъем) выбранной группы блоков вне.,шней памяти. При этом блок 3 пере ключателей переводится в режим иа-) чальной загрузки и обеспечивает с пбмощью соответствующих компарато. ров необходимое переключение блоков памяти в адресном пространстве мик .роЭВМ, т.е. отключает i-й блок памяти микроЭВМ (i ф О), нулевому блоку памяти микроЭВМ присваивает i-й номер, а л качестве нулевого блока памяти микроЭВМ подключает к магистрали нулевой и первый блоки выбранной группы 9 блоков. внешней памяти. По сигналу запуска микроЭВМ процессор через блок 1 распределения адреса обращается к установленной для этой микроЭВМ ячейке нулевого Ьлока ее адресного пространства, т.е, к ячейке нулевого блока подключенной группы блоков внешней памяти При этом считывается управ4

55 ляющая информация, записанная в этой ячейке, а именно первая команда программы перезаписи информации из внешней памяти л ОЗУ микроЭВМ, Под управлением этой программы инфор. мация иэ последовательно подключае- . мых к магистрали микроЭВМ остальных блоков внешней памяти записывается в подключенные к магистрали блоки 6 памяти микроЭВМ. При этом в блок памяти микроЭВМ, включенный в этом режиме под i-м номером, производится запись команд для выполнения режима пуска загружаемой в память микроЭВМ программы.

Подключение очередного из бло" ков внешней памяти к MBI HcTpRfIH микроЭВМ осуществляется после загрузки в память микроЭВМ информации из предыдущего блока и его отключения в соответствии с программой, размещенной в нулевом блоке внешней памяти. При этом в блоке 1 осущестляется запись соответствующего кода, который по шине данных поступает на вторые входы дешифраторов 8 группы.

Механическое отключение группы

9 блоков внешней памяти от магистрали микроЭВМ переводит блок 3 переключателей в режим выполнения загруженной в память микроЭВМ программы.

При этом блок памяти, подключенный ранее под х-и номером к магистрали микроЭВМ, возвращается в исходное состояние, т.е. включается в качестве нулевого Ьлока памяти микроЭВМ к магистрали подключается отключенный ранее i-й блок памяти микроЭВМ. При формировании сигнала запуска микроЭВМ начинается выполнение загруженной в память микроЭВМ программы. .11ля выполнения микроЭВМ другой задачи с помощью разъема подключается другая группа блоков внешней памяти и устроиство обеспечивает ее взаимодействие с процессором через блок

1 по описанному алгоритму.

Блок 1 работает следующим образом.

При обращении процессора к памяти микроЭВМ соответствующий адрес через блок приемопередатчиков 10 поступает на вход регистра 11 адреса и синхроимпульсом адреса СИА с магИстрали микроЭВМ записывается в этот регистр.

Старшие М разрядов адреса поступают при этом на первые лходы первой

I группы 4 элементол. сравнения и на

1 первые входы второи группы 7 элементов сравнения, В случае совпадения с кодом, поступающим на их вторые

1571597 6 входы, один из элементов сравнения формирует разрешающий сигнал на вклю чение соответствующего блока памяти.

Записанный в регистр 11 адреса код поступает также на вход дешифра. тора 12 и в случае обращения процессора по определенному адресу дешифратор 12 формирует сигнал, разрещающий работу дешифратора 13 управляющих сигнаЛов. В зависимости от вида операции последний вырабатывает либо сигнал "Запись" в цикле записи, по которому код данных с магистрали микроЭВМ через блок 10 приемопередатчиков записывается в регистр 14 адреса внешней памяти, либо сигнал "Считывание" в цикле чтения, по которому через блок 10 приемопередатчиков производится чтение информации из регистра 14 адреса внешней памяти в магистраль микроЭВМ. При этом код, записанный в регистре 14 адреса внешней памяти, определяет один из блоков из подключенной к устройству группы 9 блоков внешней памяти, который вместе с нулевым блоком из этой группы блоков подключен в данный момент к магистрали микроЭВМ.

Формула изобретения

Устройство для сопряжения процессора с внешней памятью, содержащее блок распределения адреса, первый блок переключателей и первую группу элементов сравнения, причем группа входов-выходов блока распределения адреса является группой входов-выходов устройства для подключения группы входов-выходов адреса, данных и управляющих сигналов процессора, адресный выход блока распределения адреса соединен с первыми входами элементов сравнения первой группы, i-й выход (i = 2,...,m) первого блока переключателей соединен с вторым входом i-ro элемента сравнения первой группы (i = 2,...,m) выход i-ro (i = О,...,m) элемента сравнения первой группы является х-м выходом устройства для подключения к входу выборки i-ro блока памяти, о т л ич а ю щ е е с я тем, что, с целью повышения эффективности использования адресного пространства процессора, в него введены второй блок переключателей, вторая группа элемен5

55 тов сравнения н группа дешифраторов адреса, причем адресный выход блока распределения адреса соединен с первыми входами элементов сравнения второй группы, выход j -го элемента сравнения второй группы соединен с первым .входом j-ro (j = О,...,К) дешифратора адреса группы и является выходом устройства для подключения к входу выборки нулевогб блока внешней памяти j-й группы, р-й выход j -ro дешифратора группы является выходом устройства для подключения к входу выборки р-го (р =

1,...,k) блока внешней памяти j-й группы, нулевой выход первого блока переключателей через первую и вторую группы размыкающих контактов второго блока переключателей соединен с вторым входом нулевого элемента сравнения первой группы и через первую группы замыкающих контактов второго блока переключателей — с вторыми входами элементов сравнения второй группы, первый выход первого блока переключателей через третью группу размыкающих контактов второго блока переключателей соединен с вторым входом первого элемента сравнения первой группы и через вторую группу замыкающих контактов второго блока переключателей — с вторым входом нулевого элемента сравнения первой группы, информационный выход блока распределения адреса соединен с вторыми входами дешифраторов адреса группы, причем блок распределения ад— реса содержит блок приемопередатчиков, первый и второй регистры адреса и первый и второй дешифраторы,причем в блоке распределения адреса вход-выход блока приемопередатчиков является входом-выходом адреса данных группы входов-выходов блока, выход блока приемопередатчиков соединен с информационными входами первого ивторого регистров адреса, вход синхронизации первого регистра адреса является входом синхронизации адреса группы входов-выходов блока, выход первого -регистра адреса соединен с входом .первого дешифратора и является адресным выходом блока, выход первого дешифратора соединен с первым входом второго дешифратора, вто— рой и третий входы которого являются группой входов-выходов блока, первый и второй выходы второго де1571597

Составитель С,Бурухин

Редакто М.Товтин. Техред N.Õoäaíè÷ Корректор Л.Патай

Заказ 1513 Тираж 570 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКИТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул, Гагарина, 101 шифратора соединены соответственно с входом синхронизации второго регистра адреса и с управляющим входом

,блока приемопередатчиков, выход f второго регистра адреса является информационным выходом блока и соединен с информационным входом блока приемопередатчиков.