Устройство обмена данными для магистральной многомашинной вычислительной системы

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для построения вычислительных систем. Цель изобретения - повышение быстродействия обмена. После занятия магистрали системы одним из устройств 2 обмена данными блок 4 управления обменом устройства 2, захватившего магистраль, организует трансляцию адреса от передающей ЭВМ через шинный формирователь 7 и мультиплексоры 8 адреса на входы блоков 9 буферной памяти остальных устройств 2. Таким образом осуществляется одновременная запись данных от любой ЭВМ системы во все устройства 2. При свободной магистрали осуществляется чтение полученных данных из блоков 9. 4 ил.

СО1ОЭ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1571604 A 1 (ц) G 06 F 15/16, 13/38

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

« °

° ««

° °

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4315495/24-24 (22) 09.10.87 (46) 15.06.90. Бюл, N 22 (71) Северо-Западный заочный политехнический институт (72) В-.И. Гуткин, А.Г, Предтеченский и В.В. Ыеремет (53) 681.325(088,8) (56) Патент США Ф 4630193, кл. G 06 F 13/42, опублик. 1986.

Патент США N 4556939, кл. С 06 F 3/04, опублик. 1985. (54) УСТРОЙСТВО ОБМЕНА ДАННЬМИ ЛПЯ

МАГИСТРАЛЬНОЙ МНОГОМАИИННОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ (57) Изобретение относится к вычислительной технике и может быть использовано для построения вычислительных систем. Цель изобретения — повышение быстродействия обмена. После занятия магистрали системы одним из устройств

2 обмена данными блок 4 управления обменом устройства 2, захватившего магистраль, организует трансляцию адреса от передающей ЭВМ через шинный формирователь 7 и мультиплексоры 8 адреса на входы блоков 9 буферной памяти остальных устройств 2, Таким образом осуществляется одновременная запись данных от любой ЭВМ системы во все устройства 2. При свободной магистрали осуществляется чтение полученных даннь|х из блоков 9. 4 ил.

1571604

Изобретение относится к вычислительной технике и может быть использовано в многомашинных вычислительных комплексах для обеспечения связи с вычислительными устройствами.

Цель изобретения — повышение быстродействйя обмена.

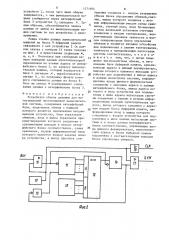

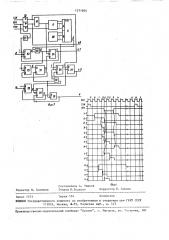

На фиг. 1 приведен пример многомацыниой вычислительной системы с.использованием устройства обмена данными; на фиг.. 2 — пример функциональной схемы блока синхронизации магистрали; на фиг. 3 " то же, блока управления

Обменом; на фиг. 4 — временные диа- граммы работы..

Многомашинная вычислительная система.(фиг. 1) может содержать блок

Синхронизации магистрали, которая состоит из линий тактирования — CLK, синхронизации — SVN занятости — BSV, пин данных — ВД и адреса — BA и К устройств 2 обмена данными, где К определяется количеством ЗВМ, подключаемых к системе. 25

Устройство обмена данными (фиг, 1) содержит интерфейсный блок 3, блок 4 управления обменом, счетчик 5, схему

6 сравнения, шинный формирователь 7, мультиплексор 8 адреса и блок 9 буферной памяти.

Блок 1 синхронизации магистрали (фиг. 2) содержит генератор 10 тактовых импульсов, счетчик 11,, схему 12 сравнення, переключатель 13, триггер

14, одновибратор 15, элементы И 16 и

17, передатчик 18.

Блок 4 управления обменом (фиг .3) содержит элемент И 19,, переключатель

20, инвертирующий передатчик 21, .эле- 4О ент И 22, триггеры 23-30, регистр 31, элемент И 32, приемник 33.

На временных диаграьмах (фиг. 4) цифры в буквенных обозначениях соответствуют К, т.е. номеру устройства обмена данными.

Устройство работает следующим образом.

В любой момент устройство может находиться в одном из трех режимов: ожидания обмена, передачи данных через магистраль и чтения данных вычислительной машиной иэ блока 9 буферной памяти, расположенного в принадлежащем ей устройстве 2. Все режимы пояснены

55 по временным диаграммам, представленным на фиг. 4. В любом иэ трех режимов блок 1 формирует,цве тактовые последовательности: на линии CLK синхросигнал с постоянным периодом и на линии ЯЧМ сигнал нулевой фазы. Все циклы обмена синхронизируются с названными сигналами, причем любые из К устройств 2 обмена данными могут захватить магистраль для передачи данных только в той фазе, которая имеет номер, соответствующий номеру устройства 2. Сигнал нулевой фазы SVN обеспечивает синхронизацию блоков 4 всех устройств 2. Линия ВБЧ используется только в режиме передачи данных и служит для индикации состояния "Канал передачи занят",. В режиме ожидания сигнал на линии BSV имеет уровень, соответствующий состоянию Канал передачи данных свободен".

Режим передачи устанавливается после возникновения запроса на передачу данных в любой из вычислительньгх машин. На фиг, 4 приведен пример передачи данных от вычислительной машины, подключенной к устройству 2 с номером

2. Запрос на передачу данных из интерфейсного блока 3 устройства 2 передается в блок 4, где on фиксируется в триггере 23 (сигнал с -2).

В фазе с номером 2 при условии незанятости канала передачи данных блок

4 занимает магистраль, устанавливая низкий уровень на линии BSV. С момента занятия канала счет фаз в блоке 1 (фиг. 2) и в счетчиках 5 всех устройств

2 прекращается до завершения цикла передачи данных, который продолжается в течение фаз 2-1, 2-2, 2-3 в рассматриваемом варианте устройства 2. Собственно процедура обмена и формируемые . в ее ходе реализации сигналы представлены на фиг. 4. Запрос (сигнал Л) возникает к моменту, когда данные и адрес уже выставлены на выходе интерфейсного блока 3 устройства 2 . При наличии запроса на передачу да"ных (сигнал h ) и совпадении фазы на линии

CLK с номером устройства 2, выставленном на переключателе 20, триггером

24 (сигпал Г) через передатчик 21 блокируется линия BSV. Низкий уровень на линии BSV запрещает счет фаэ в блоке

1 синхронизации магистрали, после чего начинается цикл передачи данных.

В этом цикле обеспечивается разрешение передачи адреса и данных по сигналу 2, переключение мультиплексоров

8 адреса всех остальных устройств 2 на прием адреса с шины адреса магистрали, запись данных в блоки 9 всех

5 157160 устройств 2, после чего цикл обмена завершается, о чем вычислительной машине сообщается через интерфейсный блок 3 устройства 2 сигналом Н . Таким образом, обеспечивается запись

5 данных от любой из вычислительных машин системы во все устройства 2 одновременно.

Режим чтения данных вычислительной машиной иэ блока 9 буферной памяти связанного с ней устройства 2 {в данном случае с номером 4) также показан на фиг. 4 и представлен графиками М, H К, Н . Поскольку при свободном канале передачи данных мультиплексоры 8 переключены на чтение адреса от интерфейсного блока 3, по запросу вычислительной машины, который передается в блок 4 сигналом М, вырабатывается 3Q сигнал Н., по перЕднему фронту которого считываются данные из блока 9.

Этот же сигнал Н подтверждает считывание данных и интерфейсному блоку 3.

Формула и з о бр ет ения устройство обмена данными для магистральной многомашинной вычислительной системы, содержащее интерфейсный блок, вход-выход обмена с машиной которого является одноименным входомвыходом устройства, блок управления обменом, вход и выход управления приемом-передачей которого соединены с одноименными выходом и входом интерфейсного блока соответственно, схему 35 сравнения, первый информационный вход которого является входом задания номера устройства, а выход признака совпадения соединен с входом разрешения обмена блока управления обменом, счетчик, выход которого соединен с вторым информационным входом схемы сравнения, счетный вход, вход блокировки и вход начальной установки счетчика соединены с входом тактирования, вхо- лом-выходом признака занятости и вхоI дом синхронизации блока управления обменом и являются входами устройства для подключения к линиям тактирования, занятости и синхронизации магистрали системы соответственно, о т л и ч аю щ е е с я тем, что, с целью повышения быстродействия обмена, в него введены блок буферной памяти, мульти" плексор адреса и шинный формирователь, выходЫ которого являются выходами устройства для подключения к шинам адреса и данных магистрали системы, информационные входы шинного формирователя соединены с выходами адреса и данных интерфейсного блока, выход адреса которого и вход устройства для подключения к шине адреса магистрали системы соединены с первым и вторым информационными входами мультиплексора адреса, выход которого соединен с адресным входом блока буферной памяти, ин-. формационные вход и выход которого соединены с входом устройства для подключения к шине данных магистрали системы и к входу данных интерфейсного блока соответственно, управляющие входы шинного формирователя, мультиплексора адреса и блока буферной памяти подключены к соответствующим выходам блока управления обменом.

1571 б04

Составитель А. Ушаков

Техред М.Ходанич

Корректор И. Король

Редактор N. Келемеш

Заказ 1513

Тираж 574

Подписное

BHHHIIH Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r, Ужгород, ул. Гагарина, 101