Устройство для управления @ -фазным тиристорным регулятором напряжения

Иллюстрации

Показать всеРеферат

Изобретение относится к электротехнике и может быть использовано для управления тиристорными регуляторами напряжения, обеспечения самоконтроля систем. Целью изобретения является исключение неполнофазных режимов работы тиристорного регулятора напряжения. В устройство для управления M-фазным тиристорным регулятором напряжения введены логический элемент ИЛИ, логические элементы ИСКЛЮЧАЮЩЕЕ ИЛИ по числу выходов узла ограничения длительности управляющих импульсов, два элемента ИЛИ-НЕ, соединенные выходами с входами элемента ИЛИ, а также элемент И и два блока селекции длительности сигналов, подключенные к входам элемента И, выход которого предназначен для подключения к исполнительному элементу отключения тиристорного регулятора напряжения. Каждый из выходов узла ограничения управляющих импульсов соединен с первым входом соответствующего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, предыдущим к соответствующему, выходы нечетных элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к входам первого элемента ИЛИ-НЕ, а выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к входам второго элемента ИЛИ-НЕ. Вход первого блока селекции длительности сигналов соединен с положительным выводом источника питания, а вход второго блока соединен с выходом логического элемента ИЛИ. 6 ил.

1733 А1

ИЕ (И) (ц)S Н 02 М 5/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСНОМЪ СВИДЕТЕЛЬСТВУ

Ala

° Ю

° Ф

° Ю

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4423599/24-07 (22) 11.05.88 (46) 15.06.90. Бюл. Р 22 (7 1) Донецкий политехнический институт (72) И.Т.Сидоренко, К.Н.Иаренич, В.С.Бакуменка, В.Я.Демидов, С.В.Дзюбан и В,Б.Иевчик (53) 62 1.316.727 (088.8) (56) Авторское свидетельство СССР

N- 1453554, кл. Н 02 М 5/22, 1986. (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ы-ФАЗНЫ1 ТИРИСТОРНЫ! РЕГУЛЯТОРОМ НАПРЯЖЕНИЯ (57) Изобретение относится к электротехнике и может быть использовано для управления тиристорными регуляторами напряжения и обеспечения самоконтроля систем. Целью изобретения является исключение неполнофазных режимов работы тиристорного регулятора напряжения. В устройство для управления тпфазным тиристорным регулятором напря,жения введены логический элемент ИЛИ, логические элементы ИСКЛЮЧАЮЩЕЕ ИЛИ

Изобретение относится к электротехнике и может быть использовано для управления тиристорными регуляторами напряжения и обеспечения само-контроля этих систем.

Целью изобретения является исклю-. чение неполнофазных режимов работы тиристориого регулятора.

На фиг, 1 изображена схема устройства, когда число фаз сети m 3; на фиг.2 - диаграмма работы устройства

2 по числу выходов узла ограничения длительности управляющих импульсов, два элемента ИЛИ-НЕ, соединенные выходами с входами элемента ИЛИ, а так.-. же элемент И и два блока селекции длительности сигналов, подключенные к входам элемента И, выход которого предназначен для подключения к исполнительному элементу отключения тиристорного регулятора напряжения. Каждый из выходов узла ограничения управляющих импульсов соединен с первым входом соответствующего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с вторым входом элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ, предыдущим к соответствующему, выходы нечетных элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к входам первого элемента ИЛИ-НЕ„ а выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к входам второго элемента

ИЛИ-НЕ..Вход первого блока селекции длительности сигналов соединен с положительным выводом источника питания, а вход второго блока соединен с,выходом логического элемента ИЛИ. 6 ил. при н=З и исправной работе;на фиг.3— диаграмма работы устройства при т=З и отсутствии одного из импульсов управления; на фиг.4 — диаграмма работы устройства при в=З и неотключении одного из импульсов управления; на фиг.5 — диаграмма работы устройства при та=3 и отсутствии импульсов управления двух соседних каналов; на фиг.б — диаграмма работы устройства

gapa m=3 и отсутствии импульсов управления тиристорами одной фазы.

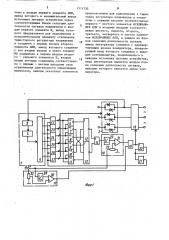

Устройство содержит блок 1 управления тиристорами регулятора 2 напряжения, синхронизированный с одной из фаз сети. S состав блока 1 входят соединенные последовательно фазосдвигающий узел 3, формирователь 4 управляющих импульсов и узел 5 ограничения длительности управляющих импульсов.

Устройство содержит также первый 6, второй 7. третий. 8, четвертый 9, пятый 10 и шестой 11 элементы ИСКЛЮЧАЮЩЕЕ

ИЛИ, два элемента ИЛИ-НЕ 12 и 13, выходы которых подключены к входам первого элемента ИЛИ 14. Входы элемента

12 соединены с выходами элементов 6, . 8 и 10, а входы элемента 13 - с выходами элементов 7„. 9 и 11. Положительный вывод 15 источника питания и выход элемента 14 подключены к вхо. дам первого элемента И 16 через первый и второй блоки 17 и 18 селекции длительности сигнала соответственно.

Выход элемента 16 подключен к исполнительному элементу 19 отключения ти ристорного регулятора 2 (например, к цепи управления контактора), а . также к первому входу второго элемента ИЛИ 20, выход которого соединен с его вторым входом и через элемент

ИЛИ 21 с вторыми входами второго 22, третьего 23, четвертрго 24, пятого

25, шестого 26 и седьмого 27 элементов И, первые входы которых соединены соответственно с первым — шестым выходами узла 5, а выходы — с первыми входами элементов 6-11 и вторыми входами элементов 11 6 7 8 9 и 10, а .также с цепями управления соответствуюцих тиристоров регулятора 2.

Блок 17 (18) содержит интегратор

28 (29), выход которого подключен к неинвертирующему входу компаратора

30 (31). Инвертируюцие входы компараторов 30 и 31 соединены с выходами потенциометров 32 и 33, подключенных к выводам источника питания. Выходы компараторов 30 и 3 1 являются выходами блокрв 17 и 18, входами которых являются входы интеграторов 28 и 29.

Элементы 20-27 позволяют повысить быстродействие отключения тиристорно-. го регулятора 2, обеспечить безПуговое отключение узла 19 путем воздействия на цепи управления его тиристоров, запрецая подачу на них импульсов управления с выходов узла 5.

Соединение выхода элемента 20 с его вторым входом обеспечивает его само71733

55 другом входе логической единицы (U ) с выхода блока 17 воздействуют на исполнительный элемент 19 отключения тиристорного регулятора 2, а также на элемент 20. Последний, самоблокируясь, запрещает (посредством инвертора 21 и элементов 22-27) подачу импульсов управления с выходов узла

5 на входы управления тиристорного регулятора 2.

Блок 17 формирует напряжение П... разрешаюцее прохождение импульсов

1 блокировку при появлении на выходе элемента 16 сигнала единичного уровня.

Устройство работает следующим образом

При нормальной работе блоке t на выходах узла 5 формируются импульсы

U«, - Пз < (фиг.2) длительностью «, одинаково сдвинутые дууг относительно друга по фазе на «/m. Импульсы управления с каждой пары соседних каналов узла 5 подаются на входы соответствующего элемента 6-11, на выходе которого формируются импульсы фазового несовпадения (U< - П„) входных импульсов управления. Длительность каж дого импульса на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ составляет «/m, а интервалы между ними составляют « (m-1)/m.

Выходные импульсы П, U и U элемен тов 6,8 и 10 подаются на входы элемента 12, а выходные импульсы U

U, элементов 7, 9 и 11 — на входы элемента 13. Логическое суммирование

25 этих импульсов с последующим инвертированием при нормальной работе всех каналов блока 1 дает в результате логические нули на выходах элементов

12 и 13.

При неисправности в блоке 1, определяющей отсутствие одного из импульсов управления, например U (фиг.3), неотключении одного из импульсов управления, например Пз « (фиг.4), отсутствии импульсов управления двух

35 соседних каналов, например U« и U (фиг.5), отсутствии импульсов управления тиристорами одной фазы, например U«« и U (фиг.6) и др., длитель40 ности соответствующих импульсов эле. ментов ИСКЛМЧАМ01ЕЕ ИЛИ изменяются равно, как и интервалы между ними.

Это приводит к появлению чередующихся логических единиц и нулей на выходах

45 элементов 12 и 13 (U z U ) ... .Импульсы

° 1 . °

U<<, U<> через блок 18 поступают на вход элемента 16 и при наличии на его

7t733

t5 на отключение тиристорного регулятора 2 напряжения с некоторой задержкой по отношению к моменту включения блока 1. Этим исключается ложное сраба- тывание устройства, поскольку при включении блока 1 импульсы управления, начиная с U><, формируются со сдвигом в N /ш длительностью в и при существовании первого импульса U, импульсы

U z< и U

Напряжение U,) порогового напряжения Uz» снимаемого с потенциометра 32.

Устройство сохраняет работоспособность и при полном исчезновении импульсов управления U< - U<< либо при появлении единичных уровней на усех выходах узла 5 ° В этом случае на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ устанавливаются логические нули, что определяет появление логических единиц на выходах элементов 12 и 13 и при наличии сигнала U

В процессе изменения углов управления тиристорами регулятора 2 (динамический режим работы регулятора и блока t) длительности отдельных импульсов управления незначительно колеблются, превышая или не достигая значения в рад, что может привести к появлению на выходах элементов 12 и 13 коротких импульсов. Для исключения их воздействия на элементы 19 и 20 предназначен блок 18,идентичный по принципу действия блоку 17 и формирующий логическую единицу при значениях импульсов Н, или б,, достигающих величины около "iT/m. Процесс формирования импульса U > показан на фиг.3, где U„ — напряжение интегратора 29,U„z- пороговое напряжение, снимаемое с выхода потенциометра 33 (импульс Н заштрихован).

При использовании предлагаемого устройства предотвращаются неполнофазные режимы работы электропривода, подключенного к тиристорноиу регулятору напряжения, вызванные невключениями тиристоров из-sa возможных от-, каздв системы управления тиристорамн.

При этом устройство обеспечивает самоконтроль каналов управления тирнсторами, поскольку в качестве сигналов, контролирующих наличие импульсов управления, используются сами импульсы управления.

Таким образом, устройство повышает надежность тиристорного регулятора напряжения, тиристорного электропривода в целом, предотвращает выход из строя асинхронных электродвигателей, питаемых от тиристорного регулятора напряжения, из-sa работы в неполнофазных режимах.

Применительно к шахтным электрическим сетям устройство, исключая эксплуатацию тиристорного регулятора напряжения в неполнофазном режиме, предотвращает ненормативные изменения уставки срабатывания участкового аппарата защиты от утечек тока на землю и, следовательно, возможность несрабатывания этого аппарата в случае касания человека к токоведущим элементам электрической сети на выходе тиристорного регулятора напряжения.

Формула изобретения

Устройство для управления ш-фаэным тиристорным регулятором напряжения, содержащее соединенные последовательно фазосдвигающий узел, вход каторога предназначен для подключения к одной из has сети, формирователь управляю- щих импульсов и узел распределения с ограничением длительности управляющих импульсов и источник питания устройства, о т л и ч а ю щ е е с я тем, что, с целью исключения неполнофазных режимов работы тиристорного регулятора напряжения, устройство снабжено семью элементами И, шестью элементами ИСКЛЮЧАЮТ!ЕЕ ИЛИ, двумя элементамн ИЛИ-НЕ, двумя элементами

ИЛИ, элементом НЕ и двумя блоками селекции длительности сигнала, каждый из которых содержит интегратор, компаратор и потенциометр, причем выходы нечетных элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с входами первого элемента ИЛИ-HF., выходы четных элементов ИСКЛР)ЧАЮЩЕЕ ИЛИ соединены с входами второго элемента ИЛИ-НЕ, выходы обоих элементов ИЛИ-НЕ подклю1571733 чены к входам первого элемента ИЛИ, выход которого и положительный вывод источника питания устройства через соответствующие блоки селекции. длительности сигнала подключены к входам первого элемента И, выход которого предназначен для подключения к исполнительному элементу отключения ,тиристорного регулятора напряжения и соединен с первым входом второго

:элемента ИЛИ, выход которого соединен с его вторым входом и через элемент

HE подключен к первым входам второ,го — седьмого элементов И, вторые входы которых соединены соответственно с первым — шестым выходами узла ограничения длительности управляющих импульсов, выходы указанных элементов предназначены для подключения к тирис торам регулятора напряжения и соединены с первыми входами соответственно первого — шестого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и вторыми входами соответственно шестого, первого, втсрого, третьего, четвертого и пятого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, в каждом из блоков селекции длительности сигнала выход интегратора соединен с неинвертирующим входом компаратора, инвертирующий вход которого соединен с выходом потенциометра, подключенного к выводам источника питания устройства, вход интегратора является входом блока селекции длительности сигнала, выходом которого является выход компаратора.

1571733

157 l 733

t Ц(И2

Фиг 3

Ur о

Ъ

О

Ug

<3_#_ 4

1571733

1571733 Фиг.б

Составитель В.Миронов

Редактор А.Лежнина Техред М.Ходанич Корректор О. Кравцова

Заказ 1520

Тираж 500

Подписное

ВНИИПИ Государственного комитета по изобретениям,и открытиям при ГКНТ СССР

1 13035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издатепьский комбинат "Патент", г, Ужгород, ул. Гагарина, 101