Устройство для формирования вычета последовательного двоичного кода по модулю

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения различных устройств передачи и переработки дискретной информации. Цель изобретения - расширение функциональных возможностей за счет формирования вычета по произвольному модулю. Устройство содержит триггер 1, блок 3 синхронизации, элемент И 4, счетчик 5 по модулю, делитель 6, счетчик 7 по модулю, группу элементов И 8.1 - 8.P, сумматор 9, элемент И 10, вычитающий счетчик 11 с соответствующими связями. 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 Н 03 N 7 18

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ASTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

fl0 ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ П4НТ СССР (21) 4471443/24-24 (22) 09.08.88 (46) 15.06.90. Бюл. Ы 22 (72) О.Н.Музыченко, В.Н.Рыжевнин и В.В.Штплков (53) 68!.3 (088.8). (56) Авторское свидетельство СССР

9 1396281, кл. Н 03 М 7/18, 1986.

Авторское свидетельство СССР

Р 1285481, кл. G 06 F 11/10, 1985 (прототип) . (54) YCTPOACTBO ДЛЯ ФОРМИРОВАНИЯ ВЫЧЕТА ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА ПО МОДУЛЮ

„„SU„„1571771 А1

2 (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения различных устройств передачи и переработки дискретной информации. Цель изобретения — расширение функциональных возможностей за счет формирования вычета по произвольному модулю. Устройство содержит триггер 1, блок 3 синхронизации, элемент И 4, счетчик

5 по модулю, делитель 6, .счетчик 7 по модулю, группу элементов И 8.18.Р, сумматор 9, элемент И 10, вычитающий счетчик 11 с соответствующими связями. 4 ил.

1571 771

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения различных устройств передачи и .переработки дискретной информации.

Цель изобретения — расширение функциональных возможностей за счет ормирования вычета по произвольному одулю.

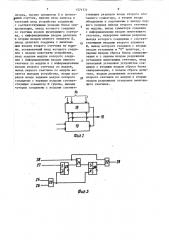

На фиг. 1.представлена схема устойства для формирования вь1чета поседовательного двоичного кода по модулю; на фиг. 2 — схема первого счетчика по модулю; на фиг. 3 — блок синхронизации; на фиг. 4 — схема второго счетчика по Модулю.

Устройство (фиг. 1) содержит триггер 1, тактовый вход 2 устройства, блок 3 синхронизации, первый элемент !

И 4, первый счетчик 5 по модулю, делитель 6, второй счетчик 7 по модулю, группу элементов И 8.1-8.Р, сумматор 9, второй элемент И 10, вычитающий счетчик 11, информационный вход

12 устройства, вход 13 запуска устройства, вход 14 задания модуля устройства, вход t5 константы устройства, выход 16 устройства, вход 17 начальной установки устройства.

Первый. счетчик 5 по модулю (фиг ° 2) содержит схему 18 сравнения и суммирующий двоичный счетчик 19, счетный вход и вход сброса которого являются соответствующими входами счетчика 5

1 по модулю, а выход — его выходом.

Выход счетчика 19 соединен с первым входом схемы 18 сравнения, второй вход которой является информационным входом счетчика 5 по модулю, а выход соединен с входом сброса счетчика 19.

Блок 3 синхронизации (фиг. 3) содержит элементы ИЛИ 20, запрета 21, И 22, первый и второй триггеры 23 и

24, первый и второй входы 25 и 26 сброса блока 3 синхронизации, вход

27 запуска .блока 3 синхронизации, тактовый вход 28 и выход 29 блока

3 синхронизации. Причем входы 25 и 26 через элемент ИЛИ 20 соединены с входами установки в нуль триггеров

23 и 24, выходы которых соединены соответственно с информационным входом элемента 21 запрета и с первым входом элемента И 22. Выходы последних соединены соответственно с входом установки в единицу триггера

24 и с выходом 29. Вход 27 соединен с входом установки в единицу триг1О

ЗО

50 гера 23, Вход 28 соединен с управляющим входом элемента 21 запрета и с вторым входом элемента И 22.

Второй счетчик 7 по модулю (фиг. 4) содержит вычитающий двоичный счетчик 30, элемент 31 запрета, группу элементов ИЛИ 32.1-32.Р, две группы элементов И 33.1-33.Р, 34.1-34.Р, элемент ИЛИ .35, вычитающий вход 36 счетчика 7, информационный вход 37 счетчика 7, вход 38 разрешения установки счетчика 7, установочный вход 39 счетчика 7, выход

40 счетчика ?. Причем выход элемента

ИЛИ 35 соединен с входом разрешения записи счетчика 30, входы разрядов которого соединены с выходами соответствующих элементов ИЛИ 32.1-32.Р группы. Входы последних соединены с выходами соответствующих элементов

И 33.1-33.Р и 34.1-34 .Р групп, первые входы которых соединены с входами соответствующих разрядов становочного входа 39 и информационного входа 37 счетчика 7. Вход 38 разрешения установки последнего соединен с вторыми входами элементов И 33.133.P группы и с первым входом элемента ИЛИ 35, второй вход которого соединен с вторыми входами элементов

И 34.1-34.Р группы и с выходом элемента 31 запрета. Управляющие входы последнего соединены соответственно с выходами разрядов и счетным входом счетчика 30. Счетный вход 36 и выход

40 счетчика 7 являются соответствующими входами и выходами счетчика 30.

Счетчик 11 реализуется аналогично.

Делитель 6 представляет собой счетный триггер, Разрядность счетчиков 11, 19, 30 выбирается равной )log (К„„ „,+1 = Р, Устройство работает следующим образом.

В исходном состоянии на вход 14 устройства подан двоичный код модуля

К, по которому осуществляется формирование остатка, а на вход 15 — код остатка по модулю К веса старшего разряда входного кода. На вход 17 подается импульс сброса. При этом триггер 1 устанавливается- в состояние, при котором на его прямом выходе нулевой сигнал, запрещающий происхождение импульсов через элемент И 4.

Блок 3 синхронизации сбрасывается в состояние, при котором импульсы с входа 2 не проходят на его выход.

1571 77 i

Счетчик 5 по модулю сбрасывается в нулевое состояние. В счетчик 7 по модулю записывается код остатка по модулю К веса старшего разряда входно5 го кода с входа 15 устройства. При этом код с выхода счетчика 7 по модулю поступает на первую группу входов сумматора 9. Если в младшем разряде кода единица, то на вторую группу входов сумматора 9 подается код модуля К с выходов элементов И группы 8.1-8.P. Сформированный на выходе сумматора 9 код записывается в вычитающий счетчик 11. 15

При поступлении на вход !3 импульса осуществляется запуск блока

3 синхронизации, на выход которого при этом начинают проходить импульсы с входа 2. Если импульс синхронизации совпадает с тактовым, то этот тактовый импульс на выход блока 3 . синхронизации не проходит, чем исключается прохождение на входы счетчиков 11, 5 и делителя 6 укороченньп 25 импульсов, которые могут быть пропущены или привести к неправильному их срабатыванию.

Тактовые импульсы с выхода блока

3 синхронизации поступают на счетный 30 вход вычитающего счетчика 11, от содержимого которого каждый раз вычитается единица, и на информационный вход делителя 6, который осуществляет их деление с коэффициентом, равным двум.

Импульсы 6 с выхода делителя 6 поступают на вычитающий вход счетчика 7 по модулю, от содержимого которого каждый раз вычитается единица. 4О

Работа продолжается, таким образом, до обнуления вычитающего. счетчика

11. При этом на всех входах элемента

И 10 появляются единичные сигналы и на его выходе появляется единичный сигнал, который поступает на вход установки в нуль триггера 1, возвращая его в исходное состояние, на вход сброса блока 3 синхронизации, возвращая его в исходное состояние, д) при котором тактовые импульсы не проходят на выход, и на установочный вход вычитающего счетчика 11, разрешая запись в него кода с выхода сумматора 9. При э-ом в вычитающий счетчик 11 записывается код остатка

q по модулю К веса следующего разряда, при q — - четном, либо код числа

q + q — нечетном.

Если одновременно с импульсом на входе 13 на информационный вход 12 устройства поступает входной импульс, свидетельствующий о единичном значении данного разряда входного кода, то он переключает триггер 1, на прямом выходе которого появляется единичный сигнал. При этом тактовые импульсы с выхода блока 3 синхронизации проходят через элемент И 4 на счетный вход счетчика 5 по модулю, к содержимому которого при этом каждый раз прибавляется единица. В результате за время обработки очередного разряда входного кода в счетчик

5 поступает число импульсов, равное остатку q по модулю К веса разряда кода, поступающего на вход устройства, либо равное К + q (если q — нечетное), и к содержимому счетчика 5 по модулю прибавляется величина остатка по модулю К веса данного pasряда. В результате в момент окончания обработки последнего разряда на выходе 16 оказывается записанным код остатка по модулю К входного кода.

Таким образом, предлагаемое устройство позволяет формировать остаток по произвольному модулю К последовательно поступающего двоичного кода. формула изобретения

Устройство для формирования вычета последовательного двоичного кода по модулю, содержащее триггер, первый и второй элементы И, первый и второй счетчики по модулю и сумматор, причем информационный вход устройства соединен с входом установки в "1 триггера, выход которого соединен с первым входом первого элемента И, выход которого соединен со счетным входом первого счетчика по модулю, вход начальной установки устройства соединен с входом сброса первого счетчика по модулю и с первым входом установки в 0" триггера, выходы разрядов второго счетчика по модулю соединены с входаМи соответствующих разрядов первого слагаемого сумматора, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет формирования вычета по произвольному модулю, оно содержит блок синхронизации, де15717/1 литель, группу элементов И и вычита-! ющий счетчик, причем вход запуска и тактовый вход устройства соединены с соответствуюшими входами блока синхронизации, выход которого соединен

5 со счетным входом вычитающего счетчика, с информационным входом делителя и вторым входом первого элемента И, выход делителя соединен с вычитаю, щим входом второго счетчика по моду; лю, установочный вход которого соеди( нен с входом константы устройства, . вход задания модуля которого соединен с информационным входом первого

, счетчика по модулю и с информационным

, входом второго счетчика по модулю, ,выход первого счетчика по модулю яв ляется выходом устройства, входы разрядов входа задания модуля которого соединены с первыми входами соответствующих элементов И группы, выходы ,которых соединены с входами соответствующих разрядов входа второго слагаемого сумматора, а вторые входы объединены и подключены к выходу первого разряда выхода второго счетчика по модулю, выход сумматора соединен с информационным входом вычитающего счетчика, инверсные выходы разрядов выхода которого соединены с соответствующими входами второго элемента

И, выход которого соединен с вторым входом установки в "О" триггера, с первым входом сброса блока синхронизации и с первым входом разрешения установки вычитающих счетчика, вход начальной установки устройства соединен с вторыми входом. сброса блока синхронизации, с входом сброса делителя, входом разрешения установки второго счетчика по модулю и вторым входом разрешения установки вычитающего счетчика.

1571771

Составитель А.Клюев

Техред Л.Сердюкова Корректор С,Черни

Редактор И.Касарда

Тираж 662

Заказ 1522

Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101