Устройство для адресации

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве модуля для аппаратного взаимного преобразования логических и физических адресов любых функционально законченных блоков (процессоров, блоков памяти и т.д.). Целью изобретения является расширение функциональных возможностей устройства и области его применения за счет обратного преобразования физического адреса блока в его логический адрес. Устройство содержит группу переключателей 1-3 логического адреса, регистр 4 логического адреса, дешифратор 5 логического адреса, первую группу элементов 6 и 7 ИЛИ, блоки 8 и 9 коммутации первой, второй группы, шифратор 11 физического адреса, регистр 13 физического адреса, дешифратор 14 физического адреса, вторую группу элементов 15 и 16 ИЛИ, шифратор 17 логического адреса. Введение регистра 13, дешифратора 14, шифраторов 11, 17 и изменение конструкции блоков коммутации позволяет осуществлять как преобразование логического адреса в физический, так и наоборот, причем прямое и обратное преобразования могут происходить одновременно и независимо друг от друга. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„Я0„, 157345 (51)5 G 06 F 12/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

49иг. 7

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (61) 1388877 (21) 4487231/24-24 (22) 26.09.88 (46) 23.06.90. Бюл. М - 23 (72) Н.Г.Пархоменко, В.Ю.Лозбенев, В,Г.Черняев и С.В.Козелков (53) 681.325 (088;8) (56) Авторское свидетельство СССР

1388877, кл. G 06 F 12/00, 1988.

2 (54) УСТР01 СТВО ДЛЯ АДРЕСАЦИИ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве модуля для аппаратного взаимного преобразования логических и физических адресов любых функционально законченных блоков (процессоров, блоков памяти и т.д.). Целью изобретения

1573458

4 является расширение функциональных воэможностей устройства и области его применения за счет обратного преобраования физического адреса блока в го логический адрес. Устройство соержит группу переключателей 1-3 ло гического адреса, регистр 4 логического адреса, дешифратор 5 логического адреса, первую группу элементов ИЛИ б и 7, блоки 8 и 9 коммутации первой, второй групп, шифратор 11 физическо.го адреса, регистр 13 физического адИзобретение относится к автоматике ! вычислительной технике, может быть 20 спользовано в качестве модуля для аппаратного взаимного преобразования логических и физических адресов любых функционально законченных блоков (процессоров, блоков памяти и т.д.) 25 и является усовершенствованием уст,ройства по авт. св. ¹ 1388877.

Целью изобретения является расширение функциональных возможностей и области применения устройства за счет обратного преобразования физического адреса блока в его логический адрес.

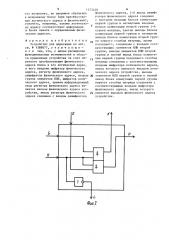

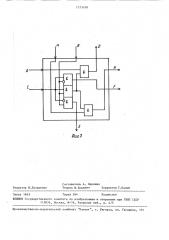

На фиг.1 представлена функциональ:ная схема устройства для трех блоков, на фиг.2 и 3 — функциоцальные схемы элементов коммутации первой и второй

35 групп соответственно.

Устройство содержит группу пере-, ключателей 1-3, регистр 4 логического адреса, дешифратор 5 логического адреса, первую группу элементов ИЛИ

6 и 7, блоки 8 и 9 коммутации первой и второй группы, вход 10 логического адреса устройства, шифратор 11 физического ацреса, выход 12 физического адреса устройства, регистр 13 физического адреса и дешифратор 14 физического адреса устройства, вторую группу элементов ИЛИ 15 и 16, шифратор 17, выход 18 логического адреса устройства, вход 19.

Устройство работает следующим образом.

Блок 8 коммутации (фиг.2) реализует логические функции K=GH, L =Í, Р=НО, где G,Н,О,К,L,Р— сигналы на первом, втором, третьем входах и выходах блока 8 коммутации первой группы соответственно. реса, дешифратор 14 физического адреса, вторую группу элементов ИЛИ 15 и 16, шифратор 17 логического адреса.

Введение регистра 13, дешифратора l4, шифраторов 11, 17 и изменение конструкции блоков коммутации позволяет осуществлять как преобразование логического адреса в физический, так и наоборот, причем прямое и обратное преобразования могут происходить одновременно и независимо друг от друга.

3 ил.

Блок 9 коммутации (Фиг,3) реализует функции Б=АВС, Е=ВС, N=BCM и

F=BC, где А,С,В,M,D,Å,F,N -сигналы на первом — четвертом входах и первом— четвертом выходах блока 9 коммутации второй группы соответственно.

Сразу же после подачи питания начинается сеанс коммутации в матрице блоков 8(9) в соответствии с сигналами переключателей:" .1-3. Сигнал высокого уровня (ВУ) на выходе переключателей 1-3 соответствует состоянию Блок включен /исправен, сигнал низкого уровня (НУ) — состоянию "Блок выключен/неисправен".

После завершения переходных процессов в матрице блоков 8(9) коммутации устройство готово к работе в режиме взаимопреобразования логического и физического адресов. При этом логический адрес " 1" всегда свяэыва11 lt ется с таким физическим адресом который соответствует j-му функциональному блоку из числа неотключенных/исправных блоков и наоборот (т.е. соответствие между полями логических и физических адресов для данного распределения флагов годности, заданного переключателями 1-3, является взаимно однозначными).

Например, пусть переключатель 1 находится в положении НУ, а переключатели. 2 и 3 — в положении ВУ. Тогда логический адрес "1" на выходе 10 соответствует физическому адресу "2" на выходе 12, а физический адрес "3" на входе 19 соответствует логическому адресу "2" на выходе 18, Причем преобразования логических адресов в физические и обратно происходят совершенно независимо друг от друга, 5 15 что позволяет, не прерывая обращения к исправному блоку (при преобразовании логического адреса в физический),,узнавать, например, какому логическому адресу соответствует информация в блоке памяти с определенным физическим адресом.

Формула изобретения

Устройство для адресации по авт. св. Ф 1388877, о т л и ч а ю щ е.— е с я тем, что, с целью расширения функциональных возможностей и области применения устройства за счет обратного преобразования физического адреса блока в его логический адрес, в него введены шифратор физического адреса, регистр физического адреса, дешифратор физического адреса, вторая группа элементов ИЛИ, шифратор логического адреса, причем информационный вход регистра физического адреса является входом физического адреса устройства; .выход регистра физического адреса соединен с входом дешифратора

73458 6 физического адреса, j-é выход дешифратора физического адреса соединен с третьими входами блоков коммутации первой группы и четвертыми входами блоков коммутации второй группы j-й строки матрицы, третьи выходы блоков коммутации первой группы и четвертые выходы блоков коммутации второй груп1О пы каждого столбца матрицы, кроме последнего, соединены с входами соответствующих -элементов ИЛИ второй группы, выходы элементов ИЛИ второй группы и третий выход блока коммутации первой группы последнего столбца матрицы соединены с соответствующими входами шифратора логического адреса, выход которого является выходом логического адреса устройства, выходы

20 элементов ИЛИ первой группы и первый выход блока коммутации первой группы первого столбца матрицы соединены с соответствующими входами шифратора физического адреса, выход которого

25,является выходом физического адреса устройства.

1573458

Составитель А. Бархина

Техред M.Õoäàíè÷ Корректор Т.Палий

Редактор Н.Лазаренко

Заказ 1643 Тираж 564 Подписное

3НИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r Ужгород, ул. Гагарина, 101