Устройство для цифровой записи воспроизведения речевой информации

Иллюстрации

Показать всеРеферат

Изобретение относится к накоплению информации, а именно к устройствам для цифровой записи-воспроизведения речевой информации. Устройство предназначено для повышения помехозащищенности записи информации за счет уменьшения искажений начальных участков речевых фрагментов, что достигается повышением точности определения границ речевых фрагментов при записи цифрового речевого сигнала в блок 10 памяти. В устройстве в качестве аналого-цифрового преобразователя используется дельта-модулятор-демодулятор 1. При записи речевого сигнала осуществляется компрессия пауз при помощи порогового контроля уровня речевого сигнала посредством компаратора 27. При этом информация о длительности речевых фрагментов и пауз записывается в блок 15 памяти. 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11> (51)5 G 11 В 20 00

ОЛИСАНИЕ ИЗОБРЕТЕНИЯ

М АBTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГННТ СССР

- (21) 4376478/24-10 (22) 09.02.88 (46) 23.06.90. Бюл. Р 23 (71) Ленинградский электротехнический институт связи им. проф. М.А.БончБруевича (72) M.Ó.Банк, E.С.Барбанель, А.Ю.Бухинник, Б.И.Шехтман и П.Е.Щербатый (53) 68 1.84 .001 2 (088.8) (56) Патент Японии Y, - 52-32244, кл. 102Е.33, опублик. 1977.

Авторское свилетельство СССР

9 1272355, кл. G 11 В 20/10, 1985.

Авторское свидетельство СССР

9 1312641, кл. G 11 В 20/00, 1985. (54) УСТРОЙСТВО ДДЯ ЦИФРОВОЙ ЗАЛИСИВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ (57) Изобретение относится к накоп2 лению- информации, а именно к устройствам цифровой записи-воспроизведения речевой информации. Устройство предназначено для повышения помехозащищенности записи информации эа счет уменьшения искажений начальных участков речевых фрагментов, что достигается повьипением точности определения границ речевых фрагментов при записи цифрового речевого сигнала в блок 10 памяти. В устройстве в качестве аналого-цифрового преоб разователя используется дельта-модулятор-демодулятор 1. При записи речевого сигнала осуществляется компрессия пауз при помощи порогового контроля уровня речевого Сигнала посредством компаратора 27. При этом информация о длительности речевых фрагментов и пауз записывается в блок 15 памяти. 2 ил.

1573470

Изобретение относится к накоплению информации, а именно к устройствам для цифровой записи-воспроизведения речевой информации.

Целью изобретения является сниже ние погрешности записи-воспроизведения речевой информации.

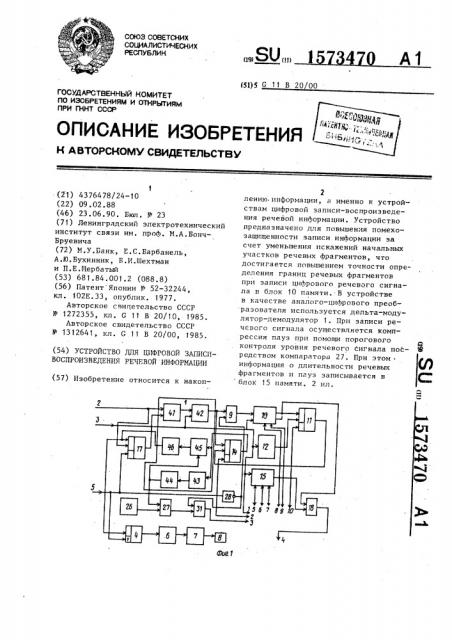

На фиг. 1 и 2 приведена структурная схема устройства для цифровой 10 записи-воспроизведения речевой информации.

Устройство для цифровой записивоспроизведения речевой информации одержит дельта-модулятор-демодулятор 15

i1 подключенный первым аналоговым ходом к вхоцной шине 2, синхронизи ующим входом — к шине 3 синхронизации, аналоговым входом — к входу первого ключевого элемента 4, подсоединенного управляющим входом к

Ьине 5 управления и выходом через

Последовательно соединенные фильтр

6 нижних частот и усилитель 7 к выI одной шине 8. Дельта-модулятор-демодулятор 1 подключен цифровым выходом через первый элемент И9 к входу первого блока 10 памяти, подключенного пе1 вым выходом к первому входу первого мультиплексора 11, соединенного вторым входом через генератор

12 кода паузы с шиной 3 синхрониза" ции, управляющим входом — с выходом счетного триггера 13 и выходом с пер вым входом второго мультиплексора 14, подключенного вторым входом к цифровому выходу дельта-модулятора-демоДулятора 1, управляющим входом — к йгине 5 управления и выходом к цифровому входу дельта-модулятрра-демоду- 40 лятора 1. Устройство также содержит второй блок 15 памяти, второй ключевой элемент 16, третий мультиплексор

17, с первого по пятый элементы ИЛИ

18т22, с первого по третий счетчики

23-25, формирователь 26 порогового напряжения, компаратор 27, с первого по третий инверторы 28-30, с второго по восьмой элементы И 31-37, первый 38 и второй 39 формирователи им50 пульсов и третий блок 40 памяти. При этом формирователь 26 порогового напряжения подключен выходом к первому входу компаратора 27, соединенного вторым входом с управляющим входом дельта-модулятора-демодулятора 1 и

55 выходом с первым входом элемента И

31, подсоединенного вторым входом к соединенным между собой соответствующему входу первого элемента И 9 и выходу первого инвертора 28, подключенного входом к управляющей ыине 5, первому входу четвертого элемента И

33, первому входу шестого элемента

И 35, управляющему входу третьего блока 40 памяти и через второй инвертор 29 к соединенным между собой первым входам третьего, пятого и седьмого элементов И 32, 34 и 36 и к входу первого формирователя 38 импульсов. Первый формирователь 38 импульсов подсоединен выходом к соеди-, ненным между собой установочному входу счетного триггера 13 и первому входу третьего элемента ИЛИ 20, подключенного вторым входом к выходу второго ключевого элемента 16 и первому входу второго элемента ИЛИ 19 и выходом к установочным входам второго и третьего счетчиков 24 и 25, соединенных выходами с адресными входами первого 10 и второго 15 блоков памяти и входами с выходами соответственно восьмого элемента И 37 и четвертого элемента ИЛИ 21. Четвертый элемент ИЛИ 21 подключен первым входом к соединенным между собой входу разрешения первого счетчика 23, соединенного установочным входом с выходом второго элемента ИЛИ 19, входами и выходами — с выходами и входами третьего блока 40 памяти и суммирующим и вычитающим входами с выходами соответственно третьего и четвертого элементов И 32 и 33, и к выходу шестого элемента И 35, подсоединенного вторым входом к входу счетного триггера 13 и к выходу переноса первого счетчика 23, и подключен вторым входом к управляющему входу второго блока 15 памяти, второму входу второго элемента ИЛИ 19 и выходу седьмого элемента И 36. Седьмой элемент И 36 подсоединен вторым входом к выходу второго формирователя 39 импульсов, подключенного входом к соединенным между собой выходу второго элемента

И 31, второму входу пятого элемента

И 34; подсоединенного выходом к управляющему входу первого блока 10 памяти и первому входу пятого элемента ИЛИ 22, соединенного вторым входом с инверсным выходом счетного триггера 13 и выходом с первым входом восьмого элемента И 37. Восьмой элемент И 37 подключен вторым входом к третьему входу пятого элемента И

5 15

34, вторым входам третьего и четвертого элементов И 32 н 33 и шине 3 синхронизации. Кроме того, третий блок 40 памяти соединен шиной данных с шиной данных второго блока

15 памяти, первый элемент ИЛИ 18 подключен первым входом к второму входу первого блока 10 памяти и выходом через третий инвертор 30 к четвертому входу пятого элемента И 34, а третий мультиплексор 17 подключен выходом к второму аналоговому входу дельта-модулятора-демодулятора 1, управляющим входом — к шине 5 управления, первым входом — к аналоговому выходу дельта-модулятора-демодулятора 1, а вторым входом — к входной шине 2. Кроме того, дельта-модулятор-демодулятор 1 содержит последовательно соединенные между собой элемент 41 сравнения, формирователь

42 информационной импульсной последовательности, последовательно соединенные между собой компаратор 43; интегратор 44, амплитудноимпульсный модулятор 45 и двойной интегратор 46.

Устройство работает следующим образом.

Для записи речевой или другой информации в устройство совместно с подачей напряжения питания по тактовой шине поступает тактовая частота (фиг. 1). На шину 5 управления режимом работы устройства "Запись/чтение" подключается сигнал логического "0".

При этом происходят соответствующие коммутации и переключения, при которых к входной шине 2 подключается дельта-модулятор-демодулятор 1, выход которого подключается к входу блока 10 памяти. !

Таким образом, устройство готово к восприятию аналоговой информации, преобразованию ее в цифровую дельтаформу и записи ее в блок 10 памяти.

Однако запись информации начинается при поступлении ее в аналоговом виде, если уровень информационного сигнала превышает некоторый порог, величина которого формируется формирователем

2б порогового напряжения. При этом информационная импульсная последовательность речевого сигнала записывается в блок 10 памяти, а информация о длительности информационной импульсной последовательности записыва- ется во второй блок 15 памяти. Паузы между фрагментами речевого сигнала, 734 70 6 исключаются из записи в блок 10 па"

501вательно, в соответствии с двоичными кодами, считываемыми из блока 15 памяти. Таким образом, при считывании речевой сигнал восстанавливается в его первоначальной форме.

55 В режиме записи информации на шине 5 управления устройством "Запись/чтение" сигнал логического "0".

Этот сигнал поступает ня вход управ5

10 t5

45 мяти, если их длительность превышает длительность межслоговой паузы. Последовательно М блок 15 памяти, за записью информации о длительности фрагмента речевого сигнала, записывается информация о длительности паузы, затем снова величина длительности очередного речевого фрагмента и т,д, Таким образом, в блок 10 памяти записываются информационные фрагменты речевого сигнала в дельта-форме, а в блок 15 памяти — последовательно чередующаяся информация о длительности фрагментов речевого сигнала и пауз в двоичном виде. При переполнении памяти запись информапии прекращается.

При считывании информации по шине 5 управления режимом работы устройства "Запись/чтение" поступает сигнал логической 11". В схеме устройства происходят соответствующие коммутации и переключения, при которых к входу тракта аналогового воспроизведения подключается выход дельта-модулятора-демодулятора 1, являющегося при записи информации местным дельта-демодулятором дельта-модулятора. Таким образом, дельта-демодулятор при аналого-цифровом преобразовании используется как местный дельта-демолулятор в цепи обратной связи дельта-модулятора, а при цифроаналоговом преобразовании — как дельта-демодулятор. Это позволяет существенно сократить аппаратурные затраты устройства.

Через мультиплексоры поочередно поступают информационные фрагменты речевого сигнала в виде информационной импульсной последовательности в дельта-форме и генерируемая последовательность ...1010... чередующихся

"1" и "0" соответствующей длительности, записанной в блоке 15.памяти.

Мультиплексор 11 цифрового сигнала управляется от счетного триггера 13, считывающего информацию о длительности речевых фрагментов и пауз последо1573470 ления мультиплексора 17, который под- ключает при этом выход двойного интегратора 46 к входу элемента 41 сравнения, тем самым замыкает цепь обратной связи в схеме дельта-модулятора 1. Тот же сигнал, поступая на вход управления мультиплексора 14 цифровых сигналов, переключает его в положение, при котором выход формирователя 42 информационных сигналов подключается к информационным входам компаратора 43 и амплитудно-импульс ного модулятора 45. Кроме того, логический "0" с шины 5 "Запись/чтение", поступая на вход управления ключевого элемента 4, с его помощью

Подключает на вход тракта воспроизведения аналоговой информации общую шину устройства. Инвертированный инвертором 28 в логическую "1" сигнал

"Запись/чтение", поступая на вход элемента И 9., разрешает прохождеНие цифровой информации с выхода дельта-модулятора 1 на вход блока 10 памяти. Тот же сигнал логической

"1", поступая на вход элемента И 3 1, разрешает восприятие формирователя 39

Импульсов сигнала активности, вырабатываемого компаратором 27. Сигнал

" Запись/чтение" уровня логического

" 0" поступает также на инвертор 29 И переводит его в режим управления записью информации. Таким образом, устройство готово к записи в дельтаформе речевой или другой информации.

Речевой аналоговый сигнал усиливается, поступает на элемент 41 сравнения, где сравнивается с восстановленным значением аналогового сигнала предыдущего такта. Если входной анаЛоговый сигнал больше восстановленного аналогового сигнала, а на выходе элемента 41 сравнения действует сигнал логической "1" формирователь

42 информационных сигналов импульсНой последовательности с тактовой частотой формирует информационную импульсную последовательность входного аналогового сигнала.

Рассматриваемое устройство реализует дельта-модулятор со слоговым компандированием и двойным интегрированием, которая является наиболее эффективной при преобразовании речевых сигналов. При аналого-цифровом и!реобразовании в дельта-форму, дельта-модулятор осуществляет цифровую компрессию, которая практически

10,îñóùåñòâëÿåòñÿ тем же местным дель1

55 осуществляется введением в цепь его обратной связи местного дельта-демодулятора, в котором уровнем AHM и величиной шага квантовая управляет сигнал с уровнем, зависящим от уровня входного сигнала. Цифроаналоговое преобразование при считывании информации в рассматриваемом устройстве та-демоду.-.ятором, поэтому закон компрессии при дельта-модуляции полностью соответствует закону экспандирования при дельта-демодуляции.

Рассмотрим работу местного дельтадемодулятора в составе дельта-модулятора, которая будет аналогичной работе дельта-демодулятора при чтении информации из блока 10 памяти, Компаратор 43 анализирует выходную информацию дельта-последовательность. Если в ней появляется пачка из следующих подряд четырех и более однородных посылок, компаратор 43 вырабатывает импульс, длительность которого равна длительности однородных посыпок в пачке. Тем самым определяется, что компанирование в дельтакодексе ведется по пачкаи однородйых посылок, начиная с четырех таких однотипных посылок. Выделяя пачки из четырех и более однородных посылок, компаратор 43 задерживает их по времени на три тактовых посылки. По мере увеличения крутизны входного сигнала однородные посыпки группируются в пачки, увеличивается число пачек из четырех и более однородных посыпок. Следовательно, увеличивается уровень сигнала на выходе интегратора 44, который на основе выделенных пачек однородных посылок формирует сигнал уровня входного аналогового сигнала. Сформированный сигнал поступает на вход сигнала уровня AHM 45, которым задается величина тока (напряжения) аналого-импульсной модуляции. Следовательно, растет шаг квантования дельта-модуляции. Сигнал с выхода АИМ 45 поступает на двойной интегратор 46, где из сигнала АИМ, в котором заложена информация входного аналогового сигнала, восстанавливается непрерывный аналоговый сигнал, являющийся копией входного аналогового сигнала. Таким образом, осуществляется последовательность: чем больше растет уровень входного аналогового сигнала, тем больше шаг

1573470!

0 квантования, сильнее компрессия дельта-модуляции и экспандирование дельта-модуляции.

Начальный шаг квантования дельтамодуляции с компандированием и двой5 ным интегрированием выбирают с одной стороны как можно меньше, чтобы обес;печить высокую помехозащищенность от 6 шумов квантования при преобразовании

10 сигналов малых амплитуд. С другой стороны он не может быть сколь угодно малым, т.к. начальный шаг квантования должен буть выше флуктуационных шумов в аналоговом канале, чтобы !

5 уверенно обеспечить работу дельтамодулятора 1 при отсутствии речевого сигнала в аналоговом канале ("молчащем" канале), когда цифровая последовательность должна иметь вид ...1010.... Кроме этого на минималь ный (начальный) шаг квантования дельта-модуляции могут оказывать влияние и другие факторы в частности динамический диапазон, который необходимо 25 обеспечить при заданной помехозащищенности.

Для уверенного определения речевого фрагмента или паузы необходимо взять 6 — 8 двоичных символов дельта30 модулированной последовательности.

Анализ речевого фрагмента сводится к определению двух ситуаций: перехода от паузы к речевому фрагменту и перехода от речевого фрагмента к паузе. В первом случае до появления аналогового сигнала фрагмента речи на входе дельта-модулятора 1 последний вырабатывает последовательность чередующихся нулей и единиц ...1010-. соответствующую нулевому сигналу. Компаратор 43 не выделяет пачек однородных посылок, а следовательно, уровень сигнала на выходе интегратора 44 равен нулю. В этой ситуации дельта-модулятор 1 работает с начальным шагом квантования, поэтому при появлении сигнала фрагмента речи он начинает вырабатывать однородные символы "1" или "0" в соответствии с изменением уровня фрагмента сиг50 нала. Следовательно, при появленни после паузы информационного фрагмента на выходе интегратора 44 появляется сигнал, величина которого пропорциональна изменению уровня входного сигнала. Сигнал с выхода интегратора 44 поступает на вход компаратора 27, где сравнивается с пороговым сигналом. поступающим на вход компаратора 27 с выхода формировате« ля 26 порогового напряжения.

При переходе от речевого фрагмента к паузе дельта-модулятор 1 из-за уменьшения уровня сигнала также работает с начальным шагом квантования или шагом квантования, близким к начальному. С началом паузы вырабатывается ДМ-последовательно паузы, поэтому компаратор 43 не выделяет пачки однородных посылок, а следовательно, и сигнал на выходе интегратора 44 уменьшается до нулевого значения. Из этого следует, что порог компаратора

27 необходимо выбирать таким образом, чтобы он был больше сигнала на выходе интегратора 44 при переходе от речевого фрагмента к паузе и меньше сигнала на выходе интегратора 44 при переходе от паузы к речевому фрагменту.

Компаратор 27 сравнивает сигнал уровня, поступающий с выхода интегратора 44. С выхода.компаратора 27 сигнал поступает на вход формирователя 39 импульсов. Находятся в исходном состоянии счетчики 24 и 25 формирования адресов записи, счетный триггер

13. Блок 40 памяти сигналом режима записи (логического "0") включен в прямом направлении на трансляцию выходных сигналов разрядов реверсивного счетчика 24 на шину данных блока 15 памяти. При поступлении первого речевого фрагмента в устройство сиг» . .нал логической "1" с помощью элемента И 37 подключает сигнал тактовой частоты на счетный вход счетчика 24, формирующего на выходах адреса записи речевой информации в блок 10 па-. мяти. Кроме того, сигнал активности логической "1" поступает на вход элемента И 34 на другие входы которого поступают сигналы логической "1н соответственно с выходов инверторов 29 и 30. Сигнал тактовой частоты r.oñòóпает на вход элемента И 34, на остальных входах которого сигналы логических f" поэтому сигнал поступает на блок 10 памяти и является сигналом стробирования записи информации. Формирователь 98 импульсов по передному фронту сигнала активности (перепад напряжения от логического "0 с логической "1") формирует импульс, поступающий на вход элемента И 36. На другой вход элемента И 36 поступает

1573470 сигнал логической "1" с выхода инвер.— тора 29. Следовательно, на выходе элемента И 36 получаем импульс, сформированный формирователем 39 импульсов. Этот импульс, поступая с выхода

5 элемента И 36, является сигналом стробирования записи информации о длительности предшествующей речевому фрагменту паузы в блок 15 памяти, Кроме того, импульс с выхода элемента И 36 через элемент ИЛИ 21 поступает на счетный вход счетчика 25, который при этом на выходах формирует ! сигнал адреса, по которому в блоке

:15 памяти записывается информация

:;о длительности поступившего речево о фрагмента. Импульс с выхода эле" ента И 36 через элемент ИЛИ 19 также поступает на установочный вход ревер-! сивного счетчика 23 и переводит его

le исходное состояние. При этом сигйал тактовой частоты поступает через элемент И 32 на вход суммирования реверсивного счетчика 23, который 25 ра основе этого сигнала формирует нформацию о длительности поступивmего речевого фрагмента. Эта информаЦия с выходов разрядов реверсивного счетчика 23 поступает через блок 40 памяти на блок 15 памяти. Информация о длительности поступившего речевого фрагмента записывается в блок 15 паМяти по заднему фронту сигнала ак тивности, поступающему на формирователь- 39 импульсов. При этом формиро35 ватель 39 импульсов формирует импульс, поступающий через элемент И

36 и стробирующий запись информации

40 рованному на выходе счетчика 25. Тот же импульс, поступая через элемент

ИЛИ 19 на вход установки реверсивного счетчика 23, переводит его в исходное состояние, тем самым обеспечивается начало формирования длительНости поступающей паузы. Кроме того, импульс с выхода элемента И 36 через элемент ИЛИ 21 поступает на счетный вход счетчика 25, который при этом формирует сигнал адреса, по которому

50 в блоке 15 памяти записывается информация о длительности наступающей паузы. Таким образом, в режиме записи информации формирователь 39 импульсов, как по переднему, так и по заднему фронтам сигнала активности речевого фрагмента, формирует импульсы, которые, поступая на вход элемента И 36 и на блок 15 памяти, стробируют запись информации о длительности речевого фрагмента или паузы.

В паузах при записи информации сигнал активности на входе формирователя 39 импульсов соответствует логическому "0". Поэтому элементом И

34 отключается сигнал стробирования записи информационной-импульсной последовательности в блок 10 памяти.

Элемент И 37 отключает подачу сигнала тактовой частоты на счетный вход счетчика 24, тем самым прекращается выработка сигнала адреса записи в блок 10 памяти.

Окончание записи при переполнении памяти, как правило, наступает, когда переполняется объем памяти блока

10 памяти, так как объем записываемой информации в блок 15 памяти невелик. При этом на вход инвертора 30 поступает сигнал логической " 1", который им преобразуется в сигнал логическоо "0" Этот сигнал поступает на вход элемента И 34 и отключает сигнал стробирования записи информации в блок 10 памяти.

В режиме считывания информации на вход инвертора 29 поступает сигнал логической "1", который, поступая на вход элемента И 33, обеспечивает подключение сигнала тактовой частоты к входу вычитания реверсивного счетчика 23, поступая на второй вход элемента И 35, обеспечивает передачу сигнала с выхода переноса реверсивного счетчика 23 на тактовый вход счетчика 25 и через элементы И 35 и .ИЛИ 21. Кроме того, этот сигнал поступает на вход управления блока

40 памяти и переключает его на трансляцию сигналов шины данных на информационные входы реверсивного двоичного счетчика 23. В соответствии с адресом, сформированным счетчиком 25, на информационные входы реверсивного счетчика 23 через блок

40 памяти поступает информация из шины данных о длительности речевого фрагмента или паузы, причем последовательность записи, пауза, фрагмент, обеспечиваются последовательностью формирования адреса счетчиком 25.

Каждый раз при пересчете длительности паузы или речевого фрагмента на выходе .сигнала переноса реверсивного счетчика 23 появляется импульс, который, поступая через элементы И

14

Формула изобретения

Устройство для цифровой записивоспроизведения речевой информации, содержащее дельта-модулятор-демодулятор, подключенный первым аналоговым входом к входной шине, синхронизирующим входом — к шине синхронизации, аналоговым выходом — к входу первого ключевого элемента, подсоединенного управляющим входом к шине управления и выходом через последовательно соединенные фильтр нижних чаетот и усилитель к выходной шине, цифровым выходом через первый элемент И вЂ” к входу первого блока памяти, подключенного первым выходом к первому входу первого мультиплексора, соединенного вторым входом через генератор кода паузы с ниной синхро35

45

50 низации, управляющим входом — с выходом счетного триггера и выходом с первым входом второго мультиплексора, подключенного вторым входом к цифровому выходу дельта-модуляторадемодулятора, управляющим входом— к шине управления и выходом к цифро- вому входу дельта-модулятора-демоду55

35 и ИЛИ 21 на счетный вход счетчика 25, обеспечивает формирование

6 следующего адреса. Кроме того, .поступая на вход счетного триггера 15, 5 он меняет состояние сигналов на его выходах. Причем речевому фрагменту

1! It соответствует сигнал логического 0 на прямом выходе счетного триггера

15 и соответственно логической "1" на инверсном выходе. При паузе сигналы на выходах счетного триггера 13 обратные. Тем самым сигналом логической " 1" при речевом фрагменте, поступающим через элемент ИЛИ 22 на вход 15 элемента И 37, обеспечивается подключение сигнала тактовой частоты к счетному входу счетчика 24. Последний при этом формирует сигнал- адреса для считывания информации из блока

10 памяти. Сигнал с прямого выхода счетного триггера 13 поступает на вход управления мультиплексора 11.

При считывании речевых фрагментов (сигнал на управляющем входе мульти- 25 плексора 11 логический "0") сигнал с выхода блока 20 памяти подключается через мультиплексоры 11 и 14 цифровых сигналов на входы элементов местного дельта-демодулятора 1. 30 лятора, второй блок памяти, второй ключевой элемент, второй элемент И, третий мельтиппексор, первый элемент

ИЛИ и первый, второй и третий счетчики, о т л и ч а ю щ е е с я тем, что, с целью снижения погрешности записи-воспроизведения речевой инфор мации, в него введены формирователь порогового напряжения, компаратор, первый, второй и третий инверторы, второй, третий, четвертый и пятый элементы ИЛИ, третий, четвертый, пятый, шестой, седьмой и восьмой элементы И, первый и второй формирователи импульсов и третий блок памяти, причем формирователь порогового на-,,пряжения подключен выходом к первому, входу компаратора, соединенного вторым входом с управляющим выходом дельта-модулятора-демодулятора и выходом с первым входом второго элемента И, подсоединенного вторым входом к соединенным между собой соот" ветствующему входу первого элемента

И и выходу первого инвертора, подключенного входом к управляющей шине, первому входу четвертого элемента И, первому входу шестого элемента И, управляющему входу третьего блока памяти и через второй инвертор к соединенным между собой первым входам третьего, пятого и седьмого элементов И и входу первого формирователя импульсов, подсоединенного выходом к соединенным между собой установочному входу счетного триггера и первому входу третьего элемента

ИЛИ, подключенного вторым входом к выходу второго ключевого элемента и первому входу второго элемента ИЛИ и выходом к установочным входам второго и третьего счетчиков, соединенных выходами с адресными входами первого и второго блоков памяти и входами с выходами соответственно восьмого элемента И и четвертого элемента ИЛИ, последний из которых подклюЧен первым входом к соединенным между собой входам разрешения первого счетчика, соединенного установочным входом с выходом второго элемента ИЛИ, входами и выходами — с выходами и входами третьего блока памяти, а сум-. мирующим и вычитающим входами - с выходами соответственно третьего и четвертого элементов И, к выходу шестого элемента И, подсоединенного вторым входом к входу счетного триг1573470

1б

Составитель 10.Алешин

Техред Л.Сердюкова Корректор С.Шекмар

Редактор Н.Лазаренко

Заказ 1644 Тираж 486 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

11 ll

Производственно-издательский комбинат Патент, г.ужгород, ул. Гагарина,101 гера и выходу переноса первого счетчика, и подключен вторым входом к управляющему входу второго блока паМяти, второму входу второго элемента

ИЛИ и выходу седьмого элемента,И, подсоединенного вторым входом к выходу второго формирователя импульсов, подключенного входом к соединенным между собой выходу второго элемента

И, второму входу пятого элемента И, Подсоединенного выходом к управляющеМу входу первого блока памяти, и к

Первому входу пятого элемента ИЛИ, соединенного вторым входом с инверсйым выходом счетного триггера и выходом с первым входом восьмого элеМента И, подключенного вторым входом

ic третьему входу пятого элемента И, вторым входам третьего и четвертого элементов И и шине .синхронизации, при этом третий блок памяти соединен

5 шиной данных с шиной данных второго блока памяти, первый элемент ИЛИ подключен первым входом к выходу второго блока памяти, вторым входом — к второму входу первого блока памяти и выходом через третий инвертор — к четвертому входу пятого элемента И, а третий мультиплексор подключен выходом к второму аналоговому входу дельта-модулятора-демодулятора, управляюшим входом — к шине управления, первым входом — к аналоговому выходу дельта-модулятора-демодулятора, а вторым входом — к входной шине,