Устройство контроля качества канала связи

Иллюстрации

Показать всеРеферат

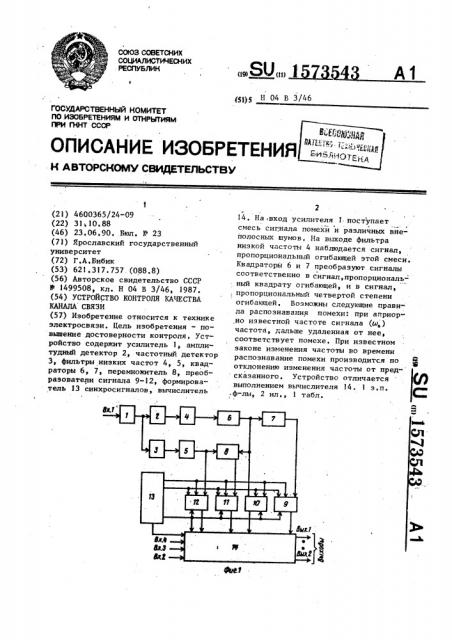

Изобретение относится к технике электросвязи. Цель изобретения - повышение достоверности контроля. Устройство содержит усилитель 1, амплитудный детектор 2, частотный детектор 3, фильтры низких частот 4, 5, квадраторы 6, 7, перемножитель 8, преобразователи сигнала 9 - 12, формирователь 13 синхросигналов, вычислитель 14. На вход усилителя 1 поступает смесь сигнала помехи и различных внеполосных шумов. На выходе фильтра низкой частоты 4 наблюдается сигнал, пропорциональный огибающей этой смеси. Квадраторы 6 и 7 преобразуют сигналы соответственно в сигнал, пропорциональный квадрату огибающей, и в сигнал пропорциональный четвертой степени огибающей. При априорно известной частоте сигнала (ω<SB POS="POST">0</SB>) частота, дальше удаленная от нее, соответствует помехе. При известном законе изменения частоты во времени распознавания помехи производится по отклонению изменения частоты от предсказанного. Устройство отличается выполнением вычислителя 14. 1 с.п. ф-лы. 2 з.п. ф-лы. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (!9) (!!) щ)5 Н 04 В 3/46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

- К А ВТОРСКОМЪ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

flO .ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

flPH ГКНТ СССР

f (21) 4600365/24-09 (22) 31;10.88 (46) 23.06.90. Бюл. Г 23 (71) Ярославский государственный университет (72) Г.А.Бибик (53) 621.317.757 (088.8) (56) Авторское свидетельство СССР

У 1499508, кл. Н 04 B 3/46, 1987. (54) УСТРОЙСТВО КОНТРОЛЯ КАЧЕСТВА

КАНАЛА СВЯЗИ (57) Изобретение относится к технике электросвязи. Цель изобретения — повышение достоверности контроля. Устройство содержит усилитель I амплитудный детектор 2, частотный детектор

3, фильтры низких частот 4, 5, квадраторы 6, 7, перемножитель 8, преобразователи сигнала 9-12, формирователь 13 синхросигналов, вычислитель

14. На вход усилителя 1 поступает смесь сигнала помехи и различных внеполосных шумов. На выходе фильтра низкой частоты 4 наблюдается сигнал, пропорциональный огибающей этой смеси.

Квадраторы 6 и 7 преобразуют сигналы соответственно в снгнал,пропорциональныи квадрату огибающей, и в сигнал,, пропорциональный четвертой степени огибающей. Возможны следующие правила распознавания помехи: при априор.но известной частоте сигнала {(о,) частота, дальше удаленная от нее, соответствует помехе. При известном законе изменения частоты во времени распознавание помехи производится по В отклонению изменения частоты от пред- сказанного. Устройство отличается выполнением вычислителя !4. 1 з.п. .ф-лы, 2 ил., 1 табл.

1573543

30

Изобретение относится к технике электросвязи и может использоваться

В системах связи для контроля качества

Каналов связи, а также для контроля

5 частоты принимаемого сигнала и ее изменений при пассивных и организованных помехах, а также при многолучевом распространении сигналов.

Цель изобретения — повьппение достоверности контроля.

На фиг.1 представлена структурная электрическая схема предлагаемого устройства; на фиг.2 — вычислитель.

Устройство контроля. качества кана- 5

Йа связи содержит. усилитель 1, амппи удный детектор 2, частотный детектор первый 4 и второй 5 .фильтры низких частот» первый 6 и второй 7 квадрато1»ы»,перемножитель 8, первый 9, второй 20

10». третий 11 и четвертый 12 преоб »азователи сигнала, формирователь 13 синхроснгналов и вычислитель 14, Вычислитель 14 содержит (фиг.2) восемнадцать регистров 15-32, блок 33 25 регистров, первый 34 и второй 35 триггеры, элемент ИЛИ-НЕ 36, семь мультиплексоров 37-43, первый 44, второй

45 и третий 46 блоки вентилей, блок

47 умножения, блок 48 сложения, блок

49 извлечения квадратного корня, блок 50 деления, блок 51 анализа, первый 52 и второй 53 сдвигатели и блок 54 управления.

Устройство работает следующим об- 35 разом.

На вход устройства (на вход усилителя 1) поступает смесь сигнала, помехи и различных внеполосных шумов * А,сов((hatt + q„(t)g + A1cosfu1t+

+ p,(Ц+5 (1) где А, cu,» q,(t) †огибающая, частота и.фаза сигнала; 45

Чг() - огибающая, часто1» та и фаза помехи; ф " внеполосной шум.

Усилитель 1 усиливает эту смесь и отфильтровывает внеполоснои шум 50

Частотный детектор 3 и второй фильтр

5 низкой частоты выдают сигнал, про- . порциональный частоте поступающей смеси полезного сигнала и помехи, а амплитудный детектор 2 и первый фильтр 4 низкой частоты — сигнал, про55 порциональный огибающей этой смеси.

Первый 4 и второй 5 фильтры низкой частоты отфильтровывают высокочастотные продукты амплитудного и частотного детектирования. Первый квадратор

6 преобразует сигнал, пропорциональный огибающей, поступающий .на его вход с выхода первого фильтра 4 низкой частоты, в сигнал, пропорциональный квадрату огибающей.. Известно, что частота смеси двух сигналов определяется по формуле

1 1

41 g A g + (б 1 А 1 + А А 1 (С +

А „+ A 1 + 2А,А1cos Гм — cu ) t +.

+ 1)cos ((<- )t + <ч(Щ

+ d g(t)g (6) а квадрат огибающей — по формуле

А = Аг + Аг + 2А А гсоs ((4) — (de) t+

+ >v(t)7» (3) где

ay(t) = (1 (t) — Ч,(t) °

Второй квадратор 7 преобразует сигнал {А„), пропорциональный квадраг ту огибающей (А ), поступающий на его вход с выхода первого квадратора 6, в сигнал (А „ ), пропорциональный чето вертой степени огибающей (А4 ), где

А = (А, + Аг) + 4А,А сое ((со1— — Ы, ) t + д сг() ) + 4А,А1(А,+A1) cos p (ю — см,) t + д q(t)) - (4)

Перемножитель 8 преобразует сигналы {м„» А, ), поступающие на его вхо Z ды, пропорциональные частоте (с выхода второго фильтра 5 низкой частоты) и квадрату огибающей {с выхода первого квадратора 6), в сигнал

{А ы>)„, пропорциональппй их произве2 дению

А СО = СО,А, + (о1А1 + А,А1(с ., +

+ы1)сов ((со1- м, ) t + dg.(t)g . (5) (A1tu) „, A» A4), пропорциональные соответственно час" тоте (2), произведению квадрата огибающей на частоту (5), квадрату огибающей (3), четвертой степени огибающей (4), поступают соответственно с выходов второго фильтра 5 низкой частоты, перемножителя 8, первого квадратора 6, второго квадратора 7 соответственно на входы четвертого 12, третьего 11, второго 10 ипервого 9 преобразователей сигналов, которые выделяют из поступающих сигналов постоянные составляющие. Это соответсч — . вует операции усреднения по времени.

Обозначая эту операцию чертой сверху обозначения сигнала, записывают результат,усреднения соотношений (3) (5)

Г1 1 2

А =А„+А1 =а;

5 1573543

Агс = сд Аг +. ы А. где (8)

По расчетным; соотношениям () О), F = 2АА». (9) 5 (14), (15) (13) и значениям сигналов

При Усреднении Учтено, что сигнал - (Аг „) Аг А4 (пропорциональным

1 и ° и помеха являются сигналами с угловой

Ф модуляцией, огибающие которых постоян- соответственно у, А с, А, А ), постуны, по крайней мере на длительности лающим с выходов всех преобразоватеусреднения. 10 лей 12-9 сигналов, вычислитель )4

Средняя частота смеси двух сигна- определяет значения M z р. Вылов является частотой сигнала с боль- дача ы,, мг обеспечивает поиск и шей огибающей. Если А,)Аг,,тогда слежение за частотами сигнала и помехи, в многоканальной линии для опре1. (10) )5 деления канала сигнала и канала помеПри равенстве огибающих (А = А г) хи (пораженного канала). Выдача р соотношение ()0) не выполняется. В определяет качество линии связи. Одэтом слУчае частота смеси Равна полУ- ьако в данном случае как и в иэ" у сумме частот обоих сигналов, что вид- вестных устройствах, выдается отношено непосредственно из формулы (2), ние меньшей мощности к большей. При

Но это изолированнаЯ особаЯ точка и пРи этом считывается, что помеха имеет любом незначительном отклонении от меньшую мощность и это отношение ()5) равенства огибающих соотношение (10) выдается за отношение мощности помехи выполнЯетсЯ, Если Учесть, что УсРеДне- к мощности сигна а.. Однако в ряде ние длится продолжительное вРемя (от- 25 линий связи (помехопостановщик — посчеты берутся чеРез единицы, десятки движен, или имеет мощный передатчик, . секУнД), взаимное Расположение источ- или.близко расположен к приемной станника сигнала и помехопостановщика слуции, или связь производится может менЯтьсЯ (есликто-ни- движными объектами на пределе энергебУДь изних или обаподвижные)и моЩно-- 30 тики линии) отношение мощностей помести излучаемых ими сигналов независихи и сигнала может с равной вероятмые то возможное иногда случайное ностью принимать любое значение в инравенство огибающих сигналаи помехи тервале -чи, +чи/ дБ. В этом слуне можетдлиться продолжительное время чае нужны дополнительныеьсведения, чеи тем самым существенно повлиять йа ге та

35 му в действительности отношение (-5) величину определяемой средней чассоответствует (отношению помеха/сигтоты. нал или сигнал/помеха). При структуроподобной (ретранслированной) помеются А, А через а, Р которые в . хе только частота, а при равенстве свою очередь, из системь! уравнений gp частот сигнала и помехи только ее (6) и (7) определяются через средние изменения дают возможность распоэназначения квадрата и четвертой степев ать помеху. ни огибающей

Возможны следующие правила расА = - А + 2F + А — ) 2F (1)) познавания помехи, 2(45 1. При априорно известной частоте

1(,/-4 à — - /-т у - сигнала (Ю ) частота, дальше удален2 ) ная от нее, соответствует помехе.

Для этого вычислитель 14 производит

l и операции

Подставляя (10) — (12) в (8), полу- M 1= д — o (16) чают Duz= юг — <>, (17)

А <-(d А 4(.= )a ) t 14 г! (18)

Лн - : 1Р Частоте Ы,=- и соответствует большая огибающая, значит, если

Учитывая, что на практике интере-0 . (19)

55 du>(а, суются не самими значениями сигнала полученное по формуле (15) отношение и помехи, а отношением их мощностей, соответствует отношению мощностей записывают расчетное соотношение для помеха сигнал, если соотношение (19) чего не выполняется, полученное отношение (15) (14) 1573543 (15) дает отношение мощностей сигнал/помеха, При известном законе изменения частоты во времени (обе станции приемная и передающая неподвижны - отсутствует доплеровское смещение частоты, или одна из станций или обе подвижны, но известно их взаимное перемещение, т.е. может быть предсказано изменение 10, частоты принимаемого сигнала) распознавание помехи производится по отклонению изменения частоты от предсказанного (D ). Для этого вычислитель

14 производит следующие операции: (. запоминает значения частот (M„ 4/z),, полученные в предьдущем цикле измерений (соответственно bJ (d ), и вы1р числяет

1 1 11 4 1) з (20) 0

Bz = (dt- май>, (21)

401 = 01 По1 (22) (23)

4D 1 4D„ I - 1dDq 1. (24)

Если 25 дп (О 1 25 1 полученное по формуле 15 отношение соответствует отношению мощностей помеха/сигнал, если же соотношение (25) не выполняется, полученное отношение (15) дает отношение мощностей сигнал/ 30 помеха.

С соответствующих выходов вычислителя 14 вьдаются"значения соответственно о,, ы, D D которые позволяют отслеживать частоты сигнала и 35 помехи и величины их изменений эа время одного цикла измерения, Для определения надежности распознавания помехи по частоте или ее сдвигу с других выходов вычислителя 14 выдают- 40 ся значения д11, dD, Кроме того, выдается сигнал, показывающий, Что выдается с определенного выхода вычислителя 14 (р) отношение помеха/ сигнал или наоборот сигнал/помеха. 5

На информационные входы всех преобразователей 12-9 сигналов поступают

1 4 сигналы, не равные со, А и, А, А а пропорциональные им (ж„, (А ul) II, 50

А„, A„). Можно на их выходе получить истинное значение измеряемых сигналов, поставив в этих блоках нормирующие усилители. Однако удобнее нормирование проводить в вычислителе 14. Для

55 этого на третий вход вычислителя 14 подаются константы нормирования (К, К К К ) и с,1„ D а на четвертый

Si Ôi 1 о вход — сигналы, синхрониэирующие их прием. Для распознавания сигнала, помехи необходимо указать по какому параметру (Р., 01, .аи, d D) производится:распознавание. Код параметра поступает через второй вход вычислителя 14.

После включений устройства тактовые импульсы поступают постоянно с четвертого выхода формирователя 13 синхросигналов на первый вход блока

54 управления (nepII61i вход вычислителя 14), содержащего счетчики набор дешифраторов, онределякпцих время начала и длительность соответствующих управляющих сигналов (Z) — Z 20).

Б качестве тактовых сигналов (Т) блок

54 выдает непосредственно сигналы формирователя 13, однако возможно такое построение блока 54; когда он генерирует собственные импульсы, синхронизированные с тактовыми импульсами формирователя 13. После сигнала пуска начинается цикл вычислений (сигнал пуска обнуляет счетчик блока 54), последовательность операций которых приведена в таблице, где указан номер операции, выполняемой данн61м блоком; порядковый номер операции; операция; откуда взяты операнды; куда помещается результат операции; управляющие сигналы мультиплексоров (в скобках указан номер кода, который совпадает с номером входа, который по данному сигналу подключается к выходу), пропускающие oIIeранды на соответствующие входы блоков для проведения данной операции; сигналы, в течение которых происходит данная операция, управляющие сигналы, по которым происходит. запоминание результатов операции, Последовательность операций выбрана такой, чтобы максимально распараллелить работу блоков. В операциях 1, 2„ 7 и . 14 происходит нормирование сигналов, поступающих из преобразователей сигнала 9, 10,12 и Il посредством умножения их на l коэффициенты К 1 У«1

К, в блоке 47 умножения.

Кроме нормирования входных сигналов (операции 1, 2, 7 и 14) блок

47 возводит в квадрат нормированный сигнал Az (операция 3) и производит умножение двух нормированных сигналов А и со, (операция 13). Результаты умножений запоминаются первым

15, вторым 1Ü, третьим 17, четвертым

18 и пятым 19 регистрами по сигналам

Z3,,Z1О,,Z18,,Z 5., Z 4, последовательность которых указана в таблице. С этих регистров 15-19 операнды через третий 39 и четвертый 40 мультиплексоры поступают на блок 48 сложения (комбинационный сумматор, возможно использование схемы ускорения переносов). EIa третий его вход 48 (вход переноса в младший разряд) подается во время операций вычитания сигнал 2 7 в .качестве единицы младшего разряда, являющийся поправкой при представлении дополнительного кода, вычитаемого через инверсный код.

В четверттой операции блок 48 определяет значение Г, а в пятой операции — подкоренное выражение соотношений 14 и 15 — результат, который выдается на блок 49 извлечения квадратного корня, где он и запоминается.

Вычисления блоком 49 производятся во время сигнала Z 9, а результат в инверсном и прямом коде поступает соответственно на седьмой и восьмой входы третьего мультиплексора 39 и используется блоком 48 в операциях 16 и 18.для определения числителя и знаменателя формулы (15). Поскольку операция извлечения корня длительная, то во время этой операции блок 47 умножения нормализует значения ы

А си (операции 7, 14) и производит умножение А х ы,(операция 13), а — z блок.48 сложения определяет отклонение частоты м, от предсказанной a)o согласно. соотношения (16) (операция

8) и определяет модуль этого отклонения (операция 9), а также определяет изменение частоты N за период

1 измерения (операция 10), отклонение этого изменения от пресказанного (операция 11) согласно соотношений (20), (22) и модуль этого отклонения (операция 12), а также вычисляет чис- литель второго члена соотношения (14). Модуль результатов операций блока 48 сложения (операции 9, 12, 22, 26) определяется на этом же блоке.

Для,этого седьмой мультиплексор 43 пропускает с шестого регистра 20 на четвертый вход третьего мультиплексора ЗО операнд в прямом или инверсном коде в зависимости от знакового разряда операнда, поступающего с третьего выхода шестого регистра 20 на управляющий вход седьмого мультиплексора 43 и четвертый вход четвер73543 10 того мультиплексора 40. Если операнд положителен (знаковый разряд О), он в прямом коде проходит седьмой 43 и третий 39 мультиплексоры, блок 48 и запоминается в шестом регистре 20, Если операнд отрицателен (знаковый разряд 1), он в инверсном коде про- . ходит седьмой 43 и третий 39 мультиплексоры на первый вход блока 48, а на второй вход блока 48 через четвертый мультиплексор 40 поступает знаковый разряд в качестве младшего разряда блока 48. После вычисления в последнем числителя (операция 15) и знаменателя (операция 16) второго члена соотношения (14) они поступают соответственно с шестого и восьмого регистров 20 и 22 через пятый 41 и

20 шестой 42 мультиплексоры на первый и второй входы (делимого и делителя) .блока 50 деления.

В обеих операциях деления (операции 17 и 20) операнды положительны, 25 поэтому знак не учитывается и делимое всегда меньше делимого. После деления (операция 17) блок 48 опреде" ляет со согласно соотношения (14), при этом умножение результата деления

З0 на коэффициент 2 осуществляется первым сдвигателеи 52 sa счет сдвига

- разрядов на один разряд влево. Первый

52 и второй 53 сдвигатели могут отсутствовать, а сдвиг на один разряд

35 в этом случае осуществляется при монтаже соединений проводов, соединяющих выходы шестого регистра 20, блока 50 соответственно с вторым, девятым входами четвертого мульти4 плексора 40, Во время операции 17 деления блок 48 определяет знаменатель соотношения (15) (операция 18), поэтому с восьмого 22 и шестого 20 регистров ., поступают результаты опе»

5 раций 16 и 18 на регистры делимого и делителя блока 50. Результат деления (операция 20) поступает через третий блок 46 вентилей на первый информационный вход четырнадцатого регистра 0 28,(Во время операции деления (операция 20) блок 48 выполняет операции

21-27 согласно соотношений (17), ()8), (21), (23) и (24). Результаты вычислений (ы,, со, D р, дю, с1Р, D,) выдаются с первых прямых выходов соответствующих регистров 17, 26-.31. !

С выхода восемнадцатого регистра

32 (вых.8) выдается сигнал — при157

3543

2О

11 знак, что больше сигнал или помеха, On полезен сам по себе, так как грубО оценивает помеху относительно сигнала, но в основном служит индикатором, что выдается на выходе четырнадцатого регистра 28 " отношение помеха/сигнал или наоборот сигнал/ пЬмеха. Этот сигнал - признак распоз авания формируется в блоке 51 ана" лйза, на вход которого поступают оперынды,. соответствующие величинам дф, Л, dD, D„. В простейшем случае блок 51 — это мультиплексор, который вь дает на выход по коду управления, пЬступающему на пятый вход блока (х.2), знак любого из операндов .

Возможны и более сложные комбинации из указанных операндов — это зависит о исходных данных для анализа. В и остейшем случае, когда анализируетс знак какого-либо из операндов в ! блоке 51, восемнадцатый регистр 32 манжет быть заменен триггером, Исходя из работы алгоритма возможны два исключения, Это когда F или пфдкоренное выражение (а < c О) отрицательны. Физически это означает, что кЬгда.помеха значительно меньше анпаратурных шумов или ее совсем нет, тогда Р 4 О (а 4(0), а когда огибающйе сигнала и помехи равны или их разность меньше аппаратурных шумов, то подкоренное выражение меньше или р@вно нулю (а < = (Az) -2Г CO), Оба эти случая выявляются путем анализа знакового разряда этих операндов (4, а ), который поступает с третьегО выхода шестого регистра 20 на информационные входы первого 34 и второго 35 триггеров и запоминается ими по сигналам Z.19, Z 20, поступающим на их управляющие входы с блока

54. Если знак отрицательного числа выражается логической единицей (нулем), то с прямых (инверсных) выходов первого 34 и второго 35 триггеров сигналы поступают соответственно на первый и второй входы элементов ИЛИHI. :Зб.и запрещают прохождение сигналов через первый 44, второй 45 и третий 46 блоки вентилей на информацион- ные входы двенадцатого 26 и тринадцатого 27 регистров и первый информацйоиный Bxop,÷åòûðíaäöàòîão регистра

28, на второй информационный вход которого поступает сигнал с второго триггера 35 ° По сигналу Z 18 двенадцатый 26 и.тринадцатый 27 регистры обнуляются, а в четырнадцатом регистре 28 запоминается лишь разряд знака операнда, поступающий с второго триггера 35, который можно рассматривать как значение р = 1, поскольку вычисленное по соотношению (15) значение р 1 Обнуление соответствующих регистров 26-28 при а CO означает, что при отсутствии помехи отсутствует ее частота (со ), изменение частоты (D ) и огибающая (р = 0). Когда огибающие помехи и сигналы равны (аз О), wz, Dz по указачному алгоритму не определяются a p = 1, что служит индикацией данного случая. Первый 44, второй 45 и третий 46 блоки вентилей в простейшем случае — это наборы элементов И с двумя входами, первый вход управляющий и соединен с выходом элемента KIH-HE а второй вход — информационный для соответствующего разряда, поступающего на блок операнда, Все мультиплексоры 37-43 управляются,сигнала с выхода блока 54 управления, Формула изобретения

1, Устройство контроля качества канала связи, содержащее вычислитель, выходы которого являются выходами устройства, формирователь синхросигналов, первый выход которого подключен к первому входу вычислителя, последовательно соединенные амплитудный детектор, первый фильтр низкой частоты, первый квадратор, второй квадратор и первый преобразователь сигнала, выход которого соединен с девятым входом вычислителя, второй преобразователь сигнала, вход и выход которого соединены соответственно с выходом первого квадратора и восьмым входом вычислителя,. второй выход формирователя синхросигналов подключен к первому управляющему входу первого преобразователя сигнала, а третий и четвертый выходы формирователя синхросигналов соединены соответственно с вторым и третьим управляющими входами второго преобразователя сигнала, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности контроля, введены последовательно соединенные усилитель, вход которого является первым входом устройства, частотный детектор, второй фильтр низкой частоты, перемножи14

1573543

13 тель и третий преобразователь сигнала, выход которого соединен с седьмым входом вычислителя, четвертый цреоГразователь сигнала, вход и выход. которого соединены соответственно с выходом второго фильтра низкой частоты и шестым входом вычислителя, выход усилителя подключен также к входу амплитудного детектора, выход первого квадратора подключен к второму входу перемножителя, второй выход формирователя синхросигналов соединен с первыми управляющими входами .второго, третьего и четвертого преобразователей сигнала и пятым входом вычислителя, третий и четвертый выходы формирователя синхросигналов соединены соответственно с вторыми и третьими управляющими входами перво- 20

ro, третьего и четвертого преобразо, вателей сигнала, причем второй, третий и четвертый входы вычислителя

; являются соответственно вторым, тре; тьим и четвертьм входами устройства. 25

2, Устройство по п.1, о т л и— ч а ю щ е е с я теи, что вычислитель содержит последовательно соединенные первый мультиплексор, блок умножения,.первый регистр, третий мультиплексор, блок сложения и шестой регистр, первый выход которого соединен с первыми входами пятого и седьмого мультиплексоров, вторьм вхо- дом шестого мультиплексора, шестым и тринадцатым входами третьего мультиплексора, а второй выход шестого регистра соединен с вторьм входом седьмого мультиплексора, одиннадца тым и четырнадцатым входами третьего мультиплексора непосредственно и через второй сдвигатель с вторым входом четвертого мультиплексора, четвертый вход котороro соединен с входаии первого и второго триггеров, тре- 4S тьим выходом шестого регистра и управляющим входом седьмого мультиплексора, выход которого соединен с четвертыи входом третьего мультиплексора, третий, IIHTblII и девятый входы которого соединены с входои третьего регистра, пятьм входом первого мультиплексора и выходом второго регистра вход которого соединен с входами четвертого и пятого регистров и выходом блока умножения, второй вход

I которого соединен с выходом второго мультиплексора, пятыи вход которого соединен с выходом пятого регистра, седьмьм и восьмым входами четвертого мультиплексора, а первый, второй, четвертый и шестой входы соедйнены

I соответственно с первьм, вторым, третьим и четвертым выходами блока регистров, пятый выход которого соединен с третьим и десятьм входами четвертого мультиплексора, шестой и тринадцатый входы которого соединены с шестым выходом блока регистров, второй и первый входы которого являются соответственно четвертым и третьим входами вычислителя, шестой, седьмой, восьмой и девятый входы которого являются соответственно четвертым, шестым, вторым и первьм входаии первого мультиплексора, третий вход которого соединен с третьим входом второго мультиплексора, вто-. рым входом третьего мультиплексора и первым выходом четвертого регистра, второй выход которого соединен с первым входом четвертого мультиплексора, выход которого соединен с вторым входом блока сложения, выход ко-.

1 торого соединен с входами седьмого, восьмого, девятого, десятого и одиннадцатого регистров и входом блока извлечения квадратного корня, первый и второй выходы которого соединены соответственно с восьмым и седьмым входами третьего мультиплексора, десятый и двенадцатый входы которого соединены с выходом седьмого регистра и входом первого блока вентилей, выход которого соединен с входом двенадцатого регистра, второй выход которого соединен с двенадцатым входом четвертого мультиплексора, пятый вход которого соединен с вторым выходом третьего регистра, а девятый вход через первый сдвигатель соединен с входом третьего блока вентилей и выходом блока деления, первый и второй входы которого соединены соответственно с выходом пятого и шестого мультиплексоров, второй вход пятого и первый вход шестого мультиплексоров соединены с выходом восьмого регистра, вторым входом блока анализа и входом второго блока вентилей, выход которого соединен .с входом тринадцатого регистра, первый вход четырнадцатого регистра соединен с выходом третьего блока вентилей, а второй вход четырнадцатого регистра соединен с выходом второго триггера и вторым входом элемента ИПИ-НЕ, пер157354 вый вход которого соединен с выходом первого триггера, а выход элемента

ИЛИ-НЕ соединен с управляющими входами первого, второго и третьего блоКов вентилей, первый вход блока анализа соединен с выходом девятого регистра, входом пятнадцатого регистра одиннадцатым входом четвертого мультиплексора, четырнадцатый вход

1 оторого..соединен с выходом десятого егистра, входом шестнадцатого региста и третьим входом блока анализа,, етвертый вход которого соединен с выходом одиннадцатого регистра и вхо22ом семнадцатого регистра, а выкод лока анализа еоединен с входом воемнадцатого регистра, при этом пятый ход блока анализа..является вторьй) ходом вьяислителя, первый и пятый 2О входы которого являются соответственl ! ио первым и вторым входами блока управления, а первый, второй, третий, четвертый, пятый, шестой,, седьмой и восьмой выходы вычислителя являются . 25 первыми выходами соответственно трет ьего, двенадцатого, тринадцатого, «.В

Операция, >1ыполняемая данным блоком ! !

Порядковый номер операции

Подкоренное выракеиие

Операнд, Вяятый нз блока

Ревультат операции, помещвемый в блок

Управляющий сигнал мультиплексора

Сигнал> в течение которого происходит данная информация

Управляющий сигнал, по которому происходит вапомннание результатов операции

19 !8

18

49

49

16 го гз

25, 20

Z1 ())

Z 1 (2)

2 1 (3)

Е6 (1)

2 6 (2) lх

2л

Зх

1+

2+

)У

4х э+

4+

5+

1

2 з

5

7

9 ! о

Зэ, 37

ЗЗ, 37 !

15, 18 !

8, 20

49

Зэ, 37

16, 33

16„) 7

20, 33, Z 2

Z 2

Z 2

27

Z7

2 9

z2

Z 7

ЕЗ

Z4> 25

zs

Z 8

Z 9

29

Z !О ze

z )!

z)2,ze

2 8

Z 1 (4)

Е 6 (3)

Z 6 (4)

26 (5)

Е6 (6) 2 7

2 7

7+

5л

6х

12

l3

14

24

18

2 6 (4)

Z ) (5)

Z 1 (6) 20

19, )6

ЗЗ, 37 г 13

2 5

2 3

2 2.

Е 6 ()) 15, 18

Z 7

l6

Е )4!

9, 49

20, 22

2 6 (7)

Z 15 (l ) г 7,I 7

z 36

Е 16!

Е 6 (8)

Е 6 (9)

Е 15 (2) 20

19, 49

l 6 50

22, 20

Z 8 г 17

Е 16

20 а„

28 г 18

21, 33

23, 20

a s> а „- в>> ь>1- ь>,аь>,! а ) )а>)т) а и вв a ts «)М1-)s">s) = o,îi ат а Ш1 »

° »>1 - 1" 1З )>1

21

22

12+

)э+

14+

Е 6 (10)

Е 6 (4) г 6 (11) 20

Z7

z 8 г 8

Z l l

Z 7

21, 26 22, 20. Z 6 (12) 2 7

l5+

24 г!4,ze а К яaaA7

1 1 в «К >А»»Аг е t » а - в > аа «(А ) а в а -а «А-(А)»F

Ф t sv ау а2ла,> А -2Р

as les ()1 — 2F

as Rs >>„>»»ь>> а as - о> «о> -t» dt»

° 1 > а lail » Id)d>l

S а„a,-< ) ЭЬ, - D>» D1 - Do»

dD„, а>1» а>1 l ldD а>> «а! в, » А си, а«Rs s(A «) „«А > > . - A >

- « Р)+=.2)1 а>в а «

>1 В

>> а, ат+ а4 А +

+ ((А"-) - 2)> а»»в,+а >а,„о> .)) . р в в, ° четырнадцатого, пятнадцатого, шестнадцатого, семнадцатого и восЕмнадцато го ре гис тров,, управляющие входы которых соединены с восемнадцатым выходом блока управления, седьмой выход которого соединен с третьим входом блока сложения, первый выход — с управляющими входами первого и второго мультиплексоров, шестой выход - с управляющими входами третьего и четвертого мультиплексоров, пятнадцатый выход — с управляющими входами пятого и шестого мультиплексоров, а соответствующие выходы блока управления соединены с управляющими входами блока. умножения, первого, пятого, четвертого, шестого регистров, блока извлечения квадра.тного корня, второго, девятого, одиннадцатого, десятого, восьмого регистров, блока деления, седьмого регистра, первого и второго тригеров, тактовый выход блока управления соединен с тактовыми входами блоков умножейия, делений н извлечения квадратного корня, 1573543

Продолжение таблицы в атs а а — О, о1

- aD, а1, I zs I !апа! а «а,е — а, I>Di I - 140 I

4

20, 33 20

20 20

16+

Z 8

2 8

Z. 6 (13)

2 6 (4)

2 6 (14) Z 7

17+

18+

26

«dD 24, 20

Z 13

Z 7

П р и и е ч а н и е.+хв

/в )Г— сложенне1 умножение; деление; извлечение квадратного корня.

26 7. х6 х7

Z1 2Ю Т

Составитель Е.Голуб

Редактор П.Рогулич Техред Л.Сердюкова Корректор С ° 1ерии

» - - - - -- »--Заказ 1647 Тираж 528 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/ 5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101