Устройство сортировки битов

Иллюстрации

Показать всеРеферат

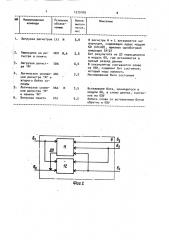

Изобретение относится к автоматике и вычислительной технике и может найти применение в устройствах управления технологическими процессами. Цель изобретения - повышение быстродействия. Устройство содержит демультиплексор 1, дешифратор адреса 2, блок памяти 3, шифратор 4, шину данных 5, блок чтения бита 6, дополнительную шину данных 7, входы "Чтение" 8 и "Запись" 9, шину адреса 10. Устройство позволяет считывать и записывать бит информации после операции преобразования. 5 ил., 1 табл.

СОЮЗ СОВЕТСКИХ социАЛистичесних

РЕСПУБЛИН (Д1) Г 06 F 7/06

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

MPH ГКНТ СССР (21) 4498951/24-24 (22) .12.09.88 (46) 30.06.90. Бюл. Р .24 (71) Ивановский энергетический институт им. В.И.Ленина (72} Ю.К.Кузьмичов, В.(О.Галата, А.О.Глебов, В.Н.Павлов, Г.Н.Федоренко и С .В.Кальянов (53) 681.325(088;8) (56) Патент СНА М 4194241, кл. G 06 F 7/00, 1980.

Патент СНА NÃ 4303990, кл. G 06 F 9/00, 1981.

„„SU„, 1575169 А 1

2 (54) УСТРОЙСТВО СОРТИРОВКИ БИТОВ (57) Изобретение относится к автоматике и вычислительной технике и может найти применение в устройствах управления технологическими процессами. Цель изобретения - повышение быстродействия. Устройство содержит демультиплексор 1, дешифратор адреса

2, блок памяти 3, шифратор 4. шину данных 5. блок чтения бита 6, дополнительную шину данных 7, входы "Чтение" 8 и "Запись" 9, шину адреса 10.

Устройство позволяет считывать и записывать бит информации после операции преобразования. 5 ил., I табл.

l575169

Изобретение относится,к автомати-ке и вычислительной технике и может, найти применение в устройствах уп1 . равления технологическими процесса5 ми.

Цель изобретения — повышение быстродействия.

На Фиг. 1 приведена блок-схема устройства сортировки битов, на

Фиг. 2-3 - варианты построения блока чтения бита на фиг. 4 - временная диаграмма работы прототипа, на фиг.5временная диаграмма работы устройства сортировки битов. 15

Устройство содержит демультиплексор 1, дешифратор 2 адреса, блок 3 памяти, шифратор 4, шину 5 данных, блок 6 чтения бита, дополнительную шину 7 данных, входы "Чтение" 8 и

"Запись" 9, шину 10 адреса, элементы вариантов построения блока 6 с 11 по 14.

Демультиплексор 1 принимает по входу 1, значение младшего бита Дф шины 7 данных и на выходе устанавливает его в разряд, указанный группой адресных проводников с шины l0 адреса и поступающий на его вход. В остальных разрядах выхода 1 уста. навливается логическая "i". Вход выборки 1 запрещает (разрешает) рабо- ту демультиплексора 1.

Дешифратор 2 адреса выбирает элементы 1, 3, 6 при их адресации с ши35 ны 10 адреса, о учетом состояния входа 9 устройства. Демультиплексор

1 выбирается при появлении адреса однобитовых операций на шине 10 адреса и сигнала "Запись" на вход 9 4 устройства. Блок 3 памяти выбирается при появлении адреса однобитовых операций или при адресации блока памяти. Блок 6 чтения бита выбирается при появлении адреса однобитовых операций и отсутствии сигнала Запись".

Блок 3 памяти служит для хранения данных и состоит из одноразрядных элементов памяти, адресные входы ко" торых присоединены к шине 10 адреса, входы записи/считывания, к шиФратору 4, входы-выходы данных - к разрядам шины 5 данных, а входы выборки - к выходу дешифратора 2.

Шифратор 4 служит,для управления 55 входом "Запись-чтение блока 3 памяти. Если на адресный вход шифратора

4 приходит адрес однобитовой операции, то на всех разрядах выхода устанавливается значение, соответствующее сигналу "Чтение", за исключением разряда для битовой операции (номер разряда указан на шине 10 адреса) . В остальных случаях все разряды выхода принимают значение, равное значению управляющего входа шифратора 4.

Шина 5 данных служит для соединения входов-выходов данных элементов устройства. Блок 6 чтения бита служит для коммутации бита иэ любого разряда шины 5 в разряд ДИ шины 7 при битовых операциях. Номер бита принимается по входу 6 с нины 10 адреса,. разрешение коммутации бита — с входа 6> и подтверждается по входу 6.

В остальных случаях (когда с входа

6з поступает запрет коммутации бита) блок 6 коммутирует нину 6 и 6,.

При разрешении чтения (вход 6,) информация с шины 5 поступает на шину иначе наоборот. На Фиг. 2 дан вариант построения блока 6, соответствующий прототипу. Мультиплексор 11 коммутирует бит с входа 6 4 в разряд

ДО на вход 6 блока 6, если приходит на мультиплексор разрешение с входа

6 и 6,. Номер бита поступает на вход 6 . При запрете битовых операций работает коммутатор 1?, коммутируя информацию с своего входа 6 и 6 в зависимости от состояния входа

6,.

Второй вариант построения блока

6 дан на фиг. 3. Мультиплексор 14 коммутирует бит с входа 6< на выход.

Номер бита поступает на вход 6 мультиплексора 14, Шифратор 13 при битовых операциях (разрешение с входа

6 ) и сигнале разрешение чтения (вход 6,) коммутирует бит мультиплексора 14 на выход 6 . При запрете чтения коммутирует бит с входа 6 йа выход ДЯ. При запрете битовых опе-. раций с мультиплексора 14 вход шифратором не анализир ется, Происходит коммутация входа 6 < на выход ДИ при запрещении чтения и входа Др на вы" ход ДО при разрешении чтения.

Шины 7, 10 и управляющие входы

8 и 9 служат для приема исходной информации от вычислителя.

Для использования устройства сортировки как обычного блока памяти вы. числитель должен обратиться к устрой. ству, так как это он делает при ра5 боте с блоком памяти: для записи на шине 10 установить адрес ячейки блока памяти, на шине 7 - данные для записи, на вход 9 — сигнал "Запись"; для чтения на шине 10 установить адрес ячейки ОЗУ, на вход 8 - сигнал

"Чтение" и принять данные из указанной ячейки.

При однобитовых операциях устройство работает следующим образам.

Для чтения бита вычислитель устанавливает в первой группе проводников шины 10 адрес ячейки блока памяти, из которой следует прочитать слово, содержащее требуемый бит. Во второй группе проводников шины 10 должен быть установлен номер бита. В третьей группе проводников должен быть установлен признак битовой операции. 20

На входе 8 должен быть установлен сигнал "Чтение". При этом дешифратор

2 адреса выдает запрет на работу демультиплексора 1 и разрешение работы блоку 3 памяти и блоку 6 чтения. 25

Шифратор 4 на всех разрядах блока 3 установит сигнал "Чтение" (поскольку на входе 9 не установлен сигнал "Записьн), Блок 3 .памяти на шину 5 выдает состояние ячейки, адрес которой указан в первой группе проводников шины 10. Блок чтения бита на шине 7 данных установит состояние разряда

ДИ, равное разряду шины 5. Далее вычислитель может принять слово данных с шины 7, в разряд ДИ которого установлен требуемый бит.

Для записи бита в Разряд слова данных, хранящегося в блоке 3 памяти, вычислитель на шине 10 устанав- 40 ливает адрес аналогично режиму битового чтения, на шине 7 в разряде ДО бит для записи, а на входе 9 сигнал

"Запись". Дешифратор 2 адреса выдает. разрешение работы демультиплексору

1 и блоку 3 памяти. Демультиплексор

; 1 принимает бит по входу 1„ и уста. ;навливает его в разряде выхода 1 (номер разряда указан на входе "2").

На остальных разрядах - логическая единица (или в третьем. состоянии).

Шифратор 4 на всех разрядах устанавливает сигнал "Чтение", кроме разряда в который будет происходить запись бита. На этом разряде установлен сигнал "Запись". Блок 3 памяти записы55 вает бит в указанный разряд, а с остальных разрядов происходит чтение.

При этом на шине 5 установлено слово

69 б данных, которое будет храниться в блоке 3 памяти после записи. На Фиг;5 дана диаграмма импульсов вычислителя на МП серии У580. Для записи требуется выполнить "1". команду "$ТА". В такт времени "1" происходит считываwe кода команды вычислителем, в такты "2", "3" - считывание адреса для записи из ПЗУ вычислителя, в такт 4н происходит работа устройства сортировки битов - запись бита в блок 3 памяти. Таким образом, такты "1"-"3" требуются вычислителю чтобы подготовить необходимую информацию. на шинах

10 и 7 и входах 9 и 8. В такт времени "4" происходит обращение к устройству сортировки битов в слове.

Программа: для прототипа, выполняющая аналогичное действие с аналогичным вычислителем, дана на фиг. 4.

Команды вычислителя -приводятся в таблице.

Формула изобретения

Устройство сортировки битов, содержац ее блок чтения бита, дешифратор, шифратор, блок памяти, причем шина адреса устройства соединена с соответствующими входами дешифратора, шифратора и с адресными входами блока чтения бита и блока памяти, информационные входы-выходы которого подключены к шине данных устройства и к входам-выходам первой группы блока чтения бита, входы-выходы второй группы которого соединены с дополнительной шиной данных устройства, а вход задания режима блока чтения би" та является входом "Чтение" устройства, вход "Запись" устройства подключен к управляюцим входам шифратора и дешифратора, первый и второй выходы которого подключены соответст"

ВеННо к управляющим входам блока чте" ния бита и блока памяти, о т л и ч а ю ц е е с я тем, что, с целью повышения быстродействия, в него введен демультиплексор, входы адреса которого подключены к шине .адреса устройства, информационные входы подключены к дополнительной шине данных устройства, информационные выходы подключены к шине данных устройства, а управляющий вход соединен с третьим выходом дешифратора, выход шифратора соединен с входом "Запись-чтение" блока памяти.

1575169

Условное обознаНаименование команды

Время выполОписание чемие нения, мкс

3,5

:4.

3,5. 5.

1. Загрузка регистров LXi Н

,,2 ° Пересылка из ре- NOV И,А гистра в память

3 ° Загрузка регист- ЖА ра "А"

Логическое умноже- ANi ние регистра "А" и второго байта команды

Логическое сложа- ORA. ние регистра "А" и памяти "И"

Загрузка памяти STA

В регистры Н и L загружается информация, содержащая адрес модуля

60 (AO-AS), признак однобитовой операции (А12)

Бит результата из ДО пересылается в модуль 60, где вставляется в нужный разряд данных

В аккумулятор считывается слово из ОЗУ, содержит бит состояния, который надо изменить

Иаскирование бита состояния

Вставление бита, хранящегося в модуле 60, в слово данных, считан- ное из ОЗУ

Запись слова со вставленным битом обратно в ОЗУ

15751G9

Е Ю Ю М Ю К1 Лг Ю н w нг н лг Я М Ю М

uruN f0

1 Я .д 4 Х 0 7 8 9 Ю 11 12 0 И Ю Ю 77

Фиг.4 1 магм w шина Ю шцна 7 р д

Составитель В.Козлов

Фиг. 1

Техред М. Ходанич Корректор Э. Лонча кова

Редактор Н.Киштулинец

Заказ 1784 Тираж 568 Подписное

ВНИЙПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101