Конвейерный умножитель

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении векторных процессоров, процессоров цифровой обработки сигналов. Цель изобретения - повышение быстродействия умножителя. Новым в умножителе, содержащем M вычислительных блоков, каждый из которых содержит регистры 1, 6 и 7, коммутатор 2, сумматор-вычитатель 4, и I-1 субрегистров 8, является введение в каждый вычислительный блок регистра 3 и триггера 5, благодаря которым обеспечивается совмещение операций коммутации множимого и суммирования/вычитания частичных произведений для предыдущих сомножителей, что приводит к ускорению процесса вычисления сумм частичных произведений. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51) G 06 F 7/52 15/332 е

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К. А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЬГГИЯМ

ПРИ ГКНТ СССР

1 (21) 4441991/24-24 (22) 17. 06.88 (46) 30.06.90. Бюл. Ф 24

171) Ленинградский электротехнический институт им. В.И.Ульянова Ленина) (72) С.И.Запорожан и Д.В.Пузанков (53) 681,325(088,8) (56) Авторскор свидетельство СССР

;11 1206800, кл. G 06 F 15/332, 1984.

Авторское свидетельство СССР

11 1464170, кл. G 06 F 7/52, 1988. (54) КОНВЕЙЕРНЫЙ УМНОЖИТЕЛЬ (57) Изобретение относится к автома:тике и вычислительной технике и может быть использовано при построе„„SU,» 1575175 А 1

2 нии векторных процессоров, процессоров цифровой обработки сигналов. Цель изобретения - повьппение быстродействия умножителя. Новым в умножителе, содержащем m вычислительных блоков, каждый из которых содержит регистры

1, 6 и 7, коммутатор 2 ° сумматор- вычитатель 4 и q -1 субрегистров 8, является введение в каждый вычислительный блок регистра 3 и триггера 5, благодаря которым обеспечивается совмещение операций коммутации множимого и суммирования/вычитания частичных произведений для предыдущих сомножителей, что приводит к ускорению процесса вычисления сумм частичных произведений.

1 ил.

1575175

Изобретение относится к автоматике и вычислительной технике и может .:быть использовано при построении высокопроизводительных вычислительных

J систем, таких как векторные процессоры, процессоры цифровой обработки сигналов и другие.

Цель изобретения — повышение быст— родействия умножителя.

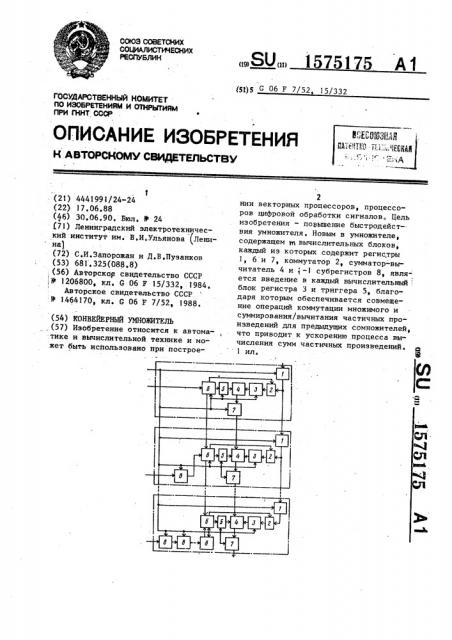

На чертеже представлена функцио нальная схема конвейерного умножителя.

Умножитель состоит из rn вычисли-! ,тельных блоков Б<,Б,...,Б .где m =

<1 дф ° со1 „ (= n/2, и — количество разрядов множи:теля), каждый из которых содержит

,первый регистр 1, коммутатор 2, четвертый регистр 3, сумматор-вычитатель

4, триггер 5, второй 6 и третий 7 регистры. Кроме того,.в Ъ.-й (1с=2...,,а) вычислительный блок входит цепочка из (1c-1) субрегистров 8, Первый регистр 1 блоков служит для хранения и передачи множимого.

Второй регистр 6 блоков служит для декодирования частичных множителей, поступающих на его входы согласно модифицированному алгоритму Бута.

Третий регистр 3 буферный в совокупности с триггером 5 служит для совмещения коммутации текущего множимого и вычисления очередной суммы частичных произведений для предыдущих сомножителей.

Субрегистры 8 служат для хранения частичных множителей, разрядность ко35 торых в соответствии с модифицированным алгоритмом Бута равна 2.

Конвейерный умножитель работает следующим образом.

Пусть необходимо nåðåìíoæèòü опеРанДы A<1Aã АГ и В ВХ . В<, Раз рядностью1 равной 4, следовательно умножитель содержит два вычислительных блока. Каждый множитель условно

45 разбивают на два частичных множителя b и Ь ($=1...,,r) причем младшая пара битов Ь поступает на ре1

2 гистр 6 блока Б,, а старшая пара Ь подается на вход субрегистра 8 блока

Б . Частичные множители декодируются согласно модифицированному алгоритму

Бута и в регистрах 6 фиксируются инструкции fc) и fg ° определяющие Функциох нирование сумматора-вычитателя 4 и коммутатора 2 первого и второго бло- 55 ков соответственно, При этом в форх мировании инструкции f < участв ют1 один бит частичного множителя Ь, который поступает на вход регистра 6 блока с выхода регистра 6 первого блока. В триггерах 5 фиксируется с задержкой на один такт разряд инструкции, управляющий работой сумматоравычитателя 4. Обозначают его через

Р и Р . Коммутатор 2 управляется

2 непосредственно с выхода регистра 6.

На выходе коммутатора 2 формируется множимое, удвоенное множимое или нулевой код„, Умножитель синхронизируется импульсами тактового генератора конвейерной системы.

В первом такте работы конвейера умножения в регистры 1 и 6 блока Б загружаются операнд А < и инструкция

f соответствующая частичному умно< жителю Ь,, а в субрегистр 8 блока Бг

1 заносится частичный множитель b,, Следовательно коммутация множимого в первом блоке и декодирование b, во втог ром блоке происходят параллельно.

Вp втором такте инструкции 121 Р< операнд Аг и скоммутированное множимое А < заносятся соответственно в регистр 6, триггер 5 и регистры 1 и

3 блока Б1. Таким образом, в первом блоке совмещаются операции вычисления первой суммы частичных произведений, соответствующей умножению А „ на В 1 и коммутации множимого А . Операнд A < пересылается в регистр 1 второго блока„ в субрегистр 8 которого записывается частичный множитель

Ь а в регистре 6 фиксируется инЕ! г струкция f,. Поэтому во втором блоке коммутируется А< .и формируется инструкция fz °

В третьем такте операнд А замещает операнд А, который, в свою очередь, выталкивает А,. В буферный регистр 3 и триггер 5 первого блока заносятся соответственно скоммутирован< ное множимое Ах и Р, а в регистре 7 фиксируется первая сумма частичных произведений. В буферный регистр 3 и триггер 5 второго блока загружаются

2 скоммутированное множимое А< и Р, Кроме того, инструкции f> и f заt гружаются в регистры 6 блоков Б, и Б соответственно, а субрегистр 8 фиксих рует частичный множитель Ь . Следовательно, в блоке Б вь<числейие первой суммы частичных произведений сомножителей Аг и Вх совмещается с коммутацией А . В блоке Бх совмещаются коммутация Аг и вычисление второй суммы

Составитель Е.Мурзина

Редактор Н,Кищтулинец Техред Л,Сердюкова Корректор О.Ципле

Заказ 1785 Тираж 571 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101

5 15751 частичных произведений для операндов

А и В, В четвертом такте множимое А4, скоммутированное множимое А, инст1 I рукция f и Р заносятся в соответ4 .3 ствующие узлы первого блока. Множимое

А>, частичный множитель Ь, скоммутированное множимое А, инструкция

f и Р запоминаются в соответст2 2 вующих узлах блока Б . В регистрах

7 обоих блоков фиксируются суммы частичных произведений, полученные в тре.тьем такте, При этом на выходе умножителя будет произведение операндов

А,, и В .

В пятом такте множимое А, скоммуl тированное множимое А, инструкция f к и Р заносится в соответствующие узлы первого блока, Множимое А, час- 20 тичный множитель Ь, скоммутирован2 ное множимое А, инструкция f< и Р>

2 2 запоминаются в соответствующих узлах второго блока. Очередные суммы частичных произведений, полученные в четвер- 25 том такте, фиксируются в регистрах 7 блоков Б„ и Б . При этом на выходе койвейерного умножителя будет произведение операндов А < и В, И так далее.

Таким образом, умножитель выдает произведение двух операндов, в каж дом такте, начиная со второго.

Формула из обр е тения

Конв ейерный умножитель, содержащий

m вычислительных блоков (m=n/2, где

n — разрядность множителя), каждый из которых содержит первый, второй и третий регистры, сумматор-вычи— татель, коммутатор и i-1 субрегистров (з.=1...,,т), причем вход множимого умножителя соединен с информационным входом первого регистра первого вычислительного блока, входы синхронизации первого второго и третьего регистров, каждого субрегистра.всех вычислительных блоков соединены с входом синхронизации умножителя, вход множителя которого соединен с первым информационным входом второго регистра первого вычислительного бло ка и информационным входом первого субрегистра каждого k-го вычислительного блока (k=2, т), а в каждом i-м вычислительном блоке выход первого регистра соединен с информационным входом коммутатора, уйравляющий вход которого соединен с первым выходом второго регистра, выход сумматора-вычитателя соединен с информационным входом третьего регистра„ выход 1-гб субрегистра (1=1,...,m-2) соединен с информационным входом (1+1)-го субрегистра, выход (i-1)-го субрегистра соединен с первым информационным входом второго регистра, выходы первого и третьего регистров и второй выход второго регистра

j-го вычислительного блока (j =1,..., m-1) соединены соответственно с информационным входом первого, первым информационным входом сумматора-вычитателя и вторым информационным входом второго регистра (j+1)-го вычислительного блока, выход третьего регистра m-го вычислительного блока соединен с выходом результата умножителя, отличающийся тем, что, с целью повьппения быстродействия, в каждый вычислительный. блок введены четвертый регистр и триггер, причем входы синхронизации четвертого регистра и триггера каждого вычислительного блока соединены с входом синхронизации умножителя, а в каждом вычислительном блоке третий выход второго регистра соединен с информационным входом триггера, выход которого соединен с управляющим входом сумматора-вычитателя, второй информационный вход которого соединен с выходом четвертого регистра, информационный вход которого соединен с выходом коммутатора.