Устройство для перебора сочетаний

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения специализированных вычислительных устройств, предназначенных, например, для автоматизированного конструирования радиоэлектронной и вычислительной аппаратуры. Целью изобретения является упрощение устройства. Устройство содержит триггеры, регистры, регистры сдвига, элементы И, ИЛИ, И-ИЛИ, элементы задержки. По сравнению с прототипом исключены два регистра, четыре группы элементов И, две группы элементов задержки, элемент И, элемент ИЛИ, три элемента задержки. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУВЛИК (51)5 С 06 Р 15 20

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСН0МУ СВИДЕТЕЛЬСТВУ

+ 1

st t — 1

1зе< Ы сф0

then g< 8

else g I

" ««ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

f (21) 4417749/24-24 (22) 27.04.88 (46) 30.06.90. Бюл. 11< 24 (71) Таганрогский радиотехнический институт им. В.Д.Калмыкова (72) В.М«Глушань, В.М.Курейчик и А.В.Пришибский (53) 681.3(088.8) (56) Авторское свидетельство СССР

И 1262520, кл. G 06 F 15/20, 1985.

Авторское свидетельство СССР

Р 1427382, кп. G 06 F 15/20, 1987.. (54) УСТРОЙСТВО ДЛЯ ПЕРЕБОРА СОЧЕТАНИЙ (57) Изобретение относится к автомаИзобретение относится к автоматике и вычислительной технике и может быть использовано для построения специализированных вычислительных уст. роиств предназначенных для автомати" зированного решения задач конструирования радиоэлектронной и вычислитель ной аппаратуры.

Цель изобретения — упрощение устройства.

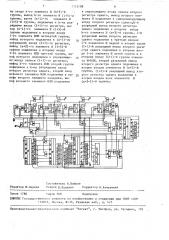

На чертеже представлена функциональная схема устройства на четыре разряда (п=4).

Устройство. содержит триггеры 1-4, элементы И 5-19, ИЛИ 20-25, регистр 26 сдвига, элементы 27 и 28 задержки, ключ 29, элемент ИЛИ 30, регистры 31 и 32, регистр 33 сдвига, элементы

И 34-37, 38.1-38.6, 39.1-39.5, 40.1-40.5, 41 .1 -41 .4, 42.1 42.4, 43-47, элементы ИЛИ 48.1-48.5, эле„„SU,, 1575198 А 1

2 тике и вычислительной технике и может быть использовано для построения специализированных вычислительных устройств, предназначенных, например, цля автоматизированного конструирования радиоэлектронной и вычислитель.ной аппаратуры. Целью изобретения является упрощение устройства. Устройство содержит триггеры, регистры сдвига, элементы И, ИЛИ, < И-ИЛИ, элементы задержки. По сравнению " прототипом исключены две регистра, четыре группы элементов И, две группы элементов задержки, элемент И, элемент ИЛИ, три элемента задержки.

1 ил. мент И-ИЛИ 49, элементы ИЛИ 50-55, элементы 56-58 задержки, тактовый вход 59 кода, вход 60 запуска, информационные выходы 61-64, выход 65 окончания перебора.

В работе устройства используется алгоритм:

Ф 0 then g4 -Ц

if g = f thån

Ь< else g и

<<-< дл «<- go н)

if t = Ъ вЂ” 1 or t = 0 then t t + 1

1575198

t - 1: — g „ л Л (,Л вЂ” л с, < с

if t = О then 1 - с1 — 1

else 1 : — t + 1, else

1< — ол (л — b1 + 1 г л л

Перед началом работы триггеры 1-4 10 регистры 26,31-33 устанавливаются в нулевое положение. Затем в триггерь 1 и 2 (для случая n=4, k=2) записьвают единицы и регистр 26 записывается в унитарном коде значение

t+=2, а в регистры 31-33 — в унитарном коде значение с ; = k+1,i=1 о, = i+I, где i=2-(n-l). Пусковой имп51льс с входа 60 поступает через элемент ИЛИ 30 на входы элементов И 161 и открывая их, обеспечивает поступление очередного сочетания 1100 на выходы устройства. Сигнал, пройдя элемент 27 задержки, открывает ключ 29 для прохождения тактового им- 25 пульса с входа 59 на входы элементов

И 5-!2. Тактовый импульс проходит через открытый элемент И 11 и далее через элементы ИЛИ 51,53 и 55, на взводы С.и $ 1 регистра 26, осущест- 30 вляя уменьшение значения t=2 на 1 (t t-1). Так как элемент И 40.3 о1крыт единичным потенциалом с третьего разрядного выхода регистра 33, а, элемент И 41.1 — с второго разрядного выхода регистра 26, то импульс поступает через элементы И.41,1 и

ИЛИ 20 на вход триггера 1, осуществляя его переход в нулевое состояние (g4 gt), Через элементы И 40. 3 и Щ

ИЛИ 22 импульс поступает ня вход триггера 3, осуществляя его переброс в нулевое состояние (g g"„,) и через элемент И 40.3 поступает на входы V и D 4 регистра 31, осуществляя за/ л л лись в него значения с = 4 (c"„, - „+,).

С выхода элемента 28 задержки импульс поступает через элемент ИЛИ 30 на входы элементов И 16-19 и, открывая их, обеспечивает поступление очеРедного сочетания 0110 на выход устРойства. Одновременно с этим импульс с выхода элемента 28 задержки поступает через элемент ИЛИ 25 на вход V регистра 33, так как элементы

И 38.1-38.6 открыты единичным потенциалом с третьего разрядного выхода

Регистра 33, то информация регистра 31 л л„ перепишется в регистр 33 (ь, - "„,).

Элемент И 45 открыт нулевым потенциалом с выхода элемента И-ИЛИ 49. Элемент И 35 открыт единичными потенциалами с единичного выхода триггера 2 и третьего разрядного выхода регистра 33, поэтому элемент И 43 также открыт. Импульс с выхода элемента

И 45 проходит через элемент, И 43, ИЛИ 53 и 55 на входы С и $ 1 регистра 26, уменьшая значение t=l на (t t — g<,„), а также на входы элементов И 38.1 и т.д. (при п=4 только один элемент И 38.1) и, так как элемент И 38.1 открыт единичным потенциалом с третьего разрядного выхода регистра 33, то импульс проходит через элемент ИЛИ 24 на вход V, разрешая перезапись информации из

n . л регистра 31 в регистр 32 (ь <, -, ) .

С выхода элемента И импульс проходит через элемент 57 задержки и элемент И 47 на входы С и S 1 регистра 33, сдвигая информацию в нем на один разряд в сторону младшего разряда (c. - о ). После формирования л л последнего сочетания 1001. в регист,рах будут содержаться слова: 00001, 00100, 00010. Элемент И 40.5 будет открыт единичным потенциалом с выхода последнего разряда регистра 33, следовательно импульс с выхода элемента 57 задержки, пройдя через элемент 56 задержки и элемент И 40.5, поступит на выхоц 65 окончания перебора. формула изобретения

У стройство для перебора сочет аний, содержащее и триггеров (п — число перебираемых элементов), ключ., первый регистр сдвига, и-2 регистров, четыре группы элементов ИЛИ, n+6 групп элементов И, элементы И-ИЛИ, восемь элементов ИЛИ, пять элементов И, пять элементов задержки, причем вход первого элемента задержки является пусковым входом устройства и соединен с первым входом первого элемента

ИЛИ, выход первого элемента задержки подключен к управляющему входу ключа, информационный вход ключа является тактовым. входом устройства, выход ключа подключен к входу второго элемента задержки, счетный вход i-ro триггера (i l n) подключен к выходу

i-го элемента ИЛИ первой группы, прямой и инверсный выходы i-го триг5 137 гера подключены к первым входам i — х элементов И и первой и второй групп соответственно, выходы элементов И первой группы подключены к входам второго элемента ИЛИ, выходы элементов И второй группы подключены к входам третьего элемента ИЛИ, выход второго элемента ИЛИ через третий элемент задержки подключен к первым входам четвертого и пятого элементов ИЛИ, выход третьего элемента ИЛИ подключен к второму входу четвертого элемента ИЛИ и к первому входу шестого элемента ИЛИ, выход четвертого элемента ИЛИ подключен к синхронизирующему входу первого регистра сдвига, выходы пятого и шестого элементов ИЛИ подключены к управляющим входам направления сдвига первого ре— гистра сдвига. (1+1)-й разрядный выход первого регистра сдвига подключен к первому входу 1-го элемента И третьей группы, выход которого подключен к первому входу i-го элемента ИЛИ первой группы, второй вход

j-го (j =I,n-l) элемента ИЛИ первой группы соединен с выходом j-ro элемента И четвертой группы, первые входы всех элементов И четвертой группы подключены к первому разрядному выходу первого регистра сдвига, -прямой выход i-го триггера подключен к первому входу i-ro элемента И пятой группы, выходы элементов И пятой группы подключены к входам седьмого элемента ИЛИ, выход которого подключен к первому входу первого элемента И, выход первого элемента И подключен к третьему вхоцу четвертого элемента ИЛИ и к второму входу шестого элемента HJIP., выход второго элемента задержки подключен к второму входу первого элемента ИЛИ, к прямому входу второго элемента И и к первому входу третьего элемента И, выход второго элемента И подключен к второму входу первого элемента И, к входу четвертого элемента задержки и к первым входам (n+2)-õ элементов И с шестой по (n+2)-ю групп, выход третьего элемента И подключен к четвертому входу четвертого элемента ИЛИ и к второму входу пятого элемента ИЛИ, выход четвертого элемента задержки подключен к первому входу четвертого элемента И к прямому входу пятого элемента И, к первому входу восьмого элемента ИЛИ и через пятый элемент задержки к первому

3198 6

55 входу (и+1)-ro (n+3) é группы, выход пятого элемента И подключен к первым входам всех элементов И (n+4) и группы, первый разрядный выход первого регистра сдвига подключен к второму входу четвертого элемента И и к инверсному входу пятого элемента И, (i+I)-й разрядный выход первого регистра сдвига подключен к второму входу i-ro элемента И (n+4)-й группы, k-й (k=1,n+1) разрядный выход первого регистра сдвига подключен к первому входу

k-й группы элементов И-ИЛИ, выход элемента И-ИЛИ подключен к инверсному входу второго элемента И и к второму входу третьего элемента И, выход i-го элемента И (и+4)-й группы подключен к соответствующему входу (i+1)-го элемента ИЛИ второй группы, выходы k-x элементов И с шестой по (n+2)-ю групп, а также (n+3)-й группы подключены к соответствующим входам k-го элемента И-ИЛИ второй группы, первый вход i-го элемента И (п+6)-й группы подключен к прямому выходу -го триггера, вторые входы элементов И .(и+6)-й группы являются выходами устройства, выход (и+I)-ro элемента И (n+3)-й группы является выходом окончания перебора устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит второй регистр сдвига, причем выхоц ключа подключен к вторым вхолам элементов И первой и второй групп, к вторым входам элементов И третьей группы, к первым входам с первого по и-й элемент И (п+3)-й группы, выход i-го элемента И (и+3)-й группы подключен к третьему входу j-го элемента ИЛИ первой группы, выход п-го элемента И (и+3)-й группы подключен к второму входу и-го элемента ИЛИ первой группы,выход (j+l)-ro элемента И (и+3)-й группы подключен к второму входу

j-ro элемента И четвертой группы, выход (1+1)-ro (1=1, и-3) элемента И (и+3)-й группы подключен к первым входам 1-х элементов ИЛИ третьей и четвертой групп, выход (n-1)-го элемента И (и+3)-й групп подключен к и-му разрядному входу и управляющему входу записи первого регистра, k-й разрядный выход 1-ro регистра подключен к первому входу k-ro элемента И (1+3)-й группы, k-й разрядный выход (n-2)-го регистра подключен к первоl 575198

Составитель В.Байков

Редактор Ю.Середа Техр д М,Xоданич Корректор N.Êó÷eðÿâàÿ

Заказ 1786

Подписное

Тир: ж 569

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101 му. входу k-го элемента И (n+5)-й группы, выход k-го элемента И (1+5)-й гр ппы, кроме (п-1)-ro элемента И (1+5)-й группы, подключен к k-му раз5 рядному входу (1+1)-го регистра, выход (n-1)-го элемента И (1+5)-й гр ппы подключен к второму входу

1-ро элемента ИЛИ четвертой группы, выфод которого подключен к (п-1)-му разрядному входу (1+1).-го регистра, вьйод (n+2)-го элемента И (1+5)-й грфппы подключен к второму входу

1-Го элемента ИЛИ третьей группы, выход которого подключен к управляющему,входу записи (1+1)-ro регистра, 1 выход k-го элемента ИЛИ второй группы подключен к k-му разрядному входу второго регистра сдвига, второй вход восьмого элемента ИЛИ подкпючен к вы- 20 ходу второго элемента задержки, выход восьмого элемента ИЛИ подключен к управляющему входу записи второго регистра сдвига, выход второго эпемента И подключен к синхронизирующему входу второго регистра сдвига,k-й разрядный выход второго регистра сдвига подключен к второму входу

k-го элемента И (п+3)-й группы, i-й разрядный выход второго регистра сдвига подключен к третьим входам

1-х элементов И первой H второй групп (+1)-й разрядный выход второго регистра сдвига подключен к второму входу i-ro элемента И пятой группы и к второму входу (i+1)-й группы элемента И-ИЛИ, второй разрядный выход второго регистра сдвига подключен к вторым входам элементов И (п+5)-й группы (1+2)-й разрядный выход второго регистра сдвига подключен к вторым входам всех элементов И (и+3-1)-й группы,