Счетчик с контролем ошибок

Иллюстрации

Показать всеРеферат

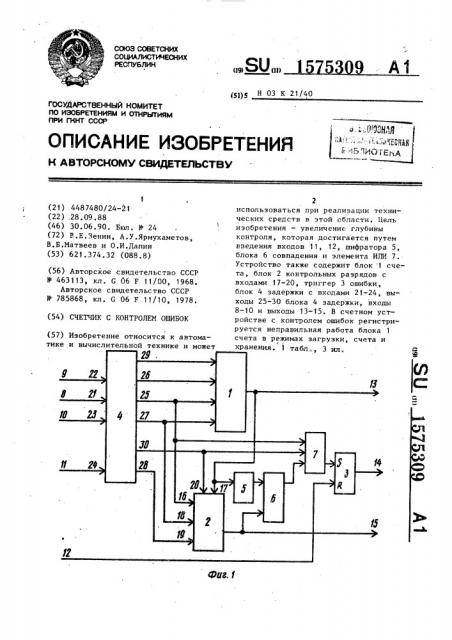

Изобретение относится к автоматике и вычислительной технике и может использоваться при реализации технических средств в этой области. Цель изобретения - увеличение глубины контроля, которая достигается путем введения входов 11, 12, шифратора 5, блока 6 совпадения и элемента ИЛИ 7. Устройство также содержит блок 1 счета, блок 2 контрольных разрядов с входами 17 - 20, триггер 3 ошибки, блок 4 задержки со входами 21 - 24, выходы 25 - 30 блока 4 задержки, входы 8 - 10 и выходы 13 - 15. В счетном устройстве с контролем ошибок регистрируются неправильная работа блока 1 счета в режимах загрузки, счета и хранения. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) щ) Н 03 К 21/40

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИ4ЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И (ЛНРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4487480/24-21 (22),28. 09, 88 (46) 30.06.90. Бил. № 24 (72) В.Е.Ленин, А.У.Ярмухаметов, В.Б.Матвеев и О.И.лапин (53) 621.374.32 (088.8) (56) Авторское свидетельство СССР № 463113, кл. G 06 F 11/00, 1968.

Авторское свидетельство СССР

У 785868, кл. G 06 F 11/10, 1978. (54) СЧЕТЧИК С КОНТРОЛЕМ ОБИБОК (57) Изобретение относится к автоматике и вычислительной технике и может использоваться при реализации технических средств в этой области. Цель изобретения — увеличение глубины контроля, которая достигается путем введения входов 11, 12, шифратора 5, блока 6 совпадения н элемента ИЛИ 7.

Устройство также содержит блок 1 счета, блок 2 контрольных разрядов с входами 17-20, триггер 3 ошибки, блок 4 задержки с входами 21-24, выходы 25-30 блока 4 задержки, входы

8-10 и выходы 13-15. В счетном устройстве с контролем ошибок регистрируется неправильная работа блока 1 счета в режимах загрузки, счета и

I хранения 1 табл 3 ил

1575309

ЗО

Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств в этой области ° . Э

Цель изобретения — увеличение глубины контроля за счет введения новых конструктивных признаков, обеспечивающих расширение класса регистрируемых ошибок. 1О

На фиг. 1 приведена структурная схема счетчика с контролем ошибок, на фиг. 2 и 3 — схемы блока контрольных разрядов и блока задержки.

Счетчик с контролем ошибок содержит блок 1 счета, блок 2 контрольных разрядов, триггер 3 ошибки, блок 4 задержки, шифратор 5, блок 6 совпадения, элемент ИЛИ 7, первый — пятый входы 8 — 12, первый — третий 20 выходы 13-15, первый — пятый входы

16-20 блока 2 контрольных разрядов, перьый — четвертый входы 21 — 24 и первый — шестой выходы 25 — 30 блока

4 задержки, при этом первый вход 8 25 соединен с первым входом 21 блока 2 задержки, первый выход 25 которого соединен с первым входом 16 блока 2 контрольных разрядов, выход блока 1 счета соединен с вторым входом 17 блока 2 контрольных разрядов и первым выходом 13, выход триггера 3 ошибки соединен с вторым выходом 14, второй 9, третий 10 и четвертый 11 входы соединены соответственно с вторым 22, третьим 23 и четвертым 24 входами блока 4 задержки, первый 25, второй 26 и третий 27 выходы которого соединены соответственно с первым, вторым и третьим входами блока 1 сче- 4О та, выход которого соединен с входом шифратора 5, выход которого соединен с первым входом блока 6 совпадения, первый выход 25 блока 4 задержки соединен с первым входом элемента ИЛИ 7, выход которого соединен с установочным входом триггера 3 ошибки, третий выход 27 и четвертый выход 28 блока 4 задержил соединены соответственно с третьим 18 и четвертым 19 входами блока 2 контрольных разрядов, выход ко50 торого соединен с третьим выходом 15 и вторым входом блока 6 совпадения, выход которого соединен с вторым входом элемента ИЛИ 7, пятый выход 29 блока 4 задержки соединен с.четвертым 55 входом блока 1 счета, а шестой выход ю

30 — с третьим .входом элемента ИЛИ 7 и пятым входом 20 блока 2 контрольных разрядов, пятый вход 12 соединен с входом сброса триггера 3 ошибки.

Блок 1 счета предназначен для запоминания "-начения, поступающего при установке на вход 9 данных счетчика, увеличения (или уменьшения) его в счетном режиме и выдачи полученного значения на выход 13 данных счетчика.

Блок 1 счета может быть реализован на микросхеме 531ИЕ17, при этом выходы 25, 26, 27 и 29 блока 4 задержки соединены соответственно с входами запрета счета с переносом, данных, запрета записи и синхрониза ции микросхемы. На вход направления счета цодается единичный сигнал, если счетчик считает в сторону увеличения, и нулевой, если счетчик считает в сторону уменьшения. На вход запрета счета без переноса микросхемы подается нулевой сигнал. Блок 2 контрольных разрядов (фиг. 2) содержит шифратор 3 1, муль-, типлексор 32, элементы И 33 и ИЛИ 34 и регистр 35.

Блок 2 контрольных разрядов предназначен для запоминания значения, поступающего при установке на вход

11 контрольных разрядов данных счетчика, формирования и запоминания при счете контрольных разрядов нового значения блока 1 счета, выдачи хранимого значения на выход 15 контрольных разрядов данных счетчика, а также участвует в формировании сигнала ошибок.

Шифратор 3 1 предназначен. для формирования контрольных разрядов, соответствующих текущему значению блока

1 счета, и может быть реализован, например, с помощью схемы сложения по модулю два (при контроле на четность).

Входы 18 и 1.9 и выход шифратора

31 соединены соответственно с адресным и первыМ и BTGpbIM информационными входами мультиплексора 32, выход которого соединен с информационным входом регистра 35, вход записи которого соединен с выходом элемента

ИЛИ 34.

Триггер 3 ошибки предназначен для формирования сигнала ошибки, поступающего на выход 14 ошибки счетчика.

Блок 4 задержки (фиг. 3) содержит генератор 36 импульсов, счетный триггер 37, элементы ИЛИ 38 и 39 и реристр 40 задержки. Блок 4 задержки предназначен для задержки на один такт работы счетчика сигналов, посту-, пающих на входы 8-11, а также для синхронизации работы "счетчика. Входы

8, 9, 10 и 11 соответственно запрета счета, данных, запрета записи и контрольных разрядов данных счетчика соединены соответственно с первым, вторым, третьим и ;етвертым информационными входами регистра 40 задержки, выходы которого с первого по четвертый соединены с выходами 25-28 блока

4 задержки соответственно..

В течение периода счета триггера

37 выполняется один такт работы счетчика. Прямой и и»»версньп» выходы счетного триггера 37 соединены с соответствующими входами элемента ИЛИ 38 и элемента ИЛИ 39, выход которого соединен с входом записи регистра 40 задержки. По фронту импульса, формируемого на выходе элемента ИЛИ 39, в регистр 40 задержки заносятся поступающие на его информационные входы данные, причем входам 21-24 соответствуют выходь» 25-28.

Шифратор 5 предназначен для формирования контрольных разрядов, сооТ ветствующих такому значению блока счета, которое он имел бь» после выполнения операции счета в направлении, обратном заданному в счетчике °

Шифратор 5 может быть реализован, например, в виде ПЗУ.

Вариант прошивки ПЗУ,при четырехразрядной блоке 1 счета, контроле на четность и счете в сторону увеличения (уменьшения) приведен в таблице.

Счетчик работает следуюп,им образом.

По фронту импульса, формируемого на выходе элемента ИЛИ 39, в регистр

40 задержки заносятся значения сигналов запрета счета и записи, а также данных и контрольных разрядов данных, поступающих иа входы 8-1 1 счетчика.

В течение следующего такта счетчика значения на соответствуюпп»х выходах блока 4 задержки не изменяются, что обеспечивает синхронизацию работы счетчика и устройства, использупш»еr"o его (например, ЦБ1»). Поэтому в дальнейшем будем считать, что сигна- лы йа входах 8-11 счетчика синхронны с тактами счетчика и поступают на блоки счетчика, минуя блок 4 задержки.

75309 б

При включении питания устройство, использующее счетчик, выполняет его начальную установку. На входы 9 и 11 . данных и контрольных разрядов данных

5 счетчика подаются соответственно начальные данные счетчика и значение контрольных разрядов этих данных. На входы 8 и 10 запрета счета и запрета записи счетчика подаются соответственно единичный и нулевой сигналы.

При этом блок 1 .счета переходит в режим записи. Импульс с выхода 29 блока 4 задержки поступает на вход синхрвнизации блока 1 счета, вследствие чего в него заносится значение, поступающее на вход 9 да»»ных счетчика.

Нулевой сигнал с входа 10 запрета

2Q записи счетчика поступает на адресный вход мультиплексора 32 и через элемент И 33 на первый вход элемента ИЛИ

34. Импульс с выхода 30 блока 4 задержки через элемент ИЛИ 34 подается

25 на вход записи регистра 35,, т»ри этом значение контрольных разрядов начальных данных, поступающее на вход 11 счетчика, через мультиплексор 32 поступает на информационньп» вход регистра 35 и заносится в него-.

Единичный сигнал с входа 8 запрета счета через элемент ИЛИ 7 поступает на установочный вход триггера 3 ошибки, запрещая его установку.

Затем на вход 12 сброса ошибки

35 счетчика подается импульс, поступающий .на вход сброса триггера 3 ошибки и сбрасывающий его, Все последующие установки счетчика выполняются аналогично за исключением того, что не выполняется сброс триггера 3 ошибки, В счетном режиме устройство работает следующим образом.

45 На входь» 8 и 10 запрета счет а и запрета записи счетчика подаются соответственно нулевой и единичный сигналы, при этом блок 1 счета переходит в счетнь»й режим. Импульс с выхода

5Q 29 блока 4 задержки поступает на вход синхронизации блока 1 счета, значение которого увеличивается (уменьшается) на единицу и поступает на входы шифраторов 5 и 31. На выходе шифратора 5 формируется значение контрольных разрядов, соответствующих такому значению блока 1 счета, которое он имел бы после выполнения операции счета в направлении, обратном задан50

7 15753 ному в счетчике. Если операция счета выполнилась верно, то это значение блока 1 счета совпадает с тем значением, которое он имел до операции счета. Если при этом блок 2 контрольных разрядов содержит корректное значение, т.е. значение, соответствующее тому значению блока 1 счета, ко« торое он имел до операции счета, то а на первый и второй входы блока 6 совпадения поступают одинаковые значения. При этом на его выходе формируется единичный сигнал и поступает через элемент ИЛИ 7 на установочный вход триггера 3 ошибки, запрещая его установку.

Если операция счета выполнялась неверно илн блок 2 контрольных разрядов содержит некорректное значение,, то его значение не совпадает со значением на выходе шифратора 5. При этом на выходе блока 6 совпадения формируется нулевой сигнал, поступающий на второй вход элемента ИЛИ 7, 25 на первый вход которого поступает нулевой сигнал с входа 8 запрета счета счетчика. Отрицательный импульс с выхода 30 блока 4 задержки через элемент ИЛИ 7 поступает на установоч- 30 ный вход триггера 3 ошибки. По спаду этого импульса триггер 3 устанавливается в единицу. Единичный сигнал с выхода триггера 3 ошибки поступает на выход 14 ошибки счетчика.

Единичный сигнал с входа 10 запрета записи счетчика поступает на адресный вход мультиплексора 32, настраивая его на передачу значения с второго информационного входа. На вы- 4р ходе шифратора 31 формируется значе«

arne йонтрольньж разрядов, соответствующих новому значению блока 1 счета, и через второй вход мультиплексора 32 поступает на информационный:, 45 вход регистра 35.

Нулевой сигнал с входа 8 запрета счета через элемент И 33 поступает на первый вход элемента ИЛИ 34. Отрицательный импульс с выхода 30 блока 4 задержки через элемент ИЛИ

34 поступает на вход записи регистра 35 По фронту этого импульса в регистр 35 заносится значение контрольных разрядов, соответствующее текущему значению блока 1 счета.

Таким образом, в режиме счета в течение одного такта счетчика значение блока 1 счета увеличивается

09 (уменьшается) на единицу, а в блоке

2 запоминается значение контрольных разрядов, соответствующее новому значению блока 1 счета. Если операция счета выполнилась неверно или блок

2 содержит некорректное значение, то триггер 3 ошибки устанавливается в единицу. В противном случае его значение не изменяется.

В режиме хранения на входы 8 и 10 запрета счета и запрета записи счетчика подаются единичные сигналы. При этом блок 1 счета находится в режиме хранения информации, единичный сигнал через элемент ИЛИ 7 поступает на установочный вход триггера 3 ошибки, запрещая его установку, на входы элемента И 33 поступают единичные сигналы, с выхода которого единичный сигнал через элемент ИЛИ 34 поступает на вход записи регистра

35, запрещая запись в него.

Таким образом, в режиме хранения состояние счетчика не изменяется, а значения блока 1 счета и блока 2 контрольных разрядов поступают на выходы 13 и 15 данных и контрольных разрядов данных счетчика соответственно.

Таким образом, недопустимый контролируемый код, возникающий.при ошибочной работе счетчика в режиме установки или в режиме хранения, обнаруживается в процессе счета и приводит к установке триггера ошибки.

Кроме того, неверное значение старшего разряда блока счета, возникающее в режимах установки, хранения или счета и приводящее к недопустимому контролируемому коду, также обнаруживается в процессе счета- и приводит к установке триггера ошибки.

Формула изобретения

Счетчик с контролем ошибок, содержащий первый, второй и третий входы, первьй, второй и третий выходы, блок счета, блок контрольных разрядов, триггер ошибки и блок за держки, первый вход соединен с первым входом блока задержки, первый выход которого соединен с первым входом блока контрольных разрядов, выход блока счета соединен с вторым входом блока контрольных разрядов и первым вьжодом, выход триггера ошибки соединен с вторым выходом, о т л и ч а

09 10 новочным входом триггера ошибки, третий и четвсртый выходы блока задержки соединены соответственно с третьим и четвертым входами блока контрольных разрядов, выхоц которого соединен с третьим выходом и вторым входом блока совпадения, выход которого соединен с вторым входом элемента ИЛИ, пятый выход блока задержки соединен с четвертым входом блока счета, шестой выход блока задержки соединен с третьим входом элемента

ИЛИ и пятым входом блока контрольных разрядов, пятый вход соединен с входом сброса триггера ошибки °

1сУ ю шийся тем, что, с целью увеличения глубины контроля, в него введены четвертый и пятый входы, шифратор, блок совпадения и элемент ИЛИ, второй, третий и четвертый входы соединены соответственно с вторым, третьим и четвертым входами блока задержки, первый, второй и третий выходы которого соединены соответственно с первым, вторым и третьим входами блока счета, выход которого соединен с входом шифратора, выход которого соединен с первым входом блока совпадения, первый выход блока задержки соединен с первым входом элемента

ИЛИ, выход которого соединен с устаВыход блока 1 Выход шифратора 5 при прямом счете

Выход шифратора S при обратном счете

Выход шифратора 31

0001

0011

0101

0111

1001

1011

f100

1101

1111

О

1

О

0

О .

1

О

О

О

О

1

О

О

О

1

О

О

О

1

1

О

О

О

1

О

О

О

1

О

1575309

Составитель К.Ранов

Техред М.Дидык

Редактор А.Лежнина

Корректор О.Кравцова

Заказ 1791 Тираж 663 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно--издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101