Двоично-десятичный цифроаналоговый преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах преобразования цифровой информации в аналоговую, а также в цифровых измерительных приборах. Цель изобретения - повышение точности и уменьшение коммутационных выбросов выходного сигнала. Двоично-десятичный цифроаналоговый преобразователь содержит преобразователь 1 код-напряжение, выходную шину 2, N декадных преобразователей 3.1-3.N код-ток, в состав каждого из которых входят четырехразрядный регистр 4, блок 5 ключей, резистивная матрица 6 и преобразователь 7 код-код на элементе ИЛИ, входные шины 8.1-8.N преобразуемого кода и входную шину 9 установки в нулевое состояние. Резистивная матрица 6 каждого преобразователя 3 выполнена на четырех резисторах, сопротивления которых относятся как целые числа 1:1:2:4. 1 з.п. ф-лы, 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

А1

O9I Ol) . (51)5 H 03 И 1/66

5 ..„ : 555 5-ЦйД

55к" .5 „51 455555Ь55

1

1 -А; 5."5 ИНЦ, :3:. :О t" гЖ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСНОМУ СВИД:ТЕЛЬСТВУ

Ю.i

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯЫ

ПРИ ГКНТ СССР (21) 4351741/24-24 (22) 28. 12.87 (46) 30.06.90. Бюл. У 24 (71) Киевский политехнический институт им. 50-летия Великой Октябрьской социалистической революции (72) Е.H.Áàíÿ, A.Ñ.Îñàä÷àÿ и В.Л.Селиванов (53) 681.325 (088.8) (56) Зангер K. Электронные системы.

Теория и применение. М.: Мир, 1980.

Авторское свидетельство СССР

У 995307, кл. Н 03 М 1/бб, 1980. (54) ДВОИЧНО.-ДЕСЯТИЧНЫЙ ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ (57) Изобретение относится к автоматике и вычислительньй технике и может быть использовано в системах преобразования цифровой информации в

2 аналоговую, а также в цифровых измерительных приборах. Цель изобретения — повышение точности и уменьшение коммутационных выбросов выходного сигнала. Двончно-десятичный цифроаналоговый преобразователь содержит преобразователь 1 код — напряжение, выходную шину 2, и декадных преобразователей 3.1-3.п код — ток, в состав каждого иэ которых входят четырехразрядный регистр 4, блок 5 ключей, реэистивная матрица б и преобразователь 7 код — код на элементе

° ИЛИ, входную шину 8 преобразуемого кода и входную шину 9 установки в нулевое состояние. Резистивная матрица 6 каждого преобразователя выпол- Е нека на четъ5рех резисторах, сопротивления которых относятся как целые числа 1:1:2:4, 1 з.п. ф-лы, 2 ил. (:

1575313

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах преобразования цифровой информации в анало5 говую, а также в цифровых измерительных приборах.

Цель изобретения — повышение точности преобразования и уменьшение величины коммутационных выбросов вы- 10 ходного сигнала.

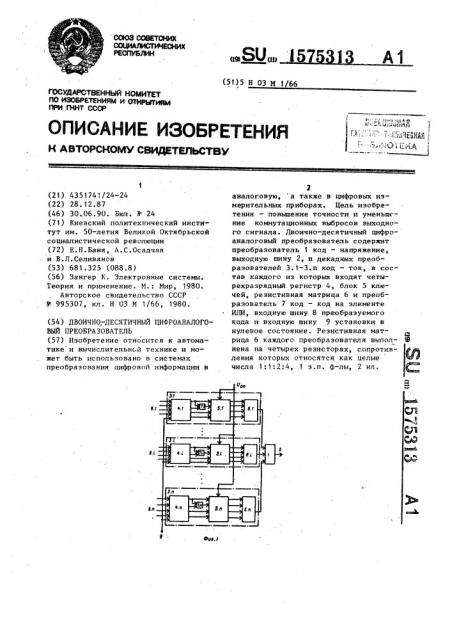

На фиг. 1 представлена функциональная схема устройства ; на фиг.2— реализация резистивной матрицы.

Двоично-десятичный цифроаналоговый преобразователь (фиг,1) содержит преобразователь 1 ток — напряжение, выходную шину 2, и декадных преоб-. разователей 3 код — ток, выполненных в виде четырехразрядного регист- щ ра 4„ блока 5 ключей, резистивной матрицы 6 и преобразователя 7 код — код на элементе ИЛИ, входную шину 8 преобразуемого кода и входную шину 9 установки. Резистивная матрица 6 каждого преобразователя 3. выполнена на четырех резисторах, -сопротивления которых относятся как целые числа

1: 1:2:4.

Двоично-десятичный цифроаналоговый преобразователь (фиг.1) работает следующим образом

После поступления команды занесения по шине 9 в регистры 4 заносится значение преобразуемого кода

N, поступающего на входную шину 8, Преобразуемый код с выхода регистра 4 преобразователя 3 код — ток поступает на управляющие входы блока 5.i .ключей, на информационный вход которого подается опорное напряжение, одинаковое для всех блоков 5 ключей.

При этом сигналы с выходов первого (старшего), третьего и четвертого (младшего) разрядов регистра 4 поступают непосредственно на соответствующие управляющие входы блока 5 ключей, на второй вход которого поступает сигнал с выхода элемента ИЛИ

7, первый и второй входы которого соединены соответственно с выходами

50 первого и второго разрядов регистра 4. При этом если на входе регистра присутствует код я)а2яъа4 В Виде двоично-десятичного кода в системе счисления 8-4-2- 1, то на управляющих входах блока 5 ключей формируется код a„(a„Ua ) аза, где знак обозначет операцию логического сложения.

В соответствии со значением полученного кода включаются соответствующие ключи блока 5 ключей, подавая на соответствующие входы реэистивной матрицы б напряжение Uð эталонного источника сигнала. Реэистивная матрица каждого декадного преобразователя 3 код - ток выполнена на че- тырех резисторах (фиг.2), сопротивления которых соотносятся как 10 R:

:10 К:2110 К:4 10 R, где i

1, 2,..., и. Токи с резистивных матриц 6 поступают на преобразователь 1 ток — напряжение. На выходе преобразователя 1 (последний реализуется на операционном усилителе с резистором в цепи отрицательной обратной связи) формируется напряжение, пропорциональное значению преобразуемого кода N и„.

Для пояснения достижения повышения точности преобразования входного кода предположим, что код младших декад (» > 1) имеет нулевое значение.

Тогда ток на выходе резистивной матрицы 6.1 старшего декадного преобразователя 3.1

I = а

Поп Пап °

1 R

+ (а Ча) — +

+ цол + П- Поп 4

2R < 4Р 4R

+4(а, Ч а )+2аз+а ).

В соответствии с полученным выражением нетрудно убедиться что первые восемь входных комбинаций обеспечивают получение пропорциональных токов так же, как и в схеме известного преобразователя.

При поступлении входного кода а а а а = 1000 срабатывают сразу два

2 Э ключа блока 5.1, так как на управляющие входы этих ключей поступает единичный сигнал с выхода первого разряда регистра 4.1. В этом случае общий ток .на выходе резистивной матрицы

I = " (4+4+0+О) = 8

2. 4В

При поступлении кода 1001 срабатывает также и четвертый ключ блока

5. 1, так как на его цифровом входе появляется сигнал "1", поэтому общий ток становится равныи

5 (4+4+0+1) 9 -ф"- .

1 об

2. 4R 4

15i5313 6 выброс, равный 4 ед. М3Р, т.е. в

2 раза меньший по величине.

Формула изобретения

KIÄ =Р,;

brÇ 2 (I1

25

I = — I

N ма с 4

В известном устройстве при этом же значении получают fI»,†и уаКс

15 — ) I,, что в 1, 36 раз больше, чем

35 в предлагаемом устройстве.

Коммутационные выбросы обусловлены различием во времени срабатывания ключевых элементов. Как правило, ключевые элементы в нулевое состоя- 4О ние переходят быстрее, чем в единичное. В связи с тем, что в известной и предлагаемой схемах первые восемь кодовых комбинаций совпадают, выбросыв первых семи позициях не отличаются.

Отличие будет при изменении входного кода с кодовой комбинацией 0111 в кодовую комбинацию 1000. В известной схеме при. этом на выходе появляется выброс, равный 8 ед. М3Р (в зависимости от соответствующего приращения. тока I )., предлагаемом устройстве при аналогичной .ситуации появляется

В преобразователе абсолютные погрешности для токов Т, I<, Iy, Х1,, протекающих соответственно через резисторы 6.1.1-6; 1.4. первой декады, при одинаковых для каждого тока относительных погрешностях равны:

6IK = III 9

= — „$I,, I где I = У д/2.

Следовательно, максимальная абсолютная погрешность выходного тока первой декады

11

М=!

Максимальное значение выходного тока при входном коде 1001

Таким образом, максимальная приведенная погрешность

1. Двоично-десятичный цифроаналоговый преобразователь, содержащий преобразователь ток — напряжение, выход которого является выходной шиной, декадные преобразователи код — ток, каждый из которых выполнен в виде четырехраэрядного регистра, блока ключей и реэистивной матрицы, выход которой соединен с входом преобразователя код — напряжение, а .входы подключены к соответствующим выходам блока ключей, информационный вход которого является входной шиной опорного сигнала, информационные входы четырехразрядного регистра являются соответствующей входной шиной декады преобразуемого коца, выходы первого, третьего и четвертого разрядов соединены с соот-ветствующими входами управления бло †ка ключей, а вход записи является входной шиной занесения информации, отличающийся тем, что, с целью повышения точности преобразования и уменьшения величины коммутационных выбросов выходного сигнала, в каждый декадный преобразователь код — ток ввецен преобразователь код код, выполненный на элементе ИЛИ, выход которого соединен с вторым входом управления блока ключей, а первый и второй входы соединены с выходами соответственно первого и второго разрядов четырехразрядного регистра.

2. Преобразователь по и.1, о т— л и ч а ю шийся тем, что резистивная матрица каждого декадного преобразователя код — ток выполнена на четырех резисторах с соотношением сопротивлений (1:1:2:4),10, где

=1,2,...,n — - номер декадного преобразователя код — ток, первые выводы резисторов являются соответствующими входами резистивной матрицы, второй вывод первого резистора объединен с первыми выводами остальных резисторов и является выходом резистивной матрицы.

1575313

Влл дхЯ И.Я Вл.ы

Составитель Н.Капитанов

Редактор А.Огар Техред М,дидык Корректор С.ШекмаР

Заказ 1792 Тираж 669 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101