Демодулятор дискретных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к технике связи. Цель изобретения - повышение достоверности приема сигналов в частотно-ограниченных каналах с межсимвольной интерференцией и высоким уровнем аддитивных помех. Демодулятор дискретных сигналов содержит фильтр 1, счетчики 2 и 3, дискретизатор 5, программируемое запоминающее устройство 6, дискретно-аналоговую линию задержки 8, коммутатор 9, ЦАП 10, делитель 11, сумматор-накопитель 12, делитель 13 с переменным коэф. деления, блок синхронизации 15, решающий блок 17. Цель достигается введением детектора 4, АЦП 7, делителя 14 с переменным коэф. деления и регулируемой линии задержки 16, с помощью которых решается задача адаптивного изменения интервала анализа и сдвига момента принятия решения в решающем блоке 17 в зависимости от отношения сигнал/шум на входе демодулятора. 1 ил.

СОЮа СОВЕтСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 Н 04 L 27/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н A ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

L ":ДЯ1, ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И QTHPblTHAM

ПРИ ГКНТ .СССР (21) 4385814/24-09 (22) 12. 01.88 (46) 30. 06.90. Бюл. Ф 24 (71) Ленинградский политехнический институт им. M.È. Калинина (72) С.Б.Макаров (53) 621.396.61 (088.8) (56) Авторское свидетельство СССР

Ф 1401637, кл. Н 04 L 27/22, 1986. (54) ДЕМОДУЛЯТОР ДИСКРЕТНЫХ СИГНАЛОВ (57) Изобретение относится к технике связи. Цель изобретения — повышение достоверности приема сигналов и частотно-ограниченных каналах с межсимвольной интерференцией и высоким уровнем аддитивных помех. Демодулятор дискретных сигналов содержит фильтр

„„SU„„1 75322 А1

1, счетчики 2 и 3, дискретизатор 5, программируемое запоминающее устр-во

6, дискретно-аналоговую линию 8 задержки, коммутатор 9, ЦАП 10, делитель 11, сумматор-накопитель 12, делитель 13 с переменным коэф. деления, блок 15 синхронизации, решающий блок

17. Цель достигается введением детектора 4, АЦП 7, делителя 14 с,переменным коэф. деления и регулируемой линии 16 задержки, с помощью которых решаетСя задача адаптивного изменения интервала анализа и сдвига момента принятия решения в решающем блоке 17 в зависимости от отношения сигнал/шум на входе демодулятора.

1 ил.

1575322

Изобретение относится к технике связи и может быть использовано для когерентной обработки двоичных дискретных сигналов.

Цель изобретения - повышение достоверности приема сигналов в частотно-ограниченных каналах с межсимвольной интерференцией и высоким уровнем аддитивньгх помех. 1О

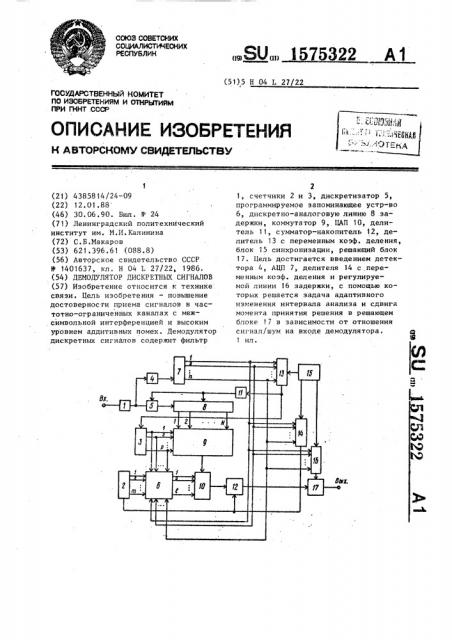

На чертеже изображена структурная

- электрическая схема предлагаемого демодулятора;

Демодулятор содержит. фильтр 1, первый и второй счетчики 2 и 3, де" тектор 4, дискретизатор 5, программируемое запоминающее устройство 6, аналого-цифровой преобразователь 7, дискретно-аналоговую линию задержки (ДАЛЗ) 8, коммутатор 9, цифроанало- 20 говый преобразователь (ЦАП) 10, первый делитель 11, сумматор-накопитель

12, второй делитель 13, делитель 14 с переменным коэффициентом деления, блок 15 синхронизации, регулируемую 25 линию 16 задержки и решающий блок 17.

Демодулятор работает следующим образом.

Аддитивная смесь x(t) полезного сигнала и шума поступает на вход 30 фильтра 1, полоса пропускания ДР которого определяется из условия

6P = 2/Д "макс rpe b, макс мальное значение интервала дискретизации равно Ь макс амакс 11 (Т

0 МакС вЂ” максимальное значение интервала анализа, И вЂ” число выборочных значений из входного процесса на интервале времени (О, 1 а „ „Д).

С выхода дискретизатора 5 последовательность выборочных значений

x(kit) (k=1,2...) из процесса x(t) поступает на вход ДАЛЗ 8, имеющей

N отводов. Время задержки между двумя соседними отводами ДАЛЗ равно 45 интервалу дискретизации Дй = Та/N и определяется частотой следования импульсов с выхода делителя 11. За время ДТ осуществляется операция дис кретной свертки выборочных значений из x(t) хранящихся в ДАЛЗ 8, с выборочными значениями импульсного отклика согласованного фильтра, записанными в виде кодовых слов в программируемом. запоминающем устройстве 6. При этом сигналу Se(t) соот55 ветствует импульсный отклик, содержащий Н отсчетных значений из Se(t).

Для получения на интервале времени

5.t .значения .дискретной свертки N выборочных значений x(t} с N выборочными значениями импульсного оТклика к N отводам ДАЛЗ Я через коммутатор

9 подключается вход опорного напряжения ЦАП 10, одновременно на цифровые входы которого поступают 1-разрядные кодовые слова, представляющие собой цифровые эквиваленты выборочных значений импульсного отклика. На выходе сумматора-накопителя 12 после сложения взвешенных с помощью ЦАП 10 значений х(kit) образуются на каждом интервале времени

Lt значения дискретной свертки. Решение в пользу того или иного символа

de принимается в решающем блоке 17 на основании сравнения значений напряжений на выходе сумматора-накопителя 12 в моменты времени kit (k =

1, 2,...) с нулевым уровнем. Рассмотрим подробнее процедуру адаптивного изменения интервала анализа и сдвига момента принятия решения в зависимости от отношения сигнал/шум на входе демодулятора дискретных сигналов. Изменение величины этого отношения, как правило, связано лишь с изменением мощности приходящего полезного сигнала при постоянном (измеренном заранее) уровне аддитивных канальных помех. Для оценки среднего уровня мощности приходящего полезного сигнала используется детектор 4 с большим значением постоянной времени детектированиями >)Т. При этом условии напряжение на выходе детектора 4 изменяется пропорционально изменению средней мощности приходящей, последовательности сигналов. С помощью ана-. лого-цифрового преобразователя 7 это напряжение преобразуется в цифровой код, служащий для управления работой (изменение коэффициентов деления) делителей 13 и 14 с переменным коэффициентом деления. При помощи этих делителей происходит изменение частоты дискретизации и частоты перезаписи выборочных значений из x(t) в ДАЛЗ 8.

В результате изменяется время интервала анализа входного процесса при сохранении на этом интервале постоянного числа выборочных значений, равного N. Определенным значениям уровня напряжения на выходе детектора 4 соответствуют свои оптимальные значения интервала анализа Тц . Синхронно с изменением частоты дискрети5

ЗО

40

50

5 1 г эации происходит и изменение частоты подключения отводов ДАЛЗ 8 с помощью коммутатора 9 к входу опорного напряжения ЦАП 10. Все возможные. формы импульсных откликов дискретно-аналогового согласованного фильтра, соответствующие определенным значениям интервалов анализа Тц, записаны в виде 1-разрядных кодовых слов в программируемом запоминающем устройстве 6, причем каждая форма отклика представлена И значениями чисел. Выбор той или иной формы импульсного откпика из памяти программируемого запоминающего устройства 6 осуществляется с помощью п-разрядного кода, поступающего на третьи входы программируемого запоминающего устройства.б. Каждому п-разрядному числу соответствует своя область памяти программируемого: запоминающего устройства 6, где записаны значения импульсного отклика для данного интервала анализа Тц. С выходов программируемого запоминающего устройства 6 1-разрядные числа поступают на цифровые входы ЦАП 10, на выходе которого получаются значения результатов синхронного перемножения выборочных значений x(t) с выходов ДАЛЗ 8 и выборочных значений импульсного отклика, хранящихся в программируемом запоминающем устройстве 6. С помощью сумматора-накопителя 12 суммируются Н значений результатов перемножения указанных напряжений, и на выходе сумматора-накопителя 12 формируется значение дискретной свертки входного процесса х(г) с соответствующим импульсным откликом на интервале анализа Тр. Такое формирование значений дискретной свертки осуществляется на каждом интервале времени Qt. В соответствии с алгоритмом работы решающий блок 17 производит анализ полярности этого напряжения в момент времени t +T . Смещение инт рвала анализа осуществляется с помощью регулируемой линии 16 задержки. Изменение времени задержки последовательности импульсов с третьего выхода блока 1,5 синхронизации осуществляется с помощью n-pas-papzoro кода, поступающего с выходов аналого-цифрового преобразователя 7..

Регулируемая линия 16 задержки может быть выполнена, например, на основе аналоговой линии, к отводам которой

75322

6 подключены ключи, управляемые дешифраторами. формула изобретения

Демодулятор дискретных сигналов, содержащий последовательно соединенные фильтр, вход которого является входом демодулятора, дискретизатор и дискретно-аналоговую линию задержки, управляющие входы которых подключены к выходу первого делителя, первый и второй счетчики, причем вход второго счетчика соединен с входом первого делителя, коммутатор, второй делитель, программируемое запоминающее устройство, решающий блок, блок синхронизации, последовательно соединенные цифроаналоговый преобразователь и сумматор-накопитель, причем М первых входов коммутатора соединены с выходами дискретно-аналоговой линии задержки, р вторых входов подключены к р выходам второго счетчика, .а выход соединен с входом опорного напряжения цифроаналогового преобразователя, 1 входов которого подключены к 1 выходам программируемого запоминающего устройства, первые р входов которого подключены к р выходам второго счетчика, а вторые m входов соединены с ш выходами первого счетчика, первый выход блока синхронизации соединен с .соответствующим входом второго делителя, отличающийся тем, что, с целью повышения достоверности приема сигналов в частотноограниченных каналах с межсимвольной интерференцией и высоким уровнем аддитивных помех, второй делитель выполнен с переменным коэффициентом деления и введены последовательно соединенные детектор и аналого-цифровой преобразователь, делитель с переменным коэффициентом деления, регулируемая линия задержки, выход которой подключен к управляющему входу решающего блока, первый вход — к второму выходу блока синхронизации, а и вторых входов — к и выходам аналого-цифрового преобразователя, которые также подсоединены к третьим п входам программируемого запоминающего устройства и к п входам второго

55 . делителя и делителя с переменным коэффициентом деления, причем соответствующий вход делителя с переменным коэффициентом деления подключен к третьему выходу блока синхронизации, 1575323

Составитель Н.Лаэарева

Редактор А.Огар Техред М:Дидык Корректор А.Обручар

3aza s792 Тираж 527 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно -издательский комбинат "Патент", r.Óàãoðoä, ул. Гагарина,101 а выход второго депителя подключен к входу первого делителя, выход делите ля с переменным коэффициентом деления подключен к входу первого счет5 чика и управляющему входу, сумматоранакопителя, вцход которого соединен,с вводом решающего блока, выход фильтра соединен с входом детектора.