Система передачи телевизионного сигнала с дифференциальной импульсно-кодовой модуляцией

Иллюстрации

Показать всеРеферат

Изобретение относится к телевидению. Цель изобретения - повышение быстродействия. Система передачи содержит канал 2 связи, на передающей части 1 АЦП 4, квантователь 5, кодер 6, блок 7 управления, блок 8 памяти и блок 9 формирования порогов квантования, а на приемной части 3 декодер 10, блок 11 управления, блок 12 памяти и блок 13 восстановления. Данная система передачи осуществляет преобразование четырехразрядных кодов эл-тов в двухразрядные выходные коды. В приемной части 3 системы двухразрядные выходные коды передающей части 1 преобразуются в четырехразрядные коды предсказанных значений эл-тов, которые затем преобразуются в аналоговый сигнал. Цель достигается за счет уменьшения времени, затрачиваемого на кодирование сообщений. Система по пп.2 и 3 ф-лы отличается выполнением квантователя 5 и блока восстановления 13, даны их ил. 2 з.п. ф-лы, 7 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„.8Ц„„ Я5532 (51)5 Н 04 N 7 13

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

К A BTOPCHGMY СВИДЕТЕЛЬСТВУ (21) 4371091/24 — 09 (22) 26.01.88 (46) 30.06.90. Бюл. ¹ 24 (72) Е.H.Ïåñòðîâ и А.Ç.Ходоровский (53) 621 ° 397.2.037.37 (088.8) (56) Претт У. Цифровая обработка изображения. M. Мир, 1982, т.2, с. 670, рис; 22.5.6. (54) СИСТЕМА ПЕРЕДАЧИ ТЕЛЕВИЗИОННОГО СИГНАЛА С ДИФФЕРЕНЦИАЛЬНОЙ iMПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ (57) Изобретение относится к телевидедению. Цель изобретения — повышение быстродействия. Система передачи содержит канал 2 связи, на передающей части 1, АЦП 4, квантователь 5, кодер 6, блок 7 управления; блок 8 памяти и блок 9 формирования порогов

2 квантования, а на приемной части 3 декодер 10, блок 11 управления, блок

12 памяти и блок 13 восстановления.

Данная система передачи осуществляет преобразование четырехразрядных .кодов эл-тов в двухразрядные. выходные коды. В приемной части 3 системы двухразрядные выходные коды передающей части 1 преобразуются в четырехразрядные коды предсказанных значений эл-тов, которые затем преобразуются в аналоговый сигнал. Цель достигается эа счет уменьшения времени, затрачиваемого на кодирование сообщений. Система по пп.2 и 3 ф-лы отличается выполнением квантователя 5 и блока 13 восстановления, даны их ил.

2 з и. ф лы, 7 ил.

1575324

55

Изобретение относится к телевидению и может быть использовано для кодирования и декодирования сигналов изображений.

Цель изобретения - повышение быстродействия.

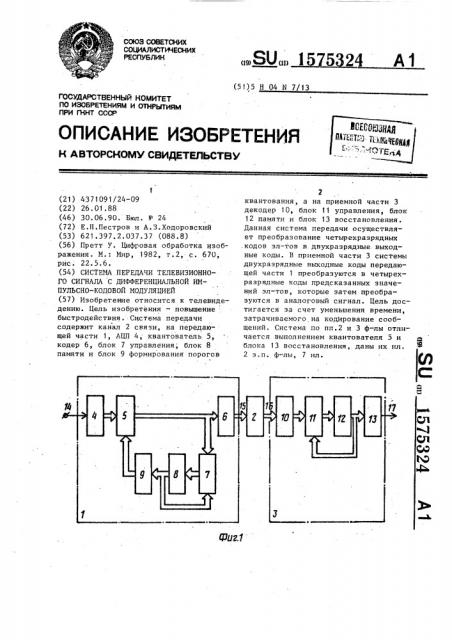

На фиг.1 представлена структур-, ная схема системы передачи телевизионного сигнала с дифференциальной импульсно-кодовой модуляцией на фиг.2 — структурная схема квантователя на фиг.3 — структурная схе- ма блока восстановления, на фиг.4— пример выполнения передающей части, на фнг.5 — пример выполнения приемной части, на фиг.6 — таблица шкалы квантования, на фнг.7 — временная диаграмма работы системы, Система передачи телевизионного сигнала с дифференциальной импульснокодовой модуляцией (фиг.1) состоит из передающей части 1, канала 2 связи и приемной части 3. Передающая часть 1 содержит аналого-цифровой преобразователь 4, квантователь 5, кодер 6, первый блок 7 управления, первый блок 8 памяти и блок 9 формирования порогов квантования. Приемная часть 3 содержит декодер 10, второй блок 11 управления, второй блок

12 памяти и блок 13 восстановления.

Вход 14 системы объединен с входом аналого-цифрового преобразователя 4, выход 15 кодера 6 является выходом передающей части 1, вход 16 декодера 10 — входом приемной части 3, а выход 17 блока 13 восстановления— выходом системы.

Квантователь 5 (фиг.2) содержит блок 18 сравнения с порогами и дешифратор 19 поддиапазонов. Блок 13 восстановления (фиг.3) содержит шифратор 20 и цифроаналоговый преобразователь 21.

Система работает следующим образом.

С приходом импульса запуска (цепи запуска и тактирования не показаны) на выходе аналого-цифрового преобразователя 4 фиксируется и-разрядный код первого элемента, который поступает на первый вход квантователя 5, а в первый 8 и второй 12 блоки памяти заносится информация о предсказываемом значении первого элемента. Эта информация с выхода первого блока 8 памяти поступает на вход блока 9 формирования порогов кванто10

1 5

45 вания и на второй вход первого блока

7 управления, а с выхода второго блока 12 памяти — на вход блока 13 восстановления и на второй вход второго блока 11 управления. В шифраторе 20 блока 13 восстановления (фиг.3) выходной сигнал второго блока 12 памяти преобразуется в и-разрядный код предсказанного значения первого элемента иэображения и после преобразования в аналоговый сигнал цифроаналоговым преобразователем 21 поступает на выход 17 системы. Одновременно блок 9 формирования порогов квантования вырабатывает и-разрядные коды порогов соответствующей шкалы квантования, которые поступают на второй вход квантователя 5 ° В квантователе

5 блок 18 сравнения с порогами (фиг.2) осуществляет сравнение двоичного кода А первого элемента изображения с и-разрядными кодами порогов (В, В,..., В,, где  — двоичный и-разрядный код порога шкалы квантования, ближайшего к нижней границе диапазона изменения входного сигнала  — код следующего, считая от нижней границы, порога шкалы В

2 -1 двоичный код порога, ближайшего к верхней границе диапазона, m — число разрядов выходного кода, формируемого на выходе 15 передающей части 1 системы) .

На выходе блока 18 сравнения с по рогами формируется единичный код

1-г,...kq, k,, где k.;=1 при А В,, и k;= О при А В . (1,2 — 1)

Этот код поступает на вход дешифратора 19 поддиапазонов, на выходе которого формируется сигнал (1е (1, 2 1), несущий информацию о том участth 1 ке шкалы квантования, внутри которого лежит значение первого элемента изображения. Алгоритм работы дешифратора

19 поддиапазонов описывается логическими выражениями вида

R4 =, р, = 1;1;;„8, = 1

6 2, 2 -1 1

Сигнал 8 поступает одновременно

8 на вход кодера 6 и на первый вход первого блока 7 управления, на второй вход которого поступает информация с выхода первого блока 8 памяти о предсказанном значении первого элемента. Такая же информация о предсказанном значении первого элемента поступает с выхода второго блока 12 на двухвходовых элементах ИЛИ 28 и 29, а первый 8 и второй 12 блоки памяти собраны на D-триггерах 30, 31, 32, 33 (фиг.4). Опрос аналого-цифрового преобразователя осуществляется через двухвходовый элемент ИЛИ 34. Декодер

10 приемной части 3 системы (фиг.5) выполнен на двухвходовом элементе И

35 и на двух двухвходовых элементах

И 36 и 37 с одним инверсным входом и на элементе ИЛИ-НЕ 38.

Система осуществляет преобразование четырехразрядных кодов элементов в двухразрядные выходные коды. В приемной части системы двухразрядные выходные коды передающей части преобразуются в четырехразрядные коды предсказанных значений элементов, которые затем преобразуются в аналоговый сигнал.

В таблице на фиг.6 показаны шкалы, используемые в процессе преобразования. Каждому предсказанному значению элемента, указанному в первой строке таблицы, соответствует своя шкала, записанная в столбце под этим значением. Заштрихованными клетками отмечены пороги квантования, а перечеркнутыми клетками отмечены уровни кван.— тования соответствующей шкалы. Принцип функционирования системы поясняется временной диаграммой на фиг.7.

В момент С, импульсом запуска обнуляются D — триггеры Т +Т, позиции

31-33 первого 8 и второго 12 блоков памяти, а триггеры То 30 этих блоков переводятся в единичное состояние.

Одновременно этим же импульсом через двухвходовый элемент ИЛИ 34 производится опрос аналого-цифрового преобразователя 4. На выходе АЦП фиксируется четырехраэрядный код первого элемента Х,: код 0110 числа 6. Шифратор 20 блока 13 .восстановления формирует на своих выходах нулевой код

0000. Соответственно на выходе цифроаналогового преобразователя 21 устанавливается напряжение,.совпадающее с нижней границей диапазона.

5 15753 памяти на второй вход второго блока

11 управления. Кодер 6 преобразует сигнал g, в m-разрядный выходной код (m (n) . Этот код с выхода канала 2 связи поступает на вход 16 декоде5 ра 10 ° В декодере 10 m-разрядный выходной код преобразуется в сигнал

g;, поступающий на первый вход второго блока 11 управления. Первый 7 и второй 11 блоки управления формируют на входах первого 8 и второго

12 блоков памяти сигналы управления записью информации о предскаэываемом значении второго элемента. Первым тактовым импульсом на выходе аналого-цифрового преобразователя 4 фиксируется и-разрядный двоичный код второго элемента изображения,, а в первый 8 и второй 12 блоки памяти 20 заносится информация о предсказываемом значении второго элемента. Предсказанное значение второго элемента иэображения преобразуется блоком 13 восстановления в аналоговый сигнал 25 и поступает на выход 17 .системы.

Одновременно на втором входе квантователя 5 в соответствии с информацией о предсказанном значении второго элемента формируются коды лоро- 30 гов квантования очередной шкалы. Квантователь осуществляет сравнение кода второго элемента с этими порогами и формирует сигнал 8 об участке шкалы, внутри которого находится значение второго элемента. В соответствии с этим сигналом кодер 6 .формирует новое значение выходного. кода, а первый

7 и второй 11 блоки управления формируют на входах первого 8 и второго 4п

12 блоков памяти сигналы управления записью информации о предсказываемом значении третьего элемента. Вторым тактовым импульсом эта информация за- . носится в первый 8 и второй 12 блоки 45 памяти, а на выходе аналого †цифрового преобразователя фиксируется код третьего элемента. Далее весь процесс обработки повторяется. с

Система передачи телевизионного сигнала может быть выполнена как показано на.фиг.4 и 5.

В квантователе 5 блок 18 сравнения с порогами выполнен на компараторах кодов CII, (фиг.4 позиции 22, 23, 24), а дешифратор 19 поддиапазонов— на двухвходовых элементах И с одним инверсным входом (позиции 25, 26) и на элементе НЕ 27. Кодер 6 выполнен

В соответствии с информацией, записанной в первом блоке 8 памяти, блок 9 формирования порогов квантования вырабатывает четырехразрядные коды порогов шкалы, приведенной в первом столбце таблицы (фиг.6), двоичные коды уровней 2, 5, 9 диапазона (0,151 возможных значений элементов. 1575324

В результате сравнения кода первого элемента с порогами в блоке 18 сравнения с порогами формируется единичный код 100, который поступает в дешифратор 19 поддиапазонов. На одном из выходов дешифратора появляется единичный сигнал g, поступающий на вход первого блока 7 управления. Одновременно в кодере 6 формируется выходной код 00, несущий. информаций об участке (5,8) первой шкалы, которому принадлежит Х . Работа кодера 6 происходит в соответствии с логическими выражениями 15

С1 = g) g4;

С =я,+g,, Этот код по каналу 2 связи поступает на вход 16 приемной части 3 системы. В декодере 10 по двоичному коду

С,С восстанавливается сигнал g -. .Pa1 бота и структура декодера описывается выражениями: Р, = С С, g =С С, ЮЗ C((У 84 С4 2

Восстановленный таким образом сигнал g подается на вход второго бло3 ка 11 управления.

Первый 7 и второй 11 блоки управ- 30 ления работают аналогично. Они формируют сигналы .управления записью единицы в тот триггер блока памяти, который соответствует уровню квантования найденного участка шкалы — еди- 35 ничный сигнал íà D-входе триггера Т, соответствующего уровню 6 участка (5,8) (см. таблицу на фиг.б). Логические выражения, выборочно описывающие работу и структуру первого . и 40 второго блоков управления, имеют вид

Т, = (Т,+Т, +Т,) g,;

Т, (Т+ Т,) g+(T,+ò +Т +т +

Т вЂ” (Т,+Т) g+(Т+Т) g

Т вЂ” (Т6+Т ) g +(Т +Ти+Т ) g y

О где Т," (iG 10,151) - логические пере- 50 менные, описывающие управляющие сигналы, подаваемые на D-входы соответствующих триггеров первого 8 и второго 12 блоков памяти.

Первым тактовым импульсом в момент ,времени t триггеры Т первого 8 и второго 12 блоков памяти переводятся в единичное состояние, а все остальные — в нулевое. Одновременно на выходе аналого-.цифрового преобразователя 4 фиксируется четырехразрядный код 1000 второго элемента Х (фиг.7).

На выходе шифратора 20 образуется двоичный код 0110 числа 6, который после прохождения через цифроаналоговый преобразователь 21 преобразуется в соответствующий аналоговый уровень (фиг.7) ° В соответствии с новой информацией, .записанной в первом блоке 8 памяти, на выходе блока 9 формирования порогов квантования вырабатываются коды порогов., соответствующие уровням 5, 8, 12 (фиг.б). После сравнения с порогами и дешифрации формируется сигнал g (в нашем при,1 мере g ) об участке (8, 11), которому принадлежит значение второго элемента Х . В соответствии с этим сиг-, налом формируются единичные сигналы на D-входах триггеров Т блоков па9 мяти.

С приходом очередного тактового импульса триггеры Т первого 8 и вто7 рого 12. блоков памяти переводятся в единичное состояние, а все остальные — в нулевое. Соответственно на выходе цифроаналогового преобразователя 21 устанавливается аналоговый уровень числа 9. Далее весь процесс преобразования повторяется..Восстановленный сигнал X(t) на выходе цифроаналогового преобразователя 2.1 появляется с задержкой на такт по отношению к входному сигналу X(t).

Для иллюстрации качества воспроизведения первичного сигнала на, фиг.7 пунктиром показана ступенчатая функция, являющаяся сдвинутой на такт влево. функцией X(t).

В предлагаемой системе передачи телевизионного сигнала благодаря введению новых блоков и связей удалось исключить из алгоритма функционирования системы операции сложения и вычитания.и соответствующие блоки из структуры системы. При этом время, затрачиваемое на кодирование сооб-. щений, оказывается существенно меньше, чем в прототипе. При прочих равных условиях общий выигрыш в быстродействии определяется соотношением суммарного времени .выполнения операций вычитания и суммирования в прототипе и формировании сигналов управления памятью в предлагаемой системе. Конкретные чиспенные значения

1 выигрыша зависят оТ параметров сНс

Формула и з о 6 р е т е н и я

1. Система передачи телевизионного сигнала с дифференциальной импульсно-кодовой модуляцией, состоящая из передающей и приемной частей, соединенных последовательно через канал связи, передающая часть содержит 20 аналого-цифровой преобразователь, вход которого является входом систе— мы, и последовательно соединенные квантователь и кодер, выход которого является выходом передающей части, 25 приемная часть содержит декодер, вход которого является входом приемной части, и блок восстановления, выход которого является выходом сис-, темы, отличающаяся тем, что, с целью повышения быстродействия, в передающую часть системы введены последовательно соединенные первый блок управления, первый блок памяти и блок формирования порогов кван1

30 (g 15753 темы (числа разрядов АЦП и числа двоичных символов в выходном коде), а также от выбранной элементной базы. В среднем время, затраченное предлагаемой системой от момента получения

5 кода на выходе АЦП до момента формирования информации о предсказанном значении очередного элемента, уменьшается по сравнению с прототипом в

2-5 раз.

24 1О тования, выход которого соединен с вторым входом квантователя, первый вход которого соединен с выходом аналого-цифрового преобразователя, выход квантователя соединен с первым .входом первого блока управления, второй вход которого соединен с выходом первого блока памяти, в приемную часть введены последовательно соединенные второй блок управления и второй блок памяти, выход которого соединен с входом блока восстановления и с вторым входом второго блока управления, первый вход которого соединен с выходом декодера °

2. Система по п.1, о т л и ч а ющ а я с я тем, что квантователь выполнен в виде последовательно соединенных блока сравнения с порогами и дешифратора поддиапазонов, выход которого является выходом квантователя, а первый и второй входы блока сравнения с порогами — соответственно первым и вторым входами квантователя.

3. Система по п.1 о т л и ч а ющ а я с я тем, что блок восстановления выполнен в виде последовательно соединенных шифратора и цифроаналогового преобразователя, выход которого является выходом блока восстановления, а вход шифратора — входом блока восстановления.

3575324

ФИ2. 4

1575324

С1 ср

Фиг.Ю

1575324

ff

В

Ю

ff 0

М

6 ф

3 г

Фиг. 7

Составитель А.Цветков

Редактор Н.Киштулинец Техред М.Дидык. . Корректор Э.Лончакова

Заказ 1792 Тираж 534 Подписное

ВНИИПИ Государственного комитета по изобретенияМ и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д, 4(5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101