Устройство для отображения информации на экране телевизионного индикатора

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для отображения информации и визуального контроля состояния объектов. Целью изобретения является повышение информационной емкости устройства. Устройство содержит генератор 1 импульсов, счетчик 2, блок 3 синхронизации, блок 4 управления, регистр 5, формирователь 6 управляющих сигналов, мультиплексор 7, блок 8 памяти, формирователь 9 видеосигналов, индикатор 10 с соответствующими связями. Генератор 1 импульсов, первый счетчик 2 и блок 3 синхронизации вырабатывают управляющие импульсы, синхронизирующие работу блоков устройства. Входная информация через регистр 5 записывается в блок 8 памяти, а затем считывается для отображения на экране индикатора 10. Формирователь 6 управляющих сигналов, в зависимости от режима работы, определяет количество одновременно отображаемых объектов, доводя их число до 2000 - 4000, повышая тем самым информационную емкость устройства. 3 з.п. ф-лы, 7 ил., 1 табл.

1578740

Изобретение относится к вычислительной технике и может быть использовано для отображения информации и визуального контроля состояния обьектов.

Целью изобретения является повышение информационной емкости устройства.

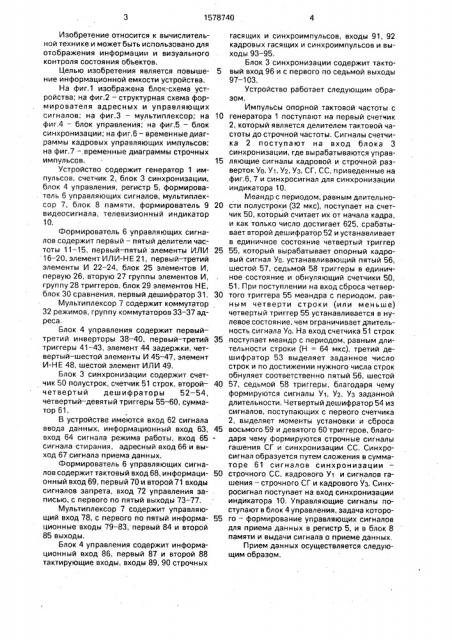

На фиг.1 изображена блок-схема устройства; на фиг.2 — структурная схема формирователя адресных и управляющих сигналов; на фиг,3 — мультиплексор; на фиг.4 — блок управления; на фиг.5 — блок синхронизации; на фиг,6 — временныедиаграммы кадровых управляющих импульсов; на фиг,7 — временные диаграммы строчных импульсов, Устройство содержит генератор 1 импульсов, счетчик 2, блок 3 синхронизации, блок 4 управления, регистр 5, формирователь 6 управляющих сигналов, мультиплексор 7, блок 8 памяти, формирователь 9 видеосигнала, телевизионный индикатор

10, Формирователь 6 управляющих сигналов содержит первый — пятый делители частоты 11 — 15, первый-пятый элементы ИЛИ

16 — 20, элемент ИЛИ-НЕ 21, первый-третий элементы И 22 — 24, блок 25 элементов И, первую 26, вторую 27 группы элементов И, группу 28 триггеров, блок 29 элементов НЕ, блок 30 сравнения, первый дешифратор 31.

Мультиплексор 7 содержит коммутатор

32 режимов, группу коммутаторов 33 — 37 адреса, Блок 4 управления содержит первыйтретий инверторы 38 — 40, первый — третий триггеры 41 — 43, элемент 44 задержки, четвертый — шестой элементы И 45 — 47. элемент

И-НЕ 48, шестой элемент ИЛИ 49, Блок 3 синхронизации содержит счетчик 50 полустрок, счетчик 51 строк, второй— четвертый дешифраторы 52-54, четвертый-девятый триггеры 55-60, сумматор 61.

В устройстве имеются вход 62 сигнала ввода данных, информационный вход 63, вход 64 сигнала режима работы, вход 65 сигнала стирания, адресный вход 66 и выход 67.сигнала приема данных.

Формирователь 6 управляющих сигналов содержит тактовый вход 68, информационный вход 69, первый 70 и второй 71 входы сигналов запрета, вход 72 управления записью, с первого по пятый выходы 73 — 77.

Мультиплексор 7 содержит управляющий вход 78, с первого по пятый информационные входы 79 — 83, первый 84 и второй

85 выходы.

Блок 4 управления содержит информационный вход 86, первый 87 и второй 88 тактирующие входы, входы 89, 90 строчных

°

55 гасящих и синхроимпульсов, входы 91, 92 кадровых гасящих и синхроимпульсов и выходы 93 — 95.

Блок 3 синхронизации содержит тактовый вход 96 и с первого по седьмой выходы

97 — 103.

Устройство работает следующим образом.

Импульсы опорной тактовой частоты с генератора 1 поступают на первый счетчик

2, который является делителем тактовой частоты до строчной частоты. Сигналы счетчика 2 поступают на вход блока 3 синхронизации, где вырабатываются управляющие сигналы кадровой и строчной разверток Уо, У, V2, У3, СГ, СС, приведенные на фиг,6, 7 и синхросигнал для синхронизации индикатора 10, Меандр с периодом, равным длительности полустроки (32 мкс), поступает на счетчик 50, который считает их от начала кадра, и как только число достигает 625, срабатывает второй дешифратор 52 и устанавливает в единичное состояние четвертый триггер

55, который вырабатывает опорный кадровый сигнал Уо, устанавливающий пятый 56, шестой.57, седьмой 58 триггеры в единичное состояние и обнуляющий счетчики 50, 51, При поступлении на вход сброса четвертого триггера 55 меандра с периодом, равным четверти строки (или меньше) четвертый триггер 55 устанавливается в нулевое состояние, чем ограничивает длительность сигнала Ур. На вход счетчика 51 строк поступает меандр с периодом, равным длительности строки (Н = 64 MKc), третий дешифратор 53 выделяет заданное число строк и по достижении нужного числа строк обнуляет соответственно пятый 56, шестой

57, седьмой 58 триггеры, благодаря чему формируются сигналы У, У2, Уз заданной длительности. Четвертый дешифратор 54 из сигналов, поступающих с первого счетчика

2, выделяет моменты установки и сброса восьмого-59 и девятого 60 триггеров, благодаря чему формируются строчные сигналы гашения СГ и синхронизации СС, Синхросигнал образуется путем сложения в сумматоре 61 сигналов синхронизации строчного СС, кадрового У и сигналов гашения — строчного СГ и кадрового Уз. Синхросигнал поступает на вход синхронизации индикатора 10. Управляющие сигналы поступают в блок 4 управления, задача которого — формирование управляющих сигналов для приема данных в регистр 5, и в блок 8 памяти и выдачи сигнала о приеме данных, Прием данных осуществляется следующим образом. . 578740

ЭВМ выставляет на информационный вход 63 устройства (фиг.1) первое слово данных, содержащее информацию об объекте, контрольный разряд и часть адреса канала.

По сигналу "Ввод" на входе признака ввода 5 данных блока 4 управления (фиг,4) при наличии сигнала Уо на первом тактирующем входе блока 4 управления первый триггер 41; устанавливается в единичное состояние (вырабатывается сигнал У<. Сигнал У4 через,10 ! элемент 44 задержки поступает на вход син- хронизации третьего триггера 43 (типа iK), на второй информационный вход которого (I) поступает сигнал контрольного разряда с третьего выхода регистра 5 через инфор- 15 мационный вход 86 блока 4 управления, Прямый выход третьего триггера 43 соединен с первым информационным (К) его входом, При таком использовании третьего триггера 43 он может перейти в единичное 20 состояние только при единичном значении контрольного разряда по заднему фронту сигнала У4, Однако при следующем прохождении сигнала У4 третий триггер 43 перейдет в исходное (нулевое) состояние при 25 любом значении контрольного разряда, Это определяет строгую последовательность приема, Первое слово данных пропускается в регистр 5 непосредственно с информационного входа 63 устройства. а второе слово, 30 содержащее вторую часть адреса, пропускается на входы блока 8 памяти через мультиплексор 7. Сигнал У4 переводится в нулевое состояние сбросам первого триггера 41 в исходное состояние по установле- 35 нию второго триггера 42 в единичное состояние. Сигнал установки второго триггера 42 в единичное состояние формируется элементом И 46 при наличии сигналов У .

СГ, Уз. Сброс второго триггера 42 Осущест- 40 вляется сигналом СС. Это означает, что триггер 42 будет находиться в единичном состоянии (а значит, и выдавать сигнал в

ЭВМ через первый выход 57 блока 4) только после окончания сигнала кадрового гаше- 45 ния (Уэ) и длительность его не превышает расстояния между фронтами сигналов СГ и .СС, В некоторых ЭВМ сигнал "Ввод" выдается нулем, поэтому на элемент И 45 входа признака ввода данных блока 4 управлен .я 50 он подается через инвертор 38. Сигнал разрешения приема на регистр 5 формируется элементом И 47 при наличии сигнала У4 в исходном состоянии третьего триггера 43.

Для работы блока Р памяти необходимо 55 формировать два управляющих сигнала: сигнал режима, определяющий режим работы — "Чтение" или "Запись":, сигнал разрешения — разрешающий запись или чтение (в зависимости от режима) данных по указанному адресу. Сигнал режима У5 формируется элементом И--НЕ 48 при наличии сигналов Уо, Уэ, У4 при единичном состоянии третьего триггера 43. Это означае, что режим записи устанавливается во время cvirнала гашения Уз с задержкой на длительность сигнала Уо (необходимой на случай задержки данных относительно сигнала "Ввод" ) только после того, как записано первое слово в регистр 5, имеющее единичный контрольный разряд, и имеется второе слово на информационном входе устройства. Сигнал разрешения записи Ув фсрмируется элементом ИЛИ 49 при наличии сигнапов Ys, У2, У1, это означает, что данный сигнал существует лишь во Время режима записи (Ys) и по времени находится внутри этого сигнала, Сигналы разрешения и режима выдаются соответственно с третьего и четвертого выходов блока 4. Элемент

44 задержки вводится для компенсации разных путей распространения сигнала У и контрольного разряда. B связи с многорежимной работой устройства сигналы У5, Уg не выдаются непосредственно в блок 8 памяти, а поступают соответственно на вход признака записи формирователя 6 и Второй информационный вход мультиплексора 7. К основным режимам работы блока 8 памяти (" Запись", "Чтение" ) добавляется режим

"Очистка", являющийся частным случаем режима "Запись, Исгольэуетсх он тогда, когда нужно быстро(В течение Одного кадра) обнулить или записать одно и то же значение в определенную область блока 8 памяти, Сигнал "Очистка" нулем вводится с входа признака стирания устройства ча Одноименный вход формирователя 6, первый вход элемента И 24, на второй вход которого

ВВОДитсЯ сигнал У5. Сигнал с ВыхОДа эле мента И 24 подается на второй управляющий Вход(входуправления режимом работы — "Запись" / "Чтение" ) блока памяти. B устройстве используется несколько режимов индикации. Код режима работь. подается через Одноименный Вход устройства на перВый Вход блока 25 элемент =- И. Поскольку индикация производится только во время активных строк, а прием ичформации во время кадрового гашения (за исключением режима "Очистка" ), то пр" ем информации не зависит от режима индикации, поэтому блок 25 пропускает код режима индикации только тогда, когда сигнал режима У принимает единичное значен. е. При нулевом значении сигнала У5. при ":.þáîì коде режима индикации формирователь 6 формирует код, сдответству ощий режиму записи, по которому коммутатор 32 режимов пропускает сигна.:, разрешения записи У6. поступаю1578740 щий с второго информационного входа мультиплексора 7, на второй выход мультиплексора 7 и, следовательно, на первый управляющий вход (вход разрешения) блока 8 памяти, а коммутаторы 33 — 37 адреса пропускают код адреса контролируемого объекта (канала), поступающий на первый и пятый информационные входы мультиплексора 7, на вход адреса блока 8 памяти. Блок 8 памяти запоминает данные, находящиеся в регистре 5, по пропущенному мультиплексором

7 адресу во время нулевых значений сигналов У5 У6.

Во время активных строк происходит отображение информации, находящейся в блоке 8 памяти. Имеется несколько режимов индикации, отличающихся разным количеством контролируемых объектов, При отображении информации о состоянии максимального количества объектов (режим

"Поле" ) для каждого объекта на экране индикатора может быть отведена наименьшая площадь (канал). В других режимах индикации при отображении информации о состоянии меньшего числа контролируемых объектов размер канала увеличивается и улучшается цветовая разрешающая способность каналов. Для удобства оператора все поле разбивается на зоны, каждая из которых в свою очередь, разбивается на подзоны (сектора), а те, в свою очередь, на подзоны следующего порядка и т.д. Зоны разделяются между собой черными горизонтальными и вертикальными чертами (разделителями). При индикации одной какой-либо зоны (подзоны) разделители остаются на своих местах, но разделяют уже подзоны данной зоны (подзоны).

Обычно соответствие между кодами объектов (адреса элементов памяти, в которых хранится информация о данном объекте) и каналами (укрупненные элементы экрана индикатора) производится путем дешифрации состояния счетчика элементов развертки, синхронизированного с разверткой.

В устройстве используется периодичность повторения разделителей и каналов.

Реализуется это посредством делителя тактовой частоты, содержащего пять делителей

11 — 15 частоты (фиг.2). Особенностью делителей 11, 13, 14 является то, что они формируют пачки импульсов, разделенных строго фиксированными промежутками (разделителями).

Деление тактовой частоты, поступающей на информационный вход делителя 1, производится следующим образом. Делитель 11 на выходы первой группы выходов выдает меандры, периоды которых кратны горизонтальных разделителей. Эти сигналы

10 поступают на делитель 11 через элементы

ИЛИ 16, 17, 19, Делитель 12 считает количе20

50 разрядов адреса при приемеданных, во второй строке (2а) приведено естественное расположение разрядов на выходах делителей

40 степени двойки периода тактовой частоты, Деление производится до частоты, период которой равен длительности развертки по строке одной эоны. Деление тактовой частоты не производится во время вертикальных разделителей, ширина которых задается самим делителем 11, а также во время сигналов гашения Уз, СГ и во время сигналов У1 ство зон, укладывающихся в одной строке

Гашение делителя 12 производится во время сигналов гашения Уз, СГ и во время сигналов Ут горизонтальных разделителей, поступающих на делитель 12 через элементы ИЛИ 17, 19. Делитель 13 строчной частоты считает количество строк, укладывающихся в канале при отображении всех контролируемых объектов (режим "Поле"), Гашение делителя 13 производится во.время сигналов Уз, У7, поступающих на делитель 13 через элементы ИЛИ 18, 19. Необходимость в делителе 13 возникает из-за того, что в стандартных индикаторах количество строк в кадре строго определенно и, как правило, не является степенью двойки.

Если из них использовать только количество строк, являющихся степенью двойки, то это приводит к неэффективному использованию площади экрана индикатора. Делитель

14 считает количество каналов, укладывающихся по вертикали в одной зоне в режиме

"Поле", а делитель 15 — количество зон, укладывающихся по вертикали на экране индикатора. Гасится делитель 14 во время сигналов Уз, У7, поступающих через элемент

ИЛИ 19, а делитель 15 — во время сигнала

Уз, Зонная кодировка знаков предъявляет дополнительные требования к организации мультиплексора, Переход от обычного кодирования к зонному поясняется в таблице, где AI...A1, В и ... В1, Cn... C, Dk... D ) — разряды на выходах пятого 15, четвертого 14, второго

12., первого 11 делителей (фиг,2), расположенные в последовательности убывания их веса. В первой строке таблицы показано естественное позиционное расположение

11, 12, 14, 15, соответствующих коду адреса в режиме "Поле", В третьей строке (2в) приведено расположение разрядов при зонном кодировании в режиме "Поле". В строке За показано расположение разрядов в режиме

"Зона". В старших разрядах находится код зоны, а в остальных — разряды с выходов шин при обычном (естественном) кодирова1578740

55 нии, а в строке Зв при зонном кодировании.

При этом размер каждого канала увеличивается в п раз (количество зон в поле), поэтому I младших разрядов четвертого делителя 14 и и младших разрядов первого делителя 11 не используются, Аналогичное расположение разрядов используешься и при выделении различных подзон, как показано в строках 3+i, а; 3+i, Ь, Несколько изменяется расположение разрядов в режиме

"Сектор" (строка 4+i): в старших разрядах располагается код сектора, далее располагаются разряды второго делителя 12 и старшие разряды первого делителя 11, На управляющие входы коммутаторов 32 — 37 подается код режима с управляющего входа мультиплексора, по которому каждый коммутатор подключает заданный кодом режима вход к выходу коммутатора, поэтому на первый выход мультиплексора 7 (фиг.3) поступают сигналы, соответствующие выбранной кодом режима строке таблицы (при индикации используется только зонный код). В связи с тем, что размеры канала в каждом режиме различны, сигналы разрешения, поступающие на первый управляющий вход блока 8 памяти с выхода коммутатора 32 режимов, тоже различны. В режиме приема это сигнал Ув, поступающий с третьего выхода блока 4 управления через второй информационный вход мультиплексора 7. При индикации это какой-либо из сигналов, поступающих через четвертый информационный вход (каждый сигнал по своему проводу), соответствующий выбранному режиму индикации. Формируются эти сигналы группой 28 триггеров . (фиг.2) следующим образом. Первая под, группа первой группы выходов делителя 11 содержит меандры, периоды которых являются степенью двойки периода тактовой частоты, вплоть до меандра, период которого равен сумме ширины канала (в режиме "Поле") и разделителя между каналами. Эта группа подается на входы элемента И

26 — 1 первой группы 26 элементов И непосредственно, а на входы элемента И 27 — 1 группы 27 — после инвертирования каждого меандра в блоке 29, На один из входов этих же элементов подается тактовая частота, кроме того, на один из входов элемента И

27 — 1 группы 27 подается проинвертированный элементом НЕ блока 29 сигнал Уа, являющийся логической суммой сигналов Уз, СГ, Yz, т.е.

Ув = Уз + СГ + Y7, (1)

Сигнал с выхода элемента И 27 — 1 поступает на установочный вход триггера 28 — 1 группы

28 и устанавливает его в единичное состояние. Сигнал с выхода элемента И 26-1 посту5

i0

40 пает на вход сброса этого же триггера и устанавливает его в исходное (нулевое) состояние. Физически это означает, что триггер 28 — 1 устанавливается в единичное состояние через полпериода тактовой частоты от начала меандра, период которого равен сумме ширины канала и разделителя и сбрасывается за полпериода тактовой частицы до окончания данного меандра. Это значит, что размер разделителя равен периоду тактовой частоты. Использование инверсии сигнала У8 в элементе И 27-1 приводит к тому, что сигнал разрешения на выходах группы 28 триггеров не формируется при сигналах гашения и разделителях.

Аналогично формируется сигнал разрешения при следующем режиме индикации. Поскольку в следующем режиме индикации отображается на экране только одна зона, то ширина канала увеличивается во столько раз, сколько зон укладывается по горизонтали в предыдущем режиме, а это значит, что к предыдущим сигналам должны добавиться еще сигналы второй подгруппы первой группы выходов делителя 11. На элемент И 26 — 2 группы 26 они поступают непосредственно, а на элемент И 27 — 2 группы 27 — через элементы НЕ блока 29. Сигналы с выходов элементов И 27 — 2, 26 — 2 поступают соответственно на вход установки и сброса триггера 28-2, на выходе которого формируется сигнал разрешения при данном режиме индикации. Аналогично формируются и остальные сигналы разрешения.

Сигнал яркости (инверсия сигнала гашения), поступающий с пятого выхода формирователя 6 на второй информационный вход формирователя 9 видеосигнала, формируется элементами ИЛИ 20, ИЛИ-НЕ 21, И 22, 23, блоком 30 сравнения, первым дешифратором 31 согласно логическому соотношению

Яр =У8+У9 Y>o+Yg Y+

+.. т) (2) где Yg — сигнал режима "Сектор", вырабатываемый первым дешифратором 31;

Yg — сигнал, инверсный сигналу Yg, вырабатываемый первым дешифратором 31;

Y>o — сигнал вертикального разделителя между зонами; поступающий с делителя 11;

Ср — сигнал, инверсный сигналу сравнения (Ср), поступающий с инверсного выхода блока 30 сравнения;

fo — сигнал с тактовой частоты, à f>...f результат, Формирователь 9 видеосигнала преобразует код цвета, поступающий на первый

1578740

12 информационный вход из блока 8 памяти, и яркостный сигнал, поступающий на второй информационный вход из формирователя 6 режимов индикации, в составляющие сигналов цветности R, G, В для индикатора 10.

Формула изобретения

1, Устройство для отображения информации на экране телевизионного индикатора, содержащее формирователь видео игнала, блок памяти, мультиплексор, регистр, блок управления, блок синхронизации, счетчик, генератор импульсов, выход которого соединен с тактовым входом счетчика, выход которого подключен к тактовому входу блока синхронизации, первый выход которого соединен с синхровходом телевизионного индикатора, второй, третий и четвертый выходь! подключены соответственно к первому тактирующему входу и входам кадрового синхроимпульса и кадрового гасящего импульса блока управления, вход сигнала ввода данных которого является входом сигнала ввода данных устройства, выходом сигнала приема данных которого является первый выход блока управления, второй выход которого соединен с управляющим входом регистра, информационный вход которого является информационным входом устройства, первый, второй и третий выходы регистра соединены соответственно с первым информационным входом мультиплексора и информационными входами блока памяти и блока управления, третий выход которого подключен к второму информационному входу мультиплексора, превый выход которого соединен с адресным входом блока памяти, выход которого г одкг ючен к первому информационному входу формирователя видеосигнала, выходы которого соединены с информационными входами телевизионного индикатора, о т- л и ч а ю щ е е с я тем, что, с целью повышения информационной емкости !устройства, оно содержит формирователь управляющих сигналов, тактовый вход которого подключен к выходу счетчика, а первый вход сигнала запрета — к четвертому выходу блока синхронизации, пятый и шестой выходы которого соединены соответственно с вторым тактирующим входом и входом строчного синхроимпульса блока управления, а седьмой выход- с вторым входом сигнала запрета формирователя упрравляющих сигналов и входом строчного гасящего импульса блока управления, четвертый выход которого подключен к входу управления записью формирователя управляющих сигналов, входы сигнала режима работы и сигнала стирания которого являются соответственна входами сигнала режима работы и сигна5

ЗО

35 ла сти, !ния устройства, первый, вт;рой и третий выходы формирователя управляющих сигналов соединены соответственно с третьим и четвертым информационными и управляющим входами мультиплексора, пятый информационный вход которого соединен с информационным входом регистра, а шестой информационный вход является адресным входом устройства, второй выход мультиплексора подключен к входу управления. считыванием блока памяти, вход управления записью которого соединен с четвертым выходом формирователя управляющих сигналов, информационный вход которого подключен к выходу блока памяти, а пятый выход — к второму информационному входу формирователя видеосигнала.

2. Устройство по п.1, о т л и ч а ю щ е ес я тем, что формирователь управляющих сигналов содержит первый, второй, третий, четвертый и пятый делители частоты, первый, второй, третий, четвертый и пятый элементы ИЛИ, первый, второй и третий элементы И, первый дешифратор, блок элементов И, первую и вторую группы элементов И, группу триггеров, элемент ИЛИ вЂ” НЕ, блок элементов НЕ, блоксравнения, первый информационный вход которого является информационным входом формирователя, а второй информац Io! Hj,!é вход. подключен к выходу пятого делителя частоты, третий информационный вход блока сравнения подключен к первому выходу четвертого делителя частоты, который соединен с выходом пятого делителя частоты, первый выход четвертого делителя частоты и выходы разрядов первого и второго делителей частоты являются первым выходом формирователя, второй выход четвертого делителя частоты соединен с тактовым входом пятого делителя частоты и первым входом четвертого элемента ИЛИ, второй вход которого соединен с управляющим входом пятого делителя частоты и является первым входом сигнала запрета формирователя, выход четвертого элемента ИЛИ соединен с управляющим входом четвертого делителя частоты, первы- ми входами второго элемента ИЛИ и третьего элемента ИЛ И, выход которого подключен к управляющему входу третьего делителя частоты, выход которого соединен с тактовым входом четвертого делителя частоты и вторым входом третьего элемента

ИЛИ, выход первого элемента ИЛИ подключен к управляющему входу первого делителя частоты, выход переноса которого соединен с тактовым входом второго делителя частоты и первыми входами первого элемента ИЛИ, второго элемента И и блока элементов НЕ, первый выход которого под13

1578740

14 ключен к первому входу первого элемента

И, выход которого соединен с первым входом элемента ИЛИ вЂ” НЕ, второй вход которого соединен с управляющим входом второго делителя частоты, вторыми входами блока элементов НЕ и первого элемента ИЛИ и выходом второго элемента ИЛИ, второй вход которого является вторым входом сигнала запрета формирователя, третий вход элемента ИЛИ вЂ” НЕ соединен с выходом второго элемента И, второй вход которого подключен к первому выходу первого дешифратора, вход которого соединен с первым входом блока элементов И и является входом сигнала режима работы формирователя, второй выход первого дешифратора подключен к второму входу первого элемента И, третий вход которого соединен с выходом блока сравнения, а четвертый вход — с выходом пятого элемента ИЛИ, первый вход которого соединен с тактовыми входами первого и третьего делителей частоты, первыми входами первых элементов И первой и второй групп и является тактовым входом формирователя, выходы разрядов, кроме старшего, первого делителя частоты соединены соответственно со всеми входами, кроме первого, пятого элемента ИЛИ, вторыми входами элементов И первой группы и, начиная с третьего,.входами блока элементов НЕ, второй и третий выходы которого подключены соответственно к второму и третьему входам первого элемента И второй группы, а выходы, начиная с четвертого, — к первым входам элементов И, кроме первого, второй группы, вторые входы которых подключены соответственно к выходам предыдущих элементов И группы, выходы элементов И второй группы соединены соответственно с установочными входами триггеров группы, первые входы элементов

И, кроме первого, первой группы подключены соответственно к выходам предыдущих элементов И группы, выходы элементов И первой группы соединены соответственно с входами сброса триггеров группы, выходы которых являются вторым выходом формирователя, первый вход третьего элемента И является входом сигнала стирания формирователя, второй вход блока элементов И соединен с вторым входом третьего элемента И и является входом сигнала записи формирователя, выходы блока элементов И, третьего элемента И и элемента ИЛИ-НЕ являются соответственно третьим, четвертым и пятым выходами формирователя.

3, Устройство по п.1, о т л и ч а ю щ е ес я тем, что мультиплексор содержит группу коммутаторов адреса и коммутатор режимов, управляющий вход которого соединен

55 с управляющими входами коммутаторов адреса и является управляющим входом мультиплексора, первые информационные входы коммутаторов адреса соединены между собой и является третьим информационным входом мультиплексора, вторые информационные входы коммутаторов адреса младших разрядов соединены между собой и являются первым информационным входом мультиплексора, вторые информационные входы коммутаторов старших разрядов соединены между собой и являются пятым информационным входом мультиплексора, первый и второй информационные входы коммутатора режимов являются соответственно вторым и четвертым информационными входами мультиплексора, третьи информационные входы коммутаторов адреса являются шестым информационным входом мультиплексора, выходы группы коммутаторов адреса и коммутатора режимов являются соответственно первым и вторым выходами мультиплексора.

4, Устройство по п.1, о т л и ч а ю щ е ес я тем, что блок управления содержит первый, второй, третий инверторы, первый, второй, третий триггеры, элемент задержки, четвертый, пятый, шестой элементы И, элемент И вЂ” НЕ, шестой элемент ИЛИ, первый и второй входы которого являются соответственно входом кадрового синхроимпульса и вторым тактирующим входом блока, а третий вход подключен к выходу элемента И—

НЕ, первый вход которого соединен с выходом второго инвертора, а второй вход, соединенный с входом третьего инвертора, является входом кадрового гасящего импульса блока, третий вход элемента И-НЕ соединен с первым информационным входом и прямым выходом третьего триггера, инверсный выход которого соединен с первым входом шестого элемента И, а тактовый вход подключен к выходу элемента задержки, вход которого соединен с выходом первого триггера, вторым входом шестого элемента И, четвертым входом элемента ИНЕ и первым входом пятого элемента И, второй вход которого подключен к выходу третьего инвертора, а третий вход является входом строчного гасящего импульса блока, выход пятого элемента И соединен с установочным входом второго триггера, первый выход которого подключен к входу сброса первого триггера, установочный вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с входом второго инвертора и является первым тактирующим входом блока, а второй вход подключен к выходу первого инвертора, вход которого и вход сброса второго

1578740 триггера являются соответственно входами сигнала ввода данных и строчного синхроимпульса блока, второй информационный вход третьего триггера является информационным входом блока, второй выход второro триггера, выходы шестого злем6нта И, шестого элемента ИЛИ, элемента И-НЕ яв-ляются соответственно первым, вторым, третьим и четвертым выходами блока.

1578740

82

И

И

И

73

1578740

Составитель В,Шувалов

Техред М,Моргентал Корректор С.Шекмар

Редактор М.Циткина

Заказ 1919 Тираж 388 Подписное

ВКИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r, Ужгород, ул.Гагарина, 101