Цифровой синтезатор частот

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике. Цель изобретения - упрощение цифрового синтезатора частот. Цифровой синтезатор частот содержит первый регистр 1 памяти, генератор 2 импульсов, накапливающий сумматор (НС) 3, комбинационный сумматор 4, ключ 5, счетный триггер 6, блок 7 вычитания кодов, второй регистр 8 памяти, третий регистр 9 памяти, цифроаналоговый преобразователь (ЦАП) 10, фильтр 11 нижних частот. В исходном состоянии в первый, второй и третий регистры 1,8 и 9 записаны соответственно код числа N, код числа α и код суммы предыдущих чисел N + Α, а в НС 3 записано любое число, например α. Последовательность кодов на выходе комбинационного сумматора 4 опережает численное значение кодов НС 3 на величину α. Импульс переполнения НС 3 открывает ключ 5 и импульс с выхода генератора 2 изменяет состояние счетного триггера 6 на противоположное. По мере поступления синхроимпульсов выходные коды НС 3 и комбинационного сумматора 4 линейно увеличиваются. В блоке вычитания 7 обеспечивается формирования треугольной аппроксимирующей функции. В ЦАП 10 осуществляется преобразование кодов аппроксимирующей функции в аналоговую величину. 1 ил.

99 А1

C0IO3 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (111 (У1)5 Н 03 В 19/00

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 ..

) 1 (21) 4459093/24-09 (22) 12.07.88 (46) 15.07.90. Бюл. У 26 (72) Н.П, Кандырин, Ю.И. Романов и С.A. Соколов (53) 621.373.42(088.8) (56) Авторское свидетельство СССР

К 813679, кл. Н 03 В 19/00, 1979.

Авторское свидетельство СССР

9 1203708, кл. Н 03 И 5/00, 1984. (54) ЦИФРОВО11 СИНТЕЗАТОР ЧАСТОТ (57) Изобретение относится к радиотехнике. Цель изобретения — упрощение цифрового. синтезатора частот. Цифровой синтезатор частот содержит первый ре.-. гистр 1 памяти, генератор 2 импульсов, накапливающий сумматор (НС) 3, комбинационный сумматор 4, ключ 5, счетный триггер 6, блок 7 вычитания кодов,второй регистр 8 памяти, третий регистр

9 памяти, цифроаналоговый преобразова2 тель (UAII) 10 фильтр 11, нижних частот.

В исходном состоянии в первьн, второй и третий регистры 1,8 и 9 записаны соответственно код числа и, код числа еС и код суммы предыдущих чисел и+ Ы., а в

НС 3 записано любое число, например о4

Последовательность кодов на выходе комбинационного сумматора 4 опережает численное значение кодов НС 3 на величину, . Импульс переполнения НС 3 открывает ключ 5 и импульс с выхода генератора 2 изменяет состояние счетного триггера 6 на противоположное. По мере поступления синхроимпульсов выходные коды НС 3 и комбинационного сумматора 4 линейно увеличиваются. В блоке вычитания 7 обеспечивается формирование треугольной аппроксимирующей функ- рр ции. В ЦАП 10 осуществляется преобразование кодов аппроксииируюцей фуш;ции в аналогввую величину. 1 ил.

1578799

Изобретение относится к радиотехнике и может быть использовано в радиоприемниках и радиопередающих устройствах.

Цель изобретения . — упрощение цифро«3 ного синтезатора частот„

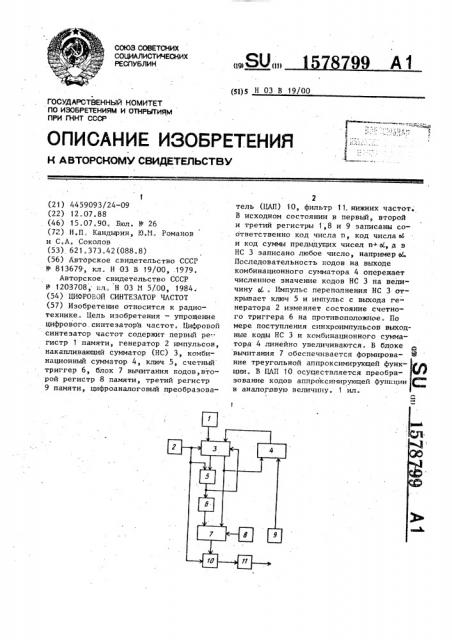

На чертеже представлена .структурная электрическая схема цифрового синтезатора частот. 0

Цифровой синтезатор частот содержит первый регистр 1 памяти, генератор 2 импульсов, накапливаюций сумматор (НС) 3, комбинационный сумматор (КС) 4,ключ

5, счетный триггер 6, блок 7 вычитания кодов, второй регистр 8 памяти, третий регистр 9 памяти, цифроаналоговый преобразователь (ЦАП) 10, фильтр

11 нижних частот.

Цифровой синтезатор частот работает20 следующим образом.

В исходном состоянии в первый регистр 1 записан код числа и, во второй регистр 8 — код числа ), н третий регистр 9 — код суммы предыдущих чисел и+()(,, а в НС 3 записано любое число, например <4 . При поступлении импульсов с частотой следования fTс выхода генератора 2 в НС 3 формируется последовательность кодов К„ г)пг

= о(,+ nr, где r = 1,2... — номер такта работы. В КС 4 осуцествляется суммирование выходных кодов K>(r) НС 3 с кодом и + О/, третьего регистра 9.

Таким образом, последовательность кодов на выходе КС 4

1, К (Г) = К )(г(Г- 1 ) + (П+(11/ ) =К „ (Г) + п(ь опережает численное значение кодов

НС 3 на величину о(, Изменение инфор- 40 мации на выходе НС 3 осуществляется по переднему фронту импульсов с выхода генератора 2. Число двоичных разрядов в НС 3 и КС 4 одинаково, поэтому переполнение содержимого КС 4 нас- /15 тупает раньше.. ь

Содержимое НС 3 линейно увеличивается до момента переполнения, когда прибавление очередного числа и изме= няет суммарный код К н так, что он становится равным или больше числа

M = 2, где m — число двоичных разlYl рядов НС 3.

При переполнении НС 3 на его выходе переполнения формируется сигнал по заднему фронту синхроимпульса. Импульс переполнения открывает ключ 5 и очередной синхроимпульс с выхода генератора 2 изменяет состояние счетного триггера 6 на противоположное, а во внутренний регистр НС 3 записывается код КС 4, который равен сумме

ЬК„С,(г ) + oL, т.е. содержимое КС 4 на () опережает содержимое КС 3. После записи в НС 3 выходного кода КС 4 на выходе переполнения прекращается сигнал переполнения и ключ 5 закрывается.

В момент переполнения в НС 3 записывается код

1 -нс(") = дКНС(г ) + а) (2)

1 где 6К)(с (г ) — остаток после переполнения в r такте работы.

Это эквивалентно уменьшению емкости

НС 3 на величину

В момент следу)я его синхроимпульса к содержимому НС 3 добавляется число и и его выходной код становится равным ((К (r +1) — К (r )+и-д1, (r )+()(!+n (3) а выходной код КС 4 опережает его на величину р,и в соответствии с (1) равен

К (r +.1) — K„(r +1)+()(, . (4)

По мере пос гупления синхронп-. зируюцих импульсов выходные коды НС 3 и КС 4 линейно увеличиваются, а в моменты переполнения в НС 3 записывается код остатка, смеценный на величину ()(, и также счетный триггер 6 изменяет свое состояние на противоположное.Т,е, в НС 3 происходит линейное суммирование кодов и по модулю (М-()(), а окончательное выражение для последовательности кодов

Ке (г)= и +пг-(11- ь1) епг (пг/(11-g)/, (5)

Форми1)пвание треугольной аппроксимирующей функции осуществляется в блоке 7 вычитания, который содержит (ш+1) двоичных разрядов.При этом на старший (ш+1) разряд подан сигнал лог. "1",что эквивалентно подаче .на второй вход блока

7 вычитания двоичного кода числа (М+()4).

Управление режимом работы блока 7 вычитания осуществляется с выхода счетного триггера 6. При низком уровне управляющего сигнала в блоке 7 вычитания осупествляется простая передача кодов с первого выхода (код К)((г)) на выход.

При высоком уровне управляюцего сигнала осуцествляется операция вычитания из двоичного кода на втором входе (М+в ) текуцего значения кода на первом т" и 4 - и .2 57-м) 272" М ) (6) Формула изобретения

Составитель 10. Ковалев

Техред:М.Моргентал Корректор М. Пожо

Редактор А. Долинич

Заказ 1922

Тираж 655

Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035,. Москва, R-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r.Óæãoðoä, ул. Гагарина,101

5 15787 ,входе К „<(r),, Указанная операция эквивалентна операции инверсии кода IIQ Mo дулю (M-к). В результате на выходе блока вычитания формируется последовательность кодов треугольной аппрокси5 мирующей функции. В ЦАП 10 осуществляется преобразование этих кодов в аналоговую величину, а фильтр 11 выделяет первую гармонику выходного сигна- 10 ла, частота которого определяется выражением:

При этом цифровой синтезатор частот обеспечивает высокое быстродействие и малый шаг перестройки по частоте и обладает более простой конструкцией.

Цифровой синтезатор частот, содержащий последовательно соединенные ге;нератор импульсов, накапливающий сумматор и комбинационный сумматор, пер вый регистр памяти, выход которого соединен с первым кодовым входом на99 6 капливающего сумматора, последователь° Ф но соединенные второй регистр памяти и блок вычитания кодов, последовательно соединенные цифроаналоговый преобразователь и фильтр нижних частот, а также третий регистр памяти., о т л ич а ю шийся тем, что, с целью повышения быстродействия при одновременном упрощении цифрового синтезатора частот, между выходом переноса накапливающего сумматора и первым входом блока вычитания кодов введены последовательно соединенные ключ и счетный триггер, второй вход блока вычитания кодов подключен к кодовому выходу накапливающего сумматора, второй кодовый вход и импульсный вход которого подключены соответственно к .выходу комбинационного сумматора и к .выходу ключа, второй вход которого объединен с первым входом цифроаналогового преобразователя и соединен с выходом генератора импульсов, выход третьего регистра памяти подключен к второму входу комбинационного сумматора, а выход блока вычитания кодов соединен с вторым входом цифроаналогового преобразователя.