М-разрядный комбинационный сумматор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике , и может быть использовано в цифровых БИС и характеризуются высоким быстродействием и низкими затратами. Сумматор состоит из узлов суммирования и узла переноса, содержащего элемент И и элемент ИЛИ, выход которого соединен с выходом переноса сумматора, причем все узлы суммирования содержат два элемента ИСКЛЮЧАЮЩИЕ ИЛИ и элемент И, а каждый -й узел суммирования содержит три элемента И и два элемента 1или. 1 ил.

СОЮЗ COBETCHHX

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

Р1)5 G 06 F 7/50

L (ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BT0PCH0MV СВИДЕТЕЛЬСТВУ

16у

f81

17

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4606634/24-24 (22) 17.11.88 (46) 23.07.90. Бюл. Ф 27 (72) С.В.Ильин, А.В.Юсупов и Л.Н.Кравченко (53) 681.325 (088.8) (56) Европейский патент Р 214836, кл. G 06 F 7/50, 1987.

Патент США N 4623982, кл. G 06 F 7/50, 1986. (54) М-РАЗРЯДНЫЙ КОМБИНАЦИОННЬП1 СУММАТОР (57), Изобретение относится к вычислительнои технике, может быть использовано в цифровых БИС и характеризуется высоким быстродействием и низ-.

„„Я0„„1580348 A 1

2 кими затратами. М-разрядный комбинационный сумматор имеет входы )6 и 17 слагаемых, выход ll суммы, вход 12 переноса, выход 15 переноса. В каждом разряде суммирования на элементах,ИСКЛЮЧАКНЦЕЕ ИЛИ 5, и И 3. формируются значения полусуммы разрядов слагаемых Р = А . О В и сигнала ф Ъ l генерации переноса G = А", Н< соответственно. На ;, ИЛИ

9 по последовательному принципу ! формируются условные межразрядные переносы, исходя из условия равенства нулю входного переноса. Выработка истинного межразрядного переноса в х-и разряд суммирования осуществляется путем селективного пропуска значе- Е

1580348

Яй =А;ЭВ; ЭС; ний условного переноса С °, и входного переноса С „на элементах И 7., 1

ИЛИ 10 в соответствии с выражени1 ем С,=С;» + C>N Р Р,.... Р»,.

Сигналы управления селективным пропуском формируются на элеИзобретение относится к вычислительной технике и микроэлектронике и может быть использовано в цифровых

БИС высокого быстродействия.

Целью изобретения является упро- 15 щение М-разрядного комбинационного сумматора.

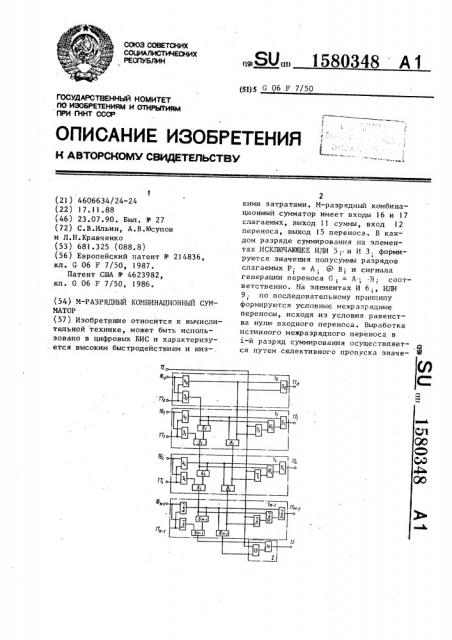

На чертеже представлена функциональная схема М-разрядного комбинационного сумматора, 20

Сумматор состоит из узлов 1 )

1,,...,1 „„, суммирования и узла 2 переноса, с нулевого по (И-1)-й узлы суммирования содержат элементы

И 3, 3,,...,3 „ „и элементы ИСКЛЮЧА10- 25

liEE ИЛИ 4., 4,)...)4р,и 5, 5„)..., ...,з ... с первого по (и-11-й узлы суммирования содержат элементы И 6

6,)" )6 м о 7,)7.„) ° ° "7,, и 8, 8 ...,,8 м „элементы ИЛИ 9 ) 30. ) ° ° ° ) м- и 101) 102) 1 м-() выходы 11 ) 11 „,...,11 „, с нулевого по (М-1)-й разрядов суммы сумматора, вход 12 переноса сумматора, узел 2 переноса содержит элемент 35

° И 13 и элемент ИЛИ 14, выход 15 пере" носа сумматора, входы 16 „, 16,, нулевого по (М-1) рязрядов первого и второго слагаемых сумматора сост- 40 ветственно.

Сумматор работает следующим образом.

Разряды слагаемых поступают на входы 16 и 17, сигнал входного переноса С „ — на вход 12. В каждом разряде суммирования на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 4, и И 3, формируются значения полусумм разрядов слагаемых

Р, = А; 9 В; и сигнала генерации переноса 0; = А;. В соответственно.

На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ

5 формируется i-й разряд суммы Я (1

s соответствии с выражением 55 о

Я =А ЭВ,З(С;,+ С „ .P""Р

° ° е Р 1 1 ) ) ментах И 8 (k = 1,..., i-q ). Разряд суммы Я; вырабатывается на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 5.. Я;

= А . 9 Б Ы С;,. Выходной перенос формируется на элементах И 13 и

ИЛИ 14. 1 ил.

О где С;, — условный перенос из (i-1)го разряда суммирования, вычисляемый из условия равенства нулю входного переноса.

Условные межразрядные переносы вычисляются последовательно на элементах И 6., ИЛИ 9,. (i = 1,...,М-1) исходя из условия равенства нулю входного переноса. Условный перенос Из нулевого разряда суммирования совпадает со значением сигнала генерации переноса нулевого разряда суммирования °

Значение истинного переноса в

i-и разряд суммирования формируется на элементах И 7;, ИЛИ 10. путем

i селективного пропуска значений усО ловного переноса С . и входного

1-1 переноса С т), . в соответствии с выражением

Элемент И 7. обеспечивает блокирование входного переноса. Управление элементом И 7 ; осуществляется сигналом Р - Р,...Р,, Формирование сигнала управления производится последовательно на элементах И 8+ (k =

= 1,..., -1).

Для пояснения принципа селективного формирования истинного переноса в 1-й разряд суммирования рассматривают два случая.

I. Хотя бы одно значение P .1,= О (Ы =-О,...,i-I), ) т.е. хотя бы в одном из разрядов, предшествующих

i-му, разряды слагаемых имеют одинаковые значения (А 1, О, В у, = О или

А — 1, В вв 1). При этом входной перенос не оказывает влияния на формирование переноса в i-й разряд сум-. мирования. Элемент И71 имеет на выходе уровень логического нуля. Значение условного переноса С проо

i-!, ходит через элемент ИЛИ 10; на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5; и -ый разряд суммы равен

1580348

II. Все значения P P °...Р.

11 И .равны 1, т.е. во всех разрядах, предшествующих i-му, разряды слагаемых имеют разные значения (А 1. = О, В,= I или А1,=1, В =О (k

= О,..., i-I )). При этом в связи с тем, что условием формирования условных переносов является равенство нуо лю входного переноса, все С 1, = О.

Входной перенос сумматора проходит через элементы И /;, ИЛИ 10; на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5,, и

i-и разряд суммы равен

S = А; (ЭВ; О - C ù.

Нулевой разряд суммы имеет значение

9Bo ®C .

Выходной перенос сумматора формируется на элементах И 13, ИЛИ 14 в соответствии с выражением о

С „=С,+С,„.Р Р,...Р и выдается на выход 15.

Формула и з о б р е т е н и я

М-разрядный комбинационный сумматор, состоящий из узлов суммирования и узла переноса, содержащего элемент И и элемент ИЛИ, выход которого соединен с выходом переноса сумматора, причем все узлы суммирования содержат два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент И, а каждый i-й (где

1,2,..., M-I ) узел суммирования содержит три элемента И и два элемента ИЛИ, причем входы i-ro разряда первого слагаемого сумматора соединены с первыми входами первых элементов И и ИСКЛЮЧАЮЩЕЕ ИЛИ i-го узла суммирования, вторые входы которых соединены с входами i-ro разряда второго слагаемого сумматора, вход нулевого разряда первого слагаемого сумматора соединен с первыми входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента И нулевого узла суммирования, вторые входы которых соединены с входом нулевого разряда второго слагаемого сумматора, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ каждого узла суммирования соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ этого узла суммирования, выход которого является выходом соответствующего разряда суммы сумматора, выход первого элемента И i-ro узла суммирования соединен с первым входом первого элемента ИЛИ i-ro узла суммирования, второй вход которого соединен с выходом второго элемента

И i-го узла суммирования, вход переноса сумматора соединен с первыми входами третьих элементов И i-x узлов суммирования и первым входом элемента И узла переноса, выход которого соединен с первым входом элемента ИЛИ узла переноса, второй вход которого соединен с выходом первого элемента ИЛИ (M-1)-го узла суммирования, выход первого элемента ИЛИ i-ro узла суммирования соединен с первыми входами вторых элементов И и ИЛИ (i+I )-го узла суммирования, выход третьего элемента И i-го узла суммирования соединен с вторым входом второго элемента ИЛИ i-го узла суммирования, выход которого соединен с вторым входом второго элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ i-ro узла суммирования, отличающийся тем, что, с целью упрощения сумматора, выход первого элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ i-ro узла суммирования соединен с первым входом четвертого и вторым входом второго элементов И i-го узла суммирования, вход переноса сумматора соединен с вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ нулевого узла суммирования, выход элемента И нулевого узла суммирования соединен с вторыми входами вторых элементов И и ИЛИ первого узла суммирования, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ нулевого узла суммирования соединен с вторыми входами третьего и четвертого элементов И первого узла суммирования, выходы четвертых элементов И с первого по (И-2)-й уз5

1О

45 лов суммирования соединены с вторыми входами третьих и четвертых элементов И с второго по (И-I )-й узлов суммирования соответственно, выход четвертого элемента И (M-1)-го узла суммирования соединен с вторым входом элемента И узла переноса.