М-разрядный комбинационный сумматор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, может быть использовано в цифровых БИС и характеризуется низкими затратами и повышением быстродействием. Сумматор состоит из М узлов суммирования и узла переноса, содержащего элемент И и элемент ИЛИ, выход которого соединен с выходов переноса сумматора, причем все узлы суммирования содержат два элемента ИСКЛЮЧАЮЩИЕ ИЛИ и элемент И, а -й узел суммирования дополнительно содержат три элемента И и элемент 1или. С целью повышения быстродействия и упрощение сумматора, в -й узел суммирования введен третий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. 1 ил.

СОЮЗ СОЕЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 G 06 F 7 50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

17

11, 12о

11;

t2i

ГОСУДАРСТВЕННЫЙ HOMHTET

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4606641/24-24 (22) 17.11.88 .(46) 23.07.90 ° Бюл. !! 27 (72) С.В.Ильин, А.В.Юсупов

I и Л.Н.Кравченко (53) 681.325 (088.8) (56) Европейский патент У 214836, кл.G 06 F 7/50, 1987.

Патент США В 4623982, кл. G 06 F 7/50, 1986. (54). М-РАЗРЯДНЫЙ КОМБИНАЦИОННЫЙ СУММАТОР

„„Я0„„1580349 А 1

2 (57) Изобретение относится к вычислительной технике, может быть использовано в цифровых БИС и характеризуется низкими затратами и повышенным быстродействием. М-разрядный комбинационный сумматор имеет. входы I! u !

2 слагаемых, выход 16 суммы, вход

17 переноса и выход !S переноса. В каждом разряде суммирования на элементах ИСКЛЮЧАЮ!ЦЕЕ ИЛИ 4; и И 3,. формируются значения полусуммы разрядов слагаемых Р; = АЙ В; и сигналя генерации переноса G; = А;.В; соответст1580349

4 венно. На элементах И 6 и ИЛИ 9 ° по I f последовательному принципу формируются условные межразрядные переносы С., о

1 исходя из условия равенства нулю входного переноса. На элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 9. формируется i-й раз1 о ряд условной суммы S l . Формирование истинного разряда суммы осуществляется на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 5; lp путем селективного инвертирования

i-ro разряда условной суммы S; в сом

Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано в цифровых

БИС высокого быстр действия.

Целью изобретения является повыше- gp ние быстродействия и упрощение сумо матора.

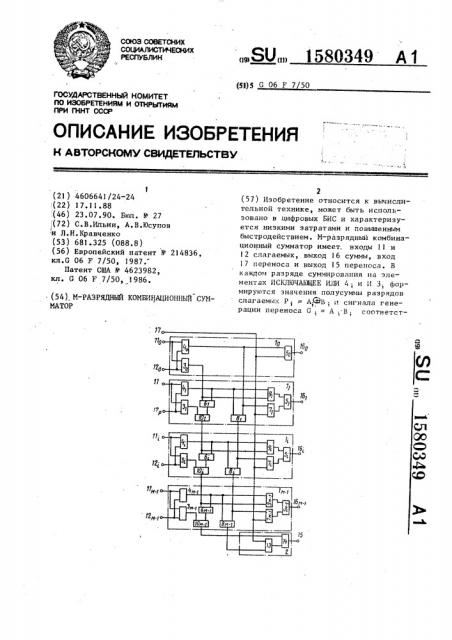

На чертеже представлена функциональная схема М-разрядного комбинаци онног о сумма тор а. 25

Сумматор содержит М узлов 1о, I 1,„, суммирования и узел 2 ф ° ° ° ф переноса. С нулевого по (И-1 )-й узлы суммирования содержат элементы

И Зо,З „ . ° .,3 м,, пеРвые элементы 30

ИСКЛЮЧАЮЩЕЕ ИЛИ 4„,4 „...,4 „,,, вторые элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 5»

5,,...,5 „„,, с первого по (М-1)-й узлы суммирования содержат вторые, 6 >6, ° ° ° j6мтретьи 7, 7q> ° ° ° 7м и четвертые 8,, 8,...,8, элементы И, третьи элементы ИСКЛЮЧАЮЩЕЕ

ИЛИ 9,,9,...,9<» элементы ИЛИ ° ° °,11 < 1 Разрядов с нуЛевого ao - 40 (И-1)-й первого слагаемого сумматора, входы 12„, 12 „...,,12„„, разря-, дов с нулевого по (N-1)-и второго слагаемого.

Узел переноса содержит элемент 45

И 13 и элемент ИЛИ 14, выход- 15 переноса сумматора, выходы 16, 16,,..., 16 „„, суммы сумматора и вход

17 переноса сумматора.

Сумматор работает следующим образом.

Разряды слагаемых поступают на входы 11 и 12, сигнал входного переноса С вЂ” на вход 17. В каждом раз и ряде суммирования на элементах ИСКМ

ЛЮЧАЮЩЕЕ ИЛИ 4; и И 3; формируются значения полусуммы разрядов слагаемых Р; = А; 9 В 1 и сигнала генерации переноса G = А, В; соответстответствии с выражением S . о

= Я ®(С „ Ро.Р, ...P ). Управление селективным инвертированием осуществляется сигналом с выхода элемента И 7; на первый вход которого подается входной перенос С „, а на второй вход — сигнал Р Р„... P.,ôîð1 -1 мируемый последовательно на элементах И 8 о, 8 1,... 8; „, выходной перенос сумматора формируется на элементах И 13, ИЛИ 14. 1 ил. венно. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5; формируется i-й разряд суммы S; в соответствии с выражением

S. = S. 8 (С.„-P .P,...Р;, ),. где S — i-й разряд условной суммы, полученный исходя из условия равенства нулю входного переноса и формируемый на выходе элемента ИСКЛОЧАЮЩЕЕ

ИЛИ 9; в соответствии с выражением

S, = А; 9 ВС;-1, о где С,, — условный перенос из (i-l)го разряда суммирования.

Условные межразрядные переносы формируются последовательно на элементах И 6, ИЛИ 10 исходя из условия равенства нулю входного переноса..

Значение условного переноса из нулевого разряда суммирования совпадает со значением генерации переноса нулевого разряда суммирования.

Значение истинного разряда суммы

Б формируется путем селективного инвертирования значения условного разряда суммы S. на элементе ИСКЛЮо

ЧАКЩЕЕ ИЛИ 5 . Управление селективI ным инвертированием осуществляется сигналом с выхода элемента И 7., на

1 вход которого подается входной перенос сумматора. Элемент И 7. Управляется сигналом Р .P,...Р;,, который формируется последовательно на элементах И 8 (k = 1,..., i-l ).

Для пояснения процесса формирования истинного разряда суммы рассматривают два случая:

Х. Хотя бы одно значение Р1

О (k = О,..., i-l), т.е. хотя бы

s одном разряде, предшествующем i-му, разряды слагаемых имеют одинаковые значения (A> = О, В = О или А = 1, В 1, 1). При этом входной перенос не оказывает влияния на формирование

1580349 о = Aî ®Во® С .

Выходной перенос сумматора формируется на элементах И 13 и ИЛИ 14 в соответствии с выражением о

Соот С м-1 С?и Ро Р Ры- и выдается на выход 15.

Формула изобретения

М-разрядный комбинационный сумматор, состоящий из М узлов суммирования и узла переноса, содержащего элемент И и элемент ИЛИ, выход кото— рого соединен с выходом переноса 4О сумматора, причем все узлы суммирования содержат два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент И, à i-й узел суммирования (где i = 1,2,...,М-1) дополнительно содержат три элемента И 45 и элемент ИЛИ, причем вход i-го разряда первого слагаемого сумматора соединен с первыми входами первых элементов И и ИСКЛЮЧАЮЩЕЕ ИЛИ i-ro узла суммирования, вторые входы кото- 5р рых соединены с входом i-го разряда второго слагаемого сумматора, вход нулевого разряда первого слагаемого сумматора соединен с первыми входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента И нулевого узла суммирования, вторые входы которых соединены с входом нулевого разряда второго слагаемого сумматора, выход первого

i-ro разряда суммь.. Элемент И 7i имеет на выходе уровень логического нуо ля. Значение S проходит без изменения через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ на выход 16; .

II. Все значения P о P,...Ð;, равны логической "1" т.е. во всех раз- . рядах, предшествующих i-му, разряды слагаемых имеют разные значения (A g =

О, B =1илиА =1, Bg=O) (k

= О,..., i-1 )). При этом входной перенос используется в формировании

i-ro разряда истиной суммы. Входной перенос сумматора проходит через эле-15 мент И 7; .. Если С ц = О, т.е. соото ветствует условию формирования S то Н проходит без изменения на вы I о ход 16; . Если С, = 1, значение S; инвертируется на элементе ИСКЛЮЧАЮ- 20

ЩЕЕ ИЛИ 5; и на выход 16у поступает

-o значение S ..

Нулевой разряд истиной суммы фор-. мируется непосредственно под управлением входного переноса 25 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ нулевого узла суммирования соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ нулевого узла суммирования, выход которого является выходом нулевого разряда суммы сумматора, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ

i-го узла суммирования соединен с выходом i-го разряда суммы сумматора, выход первого элемента И i-ro узла суммирования соединен с первым входом первого элемента ИЛИ 1-го узла суммирования, второй вход которого соединен с выходом второго элемента И i-го узла суммирования, вход переноса сумматора соединен с первыми входами третьих элементов И i õ узлов суммирования и первым входом элементов И узла переноса, выход которого соединен с первым входом элемента ИЛИ узла переноса, второй вход которого соединен с выходом первого элемента ИЛИ (М-I)-го узла сумьырования, выход первого элемента ИЛИ i-го узла суммирования соединен с первым входом второго элемента И. (i+1)-ro узла суммирования, о т л и ч а ю— шийся тем, что, с целью ",îâûøåния быстродействия и упрощения сумматора, в i-й узел суммироваНия введен третий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ

i-го узла суммирования, второй вход которого соединен с выходом третьего элемента И i-ro узла суммирования, второй вход которого соедиие с первым входом четвертого элемагга

И i-ro узла суммирования и выходом четвертого элемента И (i-1)-го узла суммирования, первый вход четвертого элемента И первого узла суммирования соединен с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ нулевого узла суммирования, выход элемента И нулевого узла суммирования соединен с первым входом второго элемента И первого узла суммирования, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ i-го узла суммирования соединен с первыми входами третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ i-го узла суммирования и с вторыми входами вторых и четвертых элементов И i-го узла суммирования, вход переноса сумматора соединен с вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ нулевого узла суммирования, выход четвертого элемента И

1580349

Составитель Н.Маркелова

Техред Л.Сердюкова

Корректор С.Черни

Редактор Н.Рогулич

Ю

Заказ 2012 Тираж 565 Подписное

3НКЩИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.Ужгород, ул. Гагарина,101 (М-1)-го узла суммирования соединен с вторым входом элемента И узла переноса, первый вход второго элемента

И i-ro узла суммирования соединен с вторым входом третьего элемента ИСКЛЮЧАКЦЕЕ ИЛИ i-го узла суммирования.