Устройство для умножения

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к устройствам для умножения , и может быть использовано при построении арифметических устройств электронных вычислительных машин. Устройство для умножения содержит регистры первого и второго сомножителей, два триггера, элемент И, группу элементов И-ИЛИ, первую и вторую группы элементов И, группу сумматоров, группу распределительных ячеек, управляющий регистр, элемент ИЛИ. С целью сокращения оборудования в устройство введена третья группа элементов И. Каждая распределительная ячейка группы содержит два фиксатора суммы, каждый из которых состоит их основного и дополнительного триггеров, два фиксатора переноса, каждый из которых состоит из основного и дополнительного триггера и два элемента И-ИЛИ. 2 ил.

СОЮЭ COBETCHHX

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

„,80„„1580352 А 1 (5l)5 G 06 F 7 52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМЪ СВИДЕТЕЛЬСТВУ

Сд

1 ОСУААРСТВЕННЫЙ КОЫИТЕТ

flO ИЗОБРЕТЕНИЯМ И (ЛНРЫТИЯМ

ПРИ ГКНТ СССР

1 (21 ) 4621609/24-24 (22) 19.. 12. 88 (46) 23. 07. 90. Бюл. Р 27 (71) Институт кибернетики им.В.M. Ãëóøкова (72) В.А Вышинский, Б.N.Òèõîíîí и Н.Б,Фесенко (53) 681.325 (088.8) (56) Авторское свидетельство СССР

У 1399729, кл. G 06 F 7/52, 1986.

Авторское свидетельство СССР

N 1425659, кл. G 06 F 7/52, 1987..

2 (54} YCTPOACTBO I1JII1 YNHOREHHH (57) Изобретение относится к вычислительной технике, в частности к устройствам для умножения, и может быть использовано при построении арифметических устройств электронных вычислительных машин. Цель изобретения— сокращение количества оборудования устройства за счет введения третьей группы элементов И, что позволило полностью совместить формирование и

1580352

3S суммирование двухрядного кода результата группой сумматоров и распределительных ячеек, а также уменьшить информационные пересылки между суммато5 рами и распределительными ячейками.

Устройство содержит сдвиговые регистры первого 6 и второго 7 сомножитеИзобретение относится к вычислительной технике, в частности" к устройствам для умножения, и может быть использовано при построении арифметических устройств электронных вычислительных машин.

Целью изобретения является сокращение количества оборудования устрой" ства. 20

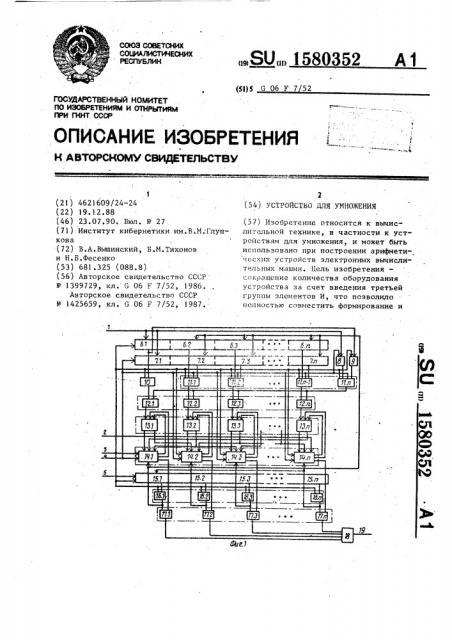

На фиг.1 приведена функциональная

О схема устройства для умножения; на фиг. 2 " схема распределительной ячейки, Устроиство для умножения (фиг.1) 25 содержит информационный вход 1,вход

2 нулевого потенциала, первый 3 и второй 4 тактовые входы, установочный вход 5, регистры первого 6 и второго 7 сомножителей, два триггера

8 и 9, элемент И 10, группу элементов И-ИЛИ 11, первую группу элементов И 12, группу сумматоров 13,группу распределительных ячеек 1 4,управляющий регистр 15,вторую и третью группы элементов И 16 и 17, элемент

ЙЛИ 18 и выход 19 результата устройства.

Распределительная ячейка 1 4 группы (фиг.2) содержит первый 20, второй 21 и третий 22 информационные входы, первый 23 и второй 24 синхро-. входы, первый 25 и второй 26 фиксаторы суммы, первый 27 и второй 28 фиксатоРы переноса, каждый из кото- 45 рых содержит основной и дополнительный триггеры, два элемента И-ИЛИ 29 и 30, управляющий вход 31 и информационные выходы 32 — 34.

В устройстве для умножения разряды 50 регистра 6 первого сомножителя, регистра 7 второго сомножителя, управляющего регистра 15 построены на двухтактиых триггерах (каждый двухтактный триггер содержит основной и дополнительный однотактные триггеры).

Первый 8 и второй 9 триггеры устройства построены на однотактных триггерах. Фиксаторы 25 и 26 суммы и фиксалей, группу сумматоров 13, первый 8 и второй 9 триггеры, группу элементов И-ИЛИ 11, элемент И 1 О, группу распределительных янеек 14, управляющий регистр 15 три группы элементов

И 12,16,17 и элемент ИЛИ 18. 1 з.п. ф-лы. 2 ил. торы 27 и 28 переноса распределительных ячеек 14 группы, кроме первого фиксатора 27 переноса второй распре; делительной ячейки 14.2 группы, содержат оцнотактные основные триггеры

25.1, 26.1, 27.1, 28.1 и дополнительные однотактные триггеры 25.2, 26.2, 27.2„ 28.2. Первый фиксатор 27 переноса второй распределительной ячейки

14.2 группы содержит только однотактный основной триггер 27,1 и не содержит дополнительного триггера 27.2.

Устройство для умножения работает в конвейерном режиме. В процессе работы оно перемножает пары и-разрядных сомножителей А„и В,, А и В, А> и

В,...,А,„и Bщ, где N — число пар сомножителеи. Конвейер состоит из двух каскадов. Первый каскад конвейера включает формирование двухрядного кода частичных произведений, а второй каскад конвейера — суммирование двухрядного кода и получение окончательного результата. Для очередной пары сомножителей А, и В . первый каскад конвейера выполняется одновременно со вторым каскадом конвейера предыдущей пары сомножителей А . и

1-!

В;, В течение первых (и+1) тактов устройство формирует двухрядный код первой пары сомножителей (первый каскад конвейера для сомножителей А> и В,).

Полученный двухрядный код первого произведения преобразуется в окончательный результат в течение следующих II тактов работы устройства. (второй каскад конвейера для сомножителей А, и В,) одновременно с формированием устройством двухрядного ко. да следующей пары сомножителей (первый каскад конвейера для сомножителей А и В ). Окончательный результат умножения очередной пары сомножителей представляется в виде и-разрядного кода. Округление результата происходит за счет того, что п младших разрядов двухрядного кода не участвуют

1580352

15

35

45

55 в формировании окончательного результата.

Управление подключением распределительных ячеек 14 группы и сумматоров 13 группы к формированию двухряд5 ного кода или к суммированию двухрядного кода для получения окончательного результата осуществляет иразрядный сдвиговый управляющий регистр 15. В начальное состояние

100...0 управляющий регистр 15 устанавливается с приходом синхросигнала . первого такта под действием сигнала установки, который поступает через вход 5 установки на вход установки в единицу первого разряда и на входы установки в нуль остальных (п-1) разрядов этого регистра.

Сигналы с выходов разрядов управляющего регистра 15 являются разрешающими для элементов И 16 второй группы, Единичный сигнал с выхода i-ro элемента И 16.i второй группы подключает с помощью i-ro элемента И 17 третьей группы третий информационный выход 34 i-й распределительной ячейки 14.i группы к входу и-входового элемента ИЛИ 18, а через него на выход 19 устройства.. Единичный сигнал с выхода i o элемента И 16.i второй группы поступает через управляющий вход 31 в i-ю распределительную ячейку 14.i группы, обнуляет в этой распределительной ячейке дополнительные триггеры фиксаторов 25.2, 26.2, 27.2, 28.2 суммы и переноса. Единичный сигнал с выхода первого элемента

И 16.1 второй группы, поступая на входы установки в нуль триггеров разрядов регистров 6 и 7 -сомножителей, начиная с дополнительных триггеров вторых разрядов регистров 6 и 7 сомножителей, устанавливает перечисленные триггеры разрядов регистров 6 и

7 сомножителей в нуль, освобождая место для поступления очередной пары сомножителей. С выхода п-го элемента И 16.п второй группы единичный управляющий сигнал возвращается в первый разряд управляющего регистра 15.

Рассмотрим первый каскад конвейера — формирование двухрядного кода произведения пары сомножителей.

На информационный вход 1 устройстI ва последовательно подаются первый о сомножитель A. = а,, а,,..., а„), 1 начиная со старших разрядов, и второй сомножитель В = Ь,, b2>..., b„), начиная с младших разрядов. Первый сомножитель А подается во время дей= ствия синхросигналов, а второй

1 У сомножитель  — во время действия синхросигналов 1, . В регистре 6 первого сомножителя и в регистре 7 второго сомножителя одновременно с приемом информации производится сдвиг информации на один разряд в сторону старших разрядов.

Управляющий сигнал с выхода n-ro элемента И-ИЛИ 11 .п поступает на входы элементов И 12 первой группы,на вторые входы которых через элемент

И 10. и первые элементы И-ИЛИ 11.1

ll.(n-1) подаются сигналы с выходов соответствующих разрядов регистра 6 первого сомножителя и регистра 7 второго сомножителя в соответствующий момент действия синхросигналов и

1 и

Первый 8 и второй 9 триггеры и элемент И-ИЛИ 11 формируют сигналы, управляющие формированием различных по весу. разрядов частичных произведений на элементах И 12 первой группы. Во время действия синхросигнала формируются частичные произведения весом от первого до п-ro разрядов. Сформированные частичные произведения суммируются на сумматорах

13 группы с промежуточными значениями сумм и переносов, которые .хранятся во вторых фиксаторах 26 и 28 сумм и переносов распределительных ячеек !

4. Так как младшие по весу разряды частичного произведения формирует п-й элемент И 12.п первой группы, то перенос распространяется от п-ro сумматора 13,п группы к первому сумматору 13.1 группы, Во время действия синхросигналов ь формируются частичные произведения весом от (n+1 )-го до 2n-ro разрядов. Сформированные частичные произведения суммируются на сумматорах

13 группы с промежуточными значениями сумм и переносов, которые хра«ятся в первых фиксаторах 25 и 27 сумм и переносов распределительных ячеек

14 группы. Так как средние по весу разряды частичного произведения формирует первый элемент И 12.1 первой группы, а старшие — и-й элемент И

1580352

12.п первой группы, то перенос распространяется от первого сумматора

13.1 группы к п-му сумматору 13.п группы.

При работе первого каскада конвей5 ера в качестве исходной информации для обработки выступают два сомножителя А- и В;. При работе второго

1 каскада конвеиера исходной информацией для обработки выступают два слагаемых — двухрядный код суммы частичных произведений и переноса. В то время,, когда часть сумматоров 13 групцы занята суммированием !5 формируемых частичных произведений, другая, не занятая в этом процессе оставшаяся часть сумматоров 13 группы выполняет суммирование двухрядного кода - второй каскад конвейера.

Чтобы разряды регистров 6 и 7 сомножителей не оказывали влияние на второй каскад конвейера, производится их периодическое обнуление, начиная с дополнительных триггеров вторых 25 разрядов регистров 6 и 7 сомножителей.

Обнуление разрядов при суммировании двухрядного кода производится при помощи элементов И 16 второй 30 группы, на первые входы которых поступают синхросигналы 1, а на вторые — сигналы с выходов соответствующих разрядов управляющего регистра 15. В момент поступления синхро- сигнала 1 нулевой сигнал с выхода элемента И 16 второй группы эакрыва" ет элемент И 17 третьей группы.Еди" ничный сигнал с выхода элемента

И 16 второй группы обнуляет дополни- 4р тельные триггеры фиксаторов 25.2, 26.2, 27.2, 28.2 суммы и переноса соответствующей распределительной ячейки 1 4 группы в момент перезаписи информации из основных триггеров.

Округление и младших разрядоэ выполняется их отбрасыванием, так как выходы соответствующих им вторых фиксаторов 26 сумм не подключены к выходу устройства.

Первые фиксаторы 25.1 сумм распределительных ячеек 14 группы после поступления в них старших разрядов результата, подключаются к выходу устройства для вывода результата, причем информация подается с выхода основных триггеров первых фиксаторов

25.1 сумм через третий информационный выход 34 распределительной ячейки. Элементы И 16 второй группы и управляющий регистр 15 периодически подключают третьи информационные выходы 34 соответствующих распределительных ячеек 14 группы через элементы И 1 7 третьей группы к элементу

ИЛИ 18 и выходу 19 устройства.

Устройство работает следующим образом.

В исходном состоянии триггеры и регистры устройства обнулены.С приходом синхросигнала 1 первого такта на вход 5 устройства подается сигнал установки, который устанавли" вает управляющий регистр 15 в начальное состояние, т.е. в состояние

1000...0. По синхросигналу ь пер1 вого такта в первый разряд регистра

6 записывается значение старшего разряда а, сомножителя А,, а с приходом синхросигнала 1 первого такта

Ф. в первый разряд регистра 7 и в первый триггер 8 записывается значение младшего разряда b сомножителя В

В течение первого такта на сумматорах 13 суммируется нулевая информация регистров 6 и 7 и дополнительных триггеров фиксаторов 25 — 28 суммы и переноса распределительных ячеек

14. Со следующего такта для первой пары сомножителей А и В начинает1 1 ся первый каскад конвейера.

Во время действия синхросигнала второго такта в первый разряд регистра 6 записывается значение разряда а сомножителя А, во вто1э рой разряд регистра 6 и во второй триггер 9 сдвигается значение разряда а„сомножителя А,. На выходе элемента И 12.1 формируется первое частичное произведение а„Ь . На сумматоре 13.1 оно суммируется с нулевым значением суммы частичных произведений и результат записывается во вторые фиксаторы 26.1 и 28.1 суммы и переноса распределительной ячейки

14.1 в качестве промежуточного .зна чения суммы частичных произведений.

По синхросигналу 1 второго ! такта с выхода первого разряда управ.ляющего регистра 15 через первый элемент И 16.1 второй группы проходит единичный управляющий сигнал на первый вход первого элемента И 17.1 третьей группы, управляющий вход 31 первой распределительной ячейки 14.1, и входы установки в нуль триггеров разрядов регистров 6 и 7, начиная с

1 580352

10 дополнительных триггеров вторых разрядов регистров 6 и 7. Под действием единичного управляющего сигнала с выхода основного триггера первого фиксатора 27.1 переноса первой распределительной ячейки 14.1 через третий информационный выход 34 этой распределительной ячейки, первый элемент И 17.1 третьей группы, элемент

ИЛИ 18 проходит нулевая информация на выход 19 устройства. Одновременно с этим производится обнуление дополнительных триггеров фиксаторов

25.2, 26.2, 27.2, 28.2 суммы и переноса первой распределительной ячейки 14 ° 1 и, начиная с дополнительного триггера второго разряда регистра, триггеров регистров 6 и 7, а значение единицы сдвигается во второй разряд управляющего регистра 15.

Во время действия синхросигнала второго такта в первый разряд регистра 7 и в первый триггер 8 записывается значение разряда Ь „, сомножителя В„, во второй разряд регистра 7 сдвигается значение разряда Ь„ сомножителя В .

По синхросигналу. 3 третьего

1 такта в первый разряд регистра 6 записывается значение разряда а сом3 ножителя А,, во второй разряд регистра 6 и второй триггер 9 сдвигается значение разряда а сомножителя

А,, в третий разряд регистра 6 сдвигается значение разряда а . сомно1 жителя А,. На выходе элементов И. 12.1 и 12.? первой группы формируются младшие разряды второго частичного произведения а Ь „,, а, Ь „, первой пары сомножителей А и В . Ha сумма1 1 торах 13.1 и 13.2 они суммируются с промежуточным значением суммы частичных произведений, и результат записывается во вторые фиксаторы

26.1 и 28.1 суммы и переноса распределительных ячеек !4.1 и 14.2.

Во время действия синхросигнала третьего такта с выхода второго разряда управляющего регистра 15 единичный управляющий сигнал поступает через второй элемент И 16.2 второй группы на.первый вход второго элемента И 17.2 третьей группы, Под действием этого единичного управляющего сигнала с выхода основного триггера первого фиксатора 25.1 суммы второй распределительной ячейки 14.2 на выход 19 устройства поступает ну5

55 левая информация, прошедшая через третий информационный выход 34 второй распределительной ячейки 14.2,второй элемент И 17.2 третьей группы, элемент ИЛИ 18. Одновременно с этими действиями производится обнуление дополнительных триггеров фиксаторов

25.2, 26.2, 27.2, 28.2 суммы и переноса второй распределительной ячейки 14.2, на входы установки в нуль которых единичный сигнал поступает через управляющий вход 31 распределительной ячейки 14.2. При этом значение единицы сдвигается в третий разряд управляющего регистра 15.

По синхросигналу третьего такта в младший разряд регистра 7 и в первый триггер 8 записывается значение разряда Ь „ сомножителя В ; во

1 второй разр д регистра 7 сдвигается значение разряда Ь „, сомножителя

В, а в третий разряд — значение младшего разряда Ь„сомножителя В т

На выходе элемента И 12.2 формируется старший разряд второго частичного произведения а h „. На сумматоре 13.2 оно суммируется с промежуточным значением суммы частичных произведений, и результат записывается в первые фиксаторы 25.1 и 27.1 суммы и переноса второй распределительной ячейки

i4.2.

С помощью синхросигнала,(i+I )ro такта в первый разряд регистра 6 записывается значение разряда а;, сомножителя А,, во второй разряд регистра 6 и второй триггер 9 сдвигается значение разряда а, сомножителя А,, в третий Разряд — значение разряда а;, сомножителя А „ в каждый следующий до (i+1)-ro разряда регист.Ра 6 сдвигается значение предыдущего разряда сомножителя А,, в (i+1)-й разряд регистра 6 сдвигается значение разряда а, сомножителя А,. На выходе элементов И 12.1 — 12.i первой группы формируются младшие разряды частичных произведений; а,Ь „. <,,(, ...,,а Ь „1;, . На сумматорах 13.1

13.i ow суммируются со значениями промежуточной суммы частичных произведений, и результат записывается во втоРые фиксаторы 26.2 и 28.1 суммы и переноса распределительных ячеек 14.1 — !4.i.

Во время действия синхросигнала (i+1)-ro такта с выхода i-го разряда управляющего регистра 15 единич1580352

5 !

О !

35

55 ный управляющий сигнал поступает через i-й элемент И Iб.i второй группы на первый вход i-ro элемента

И 17.i третьей группы. Под действием этого единичного управляющего сигнала с выхода основного триггера первого фиксатора 25,1 суммы i"é распределительной ячейки 14.i на выход 19 устройства поступает нулевая информация, прошедшая через третий информационный выход 34 i-и распределительной ячейки 14.i i-и элемент

И 17.i третьей группы, элемент

ИЛИ 18. Одновременно с этим действием производится обнуление дополнительных триггеров фиксаторов 25.2, 26.2, 27.2, 28.2 суммы и переноса

i-и распределительной ячейки 14 i на входы установки в нуль которых единичный сигнал поступает через управляющий вход 31 распределительной ячейки 14.i. При этом значение единицы сдвигается в (i+I)-й разряд управляющего регистра 15.

С приходом синхросигнала !1

7 и в первый триггер 8 записывается значение разряда Ь „!;„! сомножителя В, в каждый следующии до (i+1)—

ro разряда регистра 7 сдвигается значение поступивших в предыдущих тактах разрядов сомножителя В, в (i+

1.Ф

+1)-й разряд регистра 7 сдвигается значение разряда b ñoìíîæèòeëÿ В! .

На выходе элементов И 12.2-12.i первой группы формируются старшие разряды различных по весу частичных произведений a;b „.<;

25.1 и 27.1 суммы и переноса распределительных ячеек 14.2-14.1.

По синхросигналу Г1 и-го такта в первый разряд регистра 6 зайисывается значение младшего разряда а

h сомножителя А, во второй разряд

1 . . регистра 6 и второй триггер 9 сдвигается значение разряда а д, сомно" жителя А, в каждый следующий разряд

1 э сдвигается значение предыдущего разряда сомножителя А, в и-й разряд регистра 6 сдвигается значение разряда а, сомножителя А,. На выходе элементов И 12.1-12.(п-l) формируются младшие разряды различных по весу разрядов частичных произведений

12 а Ь " . а „, Ьг На су аторах 13.113.(n-I ) они суммируются со значениями промежуточной суммы частичных произведений, и результат записывается во вторые фиксаторы 26.1 и 28.1 суммы и переноса распределительных ячеек 14.1-14.(n-l ).

Во время действия синхросигнала и-го такта с выхода (и-I )-го разряда управляющего регистра 15 единичный управляющий сигнал поступает через (n-1)-й элемент И 16 ° (n-1) второй группы на первый вход (n-1 )-го элемента И 17.(п-l ) третьей группы.

Под действием этого единичного управляющего сигнала с выхода основного триггера первого фиксатора 25.1 суммы (и-1)-й распределительной ячейки

14.(n-l) на выход 19 устройства постунает информация, прошедшая через третий информационный выход 34 распределительной ячейки 1 4.(п-l ), (и-1 )-й элемент И 1 7.(n-l ) третьей группы, элемент ИЛИ 18. Одновременно с этими действиями производится обнуление дополнительных триггеров фиксаторов 25.2, 26.2, 27.2, 28.2 суммы и переноса (и-1)-й распределительной ячейки 1 4.(п-l ). При этом значение единицы сдвигается в и-й разряд управляющего регистра 15.

По синхросигналу n-ro такта

1 в первый разряд регистра 7 и в йервый триггер 8 записывается значение старшего разряда Ь сомножителя В ., „1 в каждый следующий разряд регистра 7 сдвигается значение предыдущего разряда coMHDRHTeJIH В 1, в и-й разряд

40 регистра 7 сдвигается. значение млад-, шего разряда Ь сомножителя BI Ha

11 выходе элементов И 12.2 " 12. (n-1) первой группы формируются старшие

О разряды различных по весу разрядов

45 частичных произведений а „, Ь,..., а.„, Ь „. На сумматорах 13.2—

13. (n-1 ) они суммируются соответственно со значениями промежуточной суммы частичных произведений и; ре50 зультат записывается в первые фиксаторы 25.1 и 27.1 суммы и переноса распределительных ячеек 14.2 14.(п-l).

В следующем такте начинается ввод второй пары сомножителей, а для первой пары сомножителей А и В закан1 чивает работу первый каскад конвейера.

1580352

13

5

1О !

20

С приходом синхросигнала (n+1)-го такта в первый разряд реги- . стра 6 записывается значение старшего разряда à сомножителя А . Одно1 временно с выхода n-ro разряда управ— ляющего регистра 15 единичный управляющий сигнал поступает через и-й элемент И 16.п второй группы на первый вход n-ro элемента И 17.п третьей группы, а также на вход пер вого разряда управляющего регистра

)5. Под действием этого единичного управляющего сигнала с выхода основного триггера первого фиксатора

25.1 суммы и-й распределительной ячейки 14.п на выход 19 устройства поступает нулевая информация,прошедшая через третий информационный выход 34 и-й распределительной ячейки 14.п, п-й элемент И 1 7.п третьей группы, элемент ИЛИ 18. В это же время производится обнуление дополнительных триггеров фиксаторов

25.2, 26.2, 27.2, 28,2 суммы и переноса п-й распределительной ячейки 14„п. При этом значение единицы сдвигается в первый разряд управляющего регистра 15.

Во время действия синхросигнала (и+1 )-го такта на выходах эле1 . ментов И 12 первой группы формируются младшие разряды частичных произведений предыдущей пары сомножителей

А1 и В „: а,Ь,..., а,Ь „. На сумматор ах 1 3 они суммируются соотв етств енно со значениями промежуточной суммы частичных произведений, и результат записывается во вторые фиксаторы

26.1 и 28.1 суммы и переноса распределительных ячеек 14.

С приходом синхросигнала (п +

+ 1 )-го такта в первый разряд регистра 7 и в первый триггер 8 записываются значения младшего разряда Ь„ сомножителя В2.

Во время действия синхросигнала ь „ (и+!)-ro такта на выходах элементов И 12 формируются старшие разряды частичных произведений предыдущей пары сомножителей: а,Ь „ ...à „Ь

На сумматорах 13 они суммируются соответственно со значениями промежуточной суммы частичных произведений, результат записывается в первые фиксаторы 25.1 и 27.1 суммы и переноса распределительных ячеек 14.

Со следующего такта для первой пары сомножителей А „ и В„ начинает работу второй каскад конвейера, а для второй пары сомножителей А и

В начинает работать первый каскад конвейера.

С приходом синхросигнала 8 (и +

+ 2)-го такта в первый разряд регистра 6 записывается значение разряда az сомножителя А>, во второй разряд регистра 6 и второй триггер 9 сдвигается значение разряда а,„ сомножителя А2. На выходе элемента

И 12.1 формируется первое частичное произведение а b . На сумматоре

ii

13.) . Оно су;- руется с нулевым значением суммы частичных произведений и результат записывается во вторые фиксаторы 26.1 и 28.1 суммы и переноса распределительной ячейки 14.1 в качестве промежуточного значения суммы частичных произведений.

Одновременно с этим с выхода первого разряда управляющего регистра

15 через первый злемепт И 16.1 второй группы единичный управляющий сигнал поступает на первый вход первого элемента И 17.1 третьей группы, управляющий вход 31 первой распределительной ячейки )4.1 и входы установки в .нуль триггеров разрядов регистров 6 и 7, начиная с дополнительных триггеров вторых разрядов регистров 6 и 7. Под действием этого единичного управляющего сигнала с выхода основного триггера первого фпкса-.ора .27.1 переиоса первой распределительной ячейки ) 4.1 через третий информационный выход 34 этой распределительной ячейки, перль ii э- н:ме! J i

И 17.1 трстьей группы, элемент ИЛИ 18 проходит нулевая информация на вход

19 устройства. В это же время производится обнуление дополнительных триггеров фиксаторов 25,2, 26.2, 27.2, 28. су:. ь:ы и пе,-, ånîoà п,;.:i, распределительной ячейки ) 4.1 и,начиная с дополнительного три гг ера в торого разряда регистра, обпуляются триггеры регистров 6 и 7. Прп этом значение единицы сдвигается во второй разряд управляющего регистра 15.

С приходом син iz (n +

+ 2)-го такта в первый разряд регистра 7 и в первый триггер 8 записывается значение .разряда Ь сомножите0 -1 ля В, во второи разряд регистра 7 сдвигается значение разряда Ь „сомножителя Б, По синхросигналу (n+2)-го такта па сумматоре !3.2 сум1580352

15 мируются (и-1)-е разряды двухрядного кода произведения первой пары сомножителей А и В, и получаемое при

1 1Э этом значение n-ro разряда округленного результата записывается в основной триггер первого фиксатора 25.1 суммы второй распределительной ячейки 14.2.

Со следующего такта начинается вывод и-разрядного округленного произведения первой пары сомножителей

А, и В,.

С приходом синхросигнала < (n +

+ 3)-ro такта в первый разряд регистра 6 записывается значение разряда аЗ сомножителя А2, во второй разряд регистра 6 и второй триггер 9 сдвигается значение разряда а сомножителя А, в третий разряд регистра 6 сдвигается значение разряда а, сомножителя А . На выходе элементов И 12.1 и 12.2 формируются младшие разряды второго частичного произведения: а b „„, a Ь „, . На сумматорах 13.1 и 13.2 они суммируются с промежуточным значением суммы частичных произведений, и результат записывается во вторые фиксаторы 26.1 и 28.1 суммы и переноса распределительных ячеек

14.1 и 14.2.

Во время действия синхросигнала

С„ (п+3)-ro такта с выхода второго разряда управляющего регистра 15 единичный управляющий сигнал поступает через второй элемент И 16.2 второй группы на первый вход второго элемента И 17.2 третьей группы и на управляющий вход 31 второй распределительной ячейки 14.2. Под действием этого единичного улравляющего сигнала с выхода основного триггера первого фиксатора 25.1 суммы второй распределительной ячеики 1 4.2 на выход 19 устройства поступает значение и-го разряда произведения первой пары сомножителей А и Б Одно1 ( временно производится обнуление дополнительных триггеров фиксаторов

25.2, 26.2, 27.2, 28.2 суммы и переноса второй распределительной ячейки 1 4.2. При этом значение единицы сдвигается в третий разряд управляющего регистра 15.

С приходом синхросигнала (n+3)-го такта в первый разряд регистра 7 и в первый триггер 8 записываются значения разряда Ь„ сомножителя В, во второй разряд регист16 ра 7 сдвигается значение разряда

Ь„, сомножителя В, а в третий разряд — значение младшего разряда

Ь„ сомножителя В . На выходе элемента И 12.2 формируется старший разряд второго частичного произведения а Ь „. На сумматоре 13.2 он суммируется с промежуточным значением суммы частичных произведений, и результат записывается в первые фиксаторы 25.1 и 27.1 суммы и переноса второй распределительной ячейки

14.2.

r!o синхросигналу (n+3)-го такта на сумматоре 13.3 выполняется сложение (n-2)-х разрядов двухрядного кода произведения первой пары сомножителей А и В и получен1 1

2О ное лри этом значение (n-1)-ro разряда округленного результата записывается в основной триггер первого фиксатора 25.1 суммы третьей распределительной ячейки 14,3.

25 Аналогичные действия выполняются устройством для умножения в течение следующих тактов работы. Особенностью

2п-го такта является получение сразу двух разрядов результата — второго

3О и первого как значение суммы и переносов. По синхросигналу (2п-ro

1 такта в первый разряд регистра 6 записывается значение разряда а „ сомножителя А, во второй разряд регист35 ра 6 и второй триггер 9 сдвигается значение разряда а „, сомножителя

А, в каждый следующий разряд сдвигается значение предыдущего .разряда сомножителя А, в и-й разряд регист4О ра 6 сдвигается значение разряда а, сомножителя А 2. На выходе элементов И 12.1 — 12.(n-1) формируются младшие разряды различных по весу разрядов частичных произведений:

45 а,Ь ..., а „, b<. На сумматорах

13.1 — 13. (n 1) они суммируются со значениями промежуточной суммы частичных произведений, и результат записывается во вторые фиксаторы

26.1 и 28.1 суммы и переноса распределительных ячеек 14.1 — 14.(п-1).

Во время действия синхросигнала Г, 2n-ro такта с выхода (n-1)-го разряда управляющего регистра 15 единичный управляющий сигнал поступает через (n-1 )-й элемент И 16.(n-1) второй группы на первый вход (и-1)го элемента И 17.(n-1) третьей группы. Под действием этого единичного

1580352 управляющего сигнала с выхода основного триггера первого фиксатора

25.1 суммы (n-1)-й распределительной ячейки 14".(n-1) на выход 19 устройства поступает значение третьего разряда произведения первой пары сомножителей А, и В,, Одновременно производится обнуление дополнительных триггеров фиксаторов 25.2, 26.2, 27.2, 28,2 суммы и переноса (n- 1)-й распределительной ячейки 14.(n-l).

При этом значение единицы сдвигается в и-й разряд управляющего регистра 15.

По синхросигналу С 2п-го такта в первый разряд регистра 7 и в первый триггер 8 записывается значение старшего разряда b сомножите1 ля В, в каждый следующий разряд регистра 7 сдвигается значение предыдущего разряда сомножителя В, в и-й разряд регистра 7 сдвигается значение младшего разряда Ь „ сомножителя В . На выходе элементов И 12.2—

12.(n-l) первой группы формируются старшие разряды различных по весу разрядов частичных произведений а „, Ь,..., а „, Ь „. На сумматорах

13.2-13. (п-1 ) они складываются соответственно со значениями промежуточной суммы частичных произведений, и результат записывается в первые фиксаторы 25.1 и 27.1 суммы и переноса распределительных ячеек 14,2

14.(n — 1).

Во время действия синхросигнала ь, 2п-го такта на сумматоре 13.п выполняется сложение старших разрядов двухрядного кода произведения первой лары сомножителей А, и В,, и полученные при этом значения второго и первого разрядов округленного результата записываются соответственно в основной триггер первого фиксатора 25.1 суммы п-й распределительной ячейки 1 4.п и в основной триггер первого фиксатора 27.1 переноса первой распределительной ячейки 14.1.

Со следующего такта начинается ввод и устройство третьей пары сомножителей А и В1. Для второй пары сомножителей А и В заканчивается первый каскад конвейера.

С приходом синхросигнала 2,(2n+

+1 )-ro такта в первый разряд регистра 6 записывается значение старшего разряда а, сомножителя А 3. На

25

30. 26.2, 27.2, 28.2 суммы и переноса

55 выходах элементов И ) 2 первой группы формируются младшие разряды частичных произведений предыдущей пары сомножителей А и В : а „Ь,...,а„Ь„.

На сумматорах 13 они суммируются соответственно со значениями промежуточной суммы частичных произведений, и результат записывается во вторые фиксаторы 26.1 и 28.1 суммы и переноса распределительных ячеек 14, Во время действия синхросигнала (2n+1)-го такта с выхода п-го разряда управляющего регистра 15 единичный управляющий сигнал поступает через п-й элемент И 16.п второй группы на первый вход п-го элемента И 17.п третьей группы, а также на вход первого разряда управляющего регистра 15. Под действием этого единичного управляющего сигнала с выхода основного триггера первого фиксатора 25.1 суммы и-й распределительной ячейки 14.п на выход 19 устройства поступают значения второго разряда округленного произведения первой пары сомножителей А и В,. Одновре1 менно производится обнуление дополнительных триггеров фиксаторов 25.2, и-й распределительной ячейки 14.п с помощью единич ного сиг нала, прошедше. го через управляющий вход 31 и-й распределительной ячейки. При этом значение единицы сдвигается в первый разряд управляющего регистра 15.

С приходом синхросигнала С (2п+1)-ro такта в первый разряд регистра 7 и в первый триггер 8 записывается значение младшего разряда Ь и сомножителя В ..Во время действия синхросигнала Р (2п+1 )-ro такта на входах элементов И 12 формируются старшие разряды различных. по весу разрядов частичных произведений предыдущей пары сомножителей А и

В: а „Ь „..., а„Ь1. На сумматорах

13.2 — 13.п они суммируются соответственно со значениями промежуточной суммы частичных произведений, и результат записывается в первые фиксаторы 25.1 и 27,1 суммы и переноса распределительных ячеек 14.2 — 14.п.

На первом сумматоре 13.1 значение первого разряда произведения первой пары сомножителей А f и В„ суммируется с нулевой информацией и перезаписывается в основной триггер перво!

9 го фиксатора 25.1 суммы первой распределительной ячейки 14.1.

Со следующего такта для третьей пары сомножителей А и Вз начинается первый каскад конвейера, для второй пары сомножителей А и В начинается второй каскад конвейера. Для первой пары сомножителей А z» В заТ 1 канчивается вывод результата.

Во время действия синхросигнала (2n+2)-го такта первый разряд

Ь регистра 6 записывается в значении разряда а сомножителя А>, во второй разряд регистра 6 и во второй триггер 9 сдвигается значение разряда а, сомножителя А 3. На выходе элементов И 12.1 формируется первое

1 частичное произведение а Ь „. На сумматоре 13.1 оно суммируется с нулеBbzM значением суммы частичных произведений, и результат записывается во вторые фиксаторы 26.1 и 28.1 суммы и переносов распределительной ячейки 14.1 в качестве промежуточного значения суммы частичных произведений.

По синхросигналу i (2n+2)-ro

1 такта с выхода первого разряда управляющего регистра 15 единичный управляющий сигнал поступает через первый элемент И 16.1 второй группы на первый вход первого элемента

И 17.1 третьей группы, управляющий вход 31 первой распределительной ячейки 14.1 и входы установки в нуль триггеров разрядов регистров 6 и 7, начиная с дополнительных триггеров вторых разрядов регистров 6 и 7.Под действием единичного управляющего сигнала с выхода основного триггера первого фиксатора 27.1 суммы первой распределительной ячейки 14.1 через третий йнформационный выход 34 этой распределительной ячейки, первый элемент И 17,.1 третьей группы, элемент ИЛИ 18 на выход 19 устройства поступает старший разряд произведения первой пары сомножителей А „ и

В ; Б это время производится обнуле1 . ние дополнительных триггеров фиксаторов 25.2, 26.2, 27.2, 28.2 суммы и переноса первой распределительной ячейки 14.1 и, начиная с дополнительного триггера разряда регистра, обнуляются триггеры регистров 6 и 7.

При этом значение единицы сдвигается во второй разряд управляющего регистра 15.

1580352

Во время деиствия синхросигнала .(2n+2)-ro такта в первый разряд регистра 7 и первый триггер 8 записывается значение разряда Ь „, сомножителя В, во второй разряд регистра 7 сдвигается значение разряда

Ь, сомножителя В °

По синхросигналу g (2n+2)-го такта на сумматоре 13.2 суммируются (п-1 )-е разряды двухрядного кода произведения второй пары сомножителей

А и Вд, и получаемое при этом значение n-ro разряда округленного результата записывается .в основной триггер первого фиксатора 25.1 суммы второй распределительной ячейки 14.2.

Закончен вывод произведения первой пары сомножителей. Со следующего так20 та начинается вь:вод произведения второй пары сомножителей.

С приходом синхросигнала (2n+3)-ro такта в первый разряд регистра 6 записывается значение разря25 да а> сомножителя Ад, во второй разряд регистра 6 и второй триггер 9 сдвигается значение разряда а сомножителя Аз, в третий разряд регистра 6 сдвигается значение разряда а, 3р сомножителя А . На выходе элементов

И 12.1 и 12.2 формируются младшие разряды второго частичного произведения ash. и,, а „Ь „, На сумматорах

13.1, 13.2 они суммируются с промежуточным значением суммы частичны