Устройство микропрограммного управления

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано, в частности в микропроцессорных системах. Цель изобретения является сокращение объема памяти микрокоманд. Устройство содержит регистр 1 команд, блок 2 памяти микрокоманд, регистр 3 адреса, блок 4 памяти перенастройки, регистр 5 микроопераций, регистр 6 условий. Указанная цель достигается благодаря перенастройке запоминающих узлов регистра адреса в процессе работы устройства (программно) на D- или Т-триггеры. 3 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИК

РЕСПУБЛИК

„„SU 1580361

А1 (1)5 С 06 Р 9/22ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОВСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4468460/24-24 (22) 10,08, 88 (46) 23,07,90,Бюл. У 27 (71) Институт проблем управления (72) В.Ф. Криворучко (53) 681. 32 (088.8) (56} Баранов С.И., Баркалов А.А,Применение ПЛМ в цифровой технике.—

Зарубежная радиоэлектроника, 1982, 6, с6779, рис6.—

Там же, рис.8, (54) УСТРОЙСТВО МИКРОПРОГРАММНОГО УП

РАВЛЕНИЯ

2l (57) Изобретение относится к вычислительной технике и может быть использовано, в частности в микропроцессорных системах. Целью изобретенйя явля ется сокращение объема памяти микрокоманд. Устройство содержит регистр I команд, блок 2 памяти микрокоманд, регистр 3 адреса, блок 4 памяти перенастройки, регистр 5 микроопераций регистр 6 условий, Указанная цель дос" тигается благодаря перенастройке sano-. минающих узлов регистра адреса в процессе работы устройства (программно) íà D- или Т-триггеры, 3 ил.

158036 1

Изобретение относится к вычислит льной технике и может быть использовано, в частности в микропроцессорных системах.

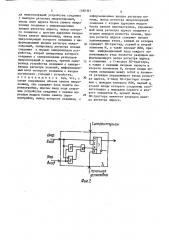

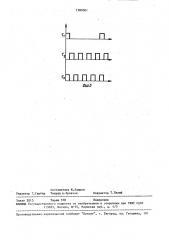

Целью изобретения является сокращение объема памяти микрокоманд, На фиг,l представлена функциональная схема устройства; на фиг,2— схема запоминающего узла регистра адреса; на фиг.3 — временная диаграмма сигналов синхронизации.

Устройство содержит регистр 1 команд, блок 2 памяти микрокоманд, регистр 3 адреса, состоящий из запоминающих узлов 3 - 3, блок 4 памяти

1 перенастройки, регистр 5 микроопераций, регистр 6 условий, Запоминающий узел 3; (i=1, N) регистра адреса (фиг,2 ) содержит 20

IK-триггер 7, первый 8 и второй 9 элементы И, элемент ИЛИ 10.

Запоминающий узел регистра адреса настраивается на два типа триггеров: Э- или Т-триггер. Подача на уп" 25 равляющий вход сигнала "0" или "1" определяет соответственно настройку узла на реализацию D- или T-триггера, Цепи начальной установки в целях 3!) упрощения не показаны.

Устройство работает следующим образом.

Перед поступлением каждого кода операции в устройство по сигналу на35 чальной установки регистры 1, 3, 5 и 6 устанавливаются в начальное сос« тояние. При поступлении на вход кода операции устройства на выходе блока

4 памяти перенастройки формируется . начальный адрес микропрограммы и код настройки регистра адреса, которые заносятся в регистр 1 команд по сигналу ñ,. Начальный ад- 45 рес микропрограммы с выхода регистра команд поступает на первый адресный вход блока 2 памяти, реализованного на программируемой логической матрице (ПЛМ), и определяет установку адреса начальной микрокоманды микропрограммы данной команды. Микрооперации, реализуемые в микрокоманде, поступают на информационный вход регистра 5, Адресная часть микрокоманды поступает на информационные входы запоминающих узлов регистра адреса, На управляющие входы запоминающих узлов регистра адреса по соответствующему выходу регистра команд поступает код настройки, настраивающий запоминающие узлы регистра адреса на тот набор типов триггеров, который является оптимальным с точки зрения достижения минимального объема

IIHM данного фрагмента команды, состоящей, например, из четырех микрокоманд, По сигналу г информация записывается в регистры 3 и 5. С выхода регистра 5 микрооперации выдаются на выход устройства. Коды адреса на первых и третьих входах адреса блока 2 памяти, а также значения логических условий1 записываемые в регистр 6 условий по сигналу после выполнения микрокоманды определяют значение. адреса следующей выполняемой микрокоманды микропрограммы, На второй адресный вход блока 4 памяти перенастройки поступает код микроопераций с выхода регистра 5, который одновременно является частью адреса блока 4.

На выходе блока 4 в зависимости от кода выполняемой команды на первом адресном входе блока 4 и кодака втором адресном входе (с .выхода регистра 5) формируется код, состоящий из двух частей. Первая часть подтверждает код выполняемой команды, а вторая — содержит код настройки регистра 3 адреса. Через четыре такта сигнала по следующему сигналу Г„ информация на выходе блока 4 запишется в регистр 1 команд, По второму выходу регистра 1 код настройки настраивает запоминающие узлы регистра адреса на оптимальный набор типов триггеров, минимизирующий объем

ПЛМ следующей части микропрограммы, состоящей из четырех микрокоманд, далее устройство работает аналогично описанному выше. Последняя микрокоманда любой операции содержит признак окончания операции, из обретения

Формул а 1

Устройство микропрограммного управления, содержащее регистр команд, блок памяти микрокоманд, регистр адреса, регистр микроопераций, регистр условий, причем первый выход регистра команд соединен с первым адресным входом блока памяти микрокоманд, второй адресный вход которого соединен с выходом регистра условий, выход ко1580361 устпюдка

Фиг.2 да микроопераций устройства соединен с выходом регистра микроопераций выход поля адреса блока памяти микрокоманд соединен с информационным входом регистра адреса, выход которого соединен с третьим адресным входом блока памяти микрокоманд, выход поля микроопераций которого соединен с информационным входом регистра микроопераций, синхровход регистра команд соединен с первым синхровходом устройства, второй синхровход которого соединен с синхровходами регистров микроопераций и адреса, третий синхровход устройства соединен с синхровходом регистра условий, информационный вход -которого соединен с входом логических:- условий устройства, о т л и ч а ю щ е е с я тем, что, с целью сокращения объема памяти микрокоманд, оно содержит блок памяти перенастройки, причем вход кода операции устройства соединен с первым адресным входом блока памяти перенастройки, выход которого соединен с информационным входом регистра команд, выход регистра микроопераций соединен с вторым адресным входом

5 блока памяти перенастройки, управляющий вход регистра адреса соединен с вторым выходом регистра команд, причем регистр адреса содержит группу запоминакнцих узлов, каждый из которых

10 содержит IK-триггер, первый и второй элементы И, а также элемент ИЛИ, причем информационный вход каждого saпоминакнцего узла является разрядом информационного входа регистра адреса и соединен с Е-входом IK-триггера, а также с первыми входами первого и второго элементов И, вторые входы которых соединены между собой и являются разрядом управляющего входа регистра адреса, К-вход IK-триггера соединен с выходом элемента ИЛИ, первый и .второй входы которого соединены соответственно с выходами первого и второго элементов И, прямой выход

IK-триггера является разрядом выхода регистра адреса.

1580361

Составитель Ю.Ланцов

Редактор Г, Гербер Техред A.Êðàâ÷óê Корректор Т.Палий

Заказ 2013 Тираж 570 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, .Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101