Устройство для сопряжения процессора с сетевым контроллером

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении сетей ЦВМ. Целью изобретения является повышение пропускной способности устройства за счет уменьшения времени ожидания процессором права доступа к общей памяти. Поставленная цель достигается тем, что в устройство, содержащее два регистра адреса 5, 13, два регистра данных 6, 14, два селектора адреса 2, 15, общую память 12, триггер 10, элемент НЕ 11, введены арбитр 3, блок управления общей памятью 4, триггеры 7 - 9. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU „„1580384 (g1)g G 06 F 13/14

ОПИСАНИЕ ИЗОБРЕТЕНИЯ:

ГОсудАРст8енный ИОмитет

1 1О изОБРетениям и ОтнРытиям

Г1РИ ГКНТ СССР

К АBTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 4485478/24-24 (22) 21.09,88 (46) 23 ° 07.90. Вюл. Р 27 (71) Новосибирский электротехнический институт (72) Л.А.Акульшина, Ю.Ф,Ерофеев и Р.Г.Карымов (53) 681.325(088.8) (56) Прангишвили И.В, Микропроцессорные и локальные сети микро-ЭВМ в распределенных системах управления.H.:

Энергоатомиздат, 1985, с. 212, 213ь 219 227 °

ЕР Ф 0174446, кл. С 06 Р 13/14, опуВпик. 1986, 2 (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПРОЦЕССОРА С CETEBbB КОНТРОЛЛЕРОМ (57) Изобретение относится к вычислительной технике и может быть использовано при построении сетей ЦВМ. Целью изобретения является повышение пропускной способности устройства за счет уменьшения времени ожидания процессором права доступа к общей памяти. Поставленная цель достигается тем, что в устройство, содержащее два регистра адреса 5, 13, два регистра данных 6, 14, два селектора адреса 2, 15, общую память 12, триггер 10, элемент НЕ 11, введены арбитр 3, блок управления общей памятью 4ьтриггеры 7-9, 2 нл, 1580384

Изобретение относится к вычислительной технике и может быть использовано при построении сетей ЦВМ.

Целью изобретения является повыше. 5 ние пропускной способности устройства путем уменьшения времени ожидания процессором права доступа к общей памяти.

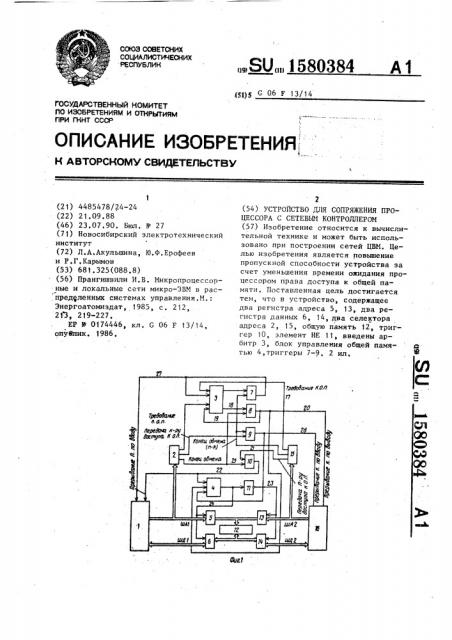

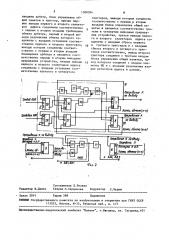

На фиг.1 представлена блок-схема 10 устройства; на. фиг,2 — примеры реализации блока управления общей памятью и арбитра.

На блок-схема (фиг.1) показаны процессор 1 (в устройство не входит), селектор 2 адреса, арбитр 3, блок 4 управления общей памятью, регистр 5. адреса, регистр 6 данных, триггеры

7-10, элемент НЕ 11, общая память 12, регистр 13 адреса, регистр 14 данных, селектор 15 адреса, сетевой контроллер 16 (в устройство не входит), связь 17 требования контроллером доступа к общей памяти, связь 18 установки в " 1" триггера 7, связь 19 бло- 25 .кировки арбитра от контроллера, связь

20 прерывания контроллера по выводу, связь 21 разрешения процессору доступа к .общей памяти, связь 22 прерывания процессора по вводу связь 23

Э

30 разрешения записи в буферы контроллера, связь 24 разрешения записи, связь 25 — конец обмена, связь 26 прерывания контроллера по вводу, связь

27 прерывания процессора по выводу.

Арбитр 3 (фиг.2) содержит триггеры 28-31, элемент ИЛИ 32, генератор

33, элементы И 34 и 35, элемент НЕ 36.

Блок 4 управления общей памятью (фиг.2) содержит элемент ИЛИ 37, . 4 элемент HE 38, элемент И 39.

Устройство работает следующим образом.

Если инициатором обмена является процессор 1, то он выставляет на шину адреса код, по которому селектор 2 адреса вырабатывает сигнал требования, поступающий на арбитр. По этому сигналу арбитр 3 совместно с триггером 7 формирует сигнал ире» рывания, который блокирует входы арбитра 3 и запускает в процессоре программу вывода информации. в общую память 12. Далее процессор выставляет на шину адреса код, по которому селектор 2..адреса вырабатывает сигнал.55 разрешения. Под действием этого сигнала на выходе триггера 9 формируется сигнал, который через блок 4, эле/ мент HE 11 и регистры 3 и 14 подключает сетевой контроллер 16 к общей памяти 12. Сигнал с выхода триггера, 9 в качестве прерывания поступает также на вход контроллера 16,. Получив сигнал прерывания с триггера 9, контроллер 16 выполняет программу ввода данных из общей памяти 12. По окончании процедуры ввода контроллер 16 на шину адреса выставляет код, по которому селектор 15 адреса вырабатывает сигнал - конец обмена, который устанавливает триггеры устройства в исходное состояние, Если инициатором обмена является контроллер, то устройство работает аналогично описанному.

При одновременном требовании обмена со стороны процессора 1 и контроллеРа 16 приоритет отдается контроллеру. Приоритет реализуется . в . арбитре 3.

Формула изобретения

Устройство для сопряжения процессора с сетевым контроллером, содержащее два регистра адреса, два регистра данных, общую память, два селектора адреса, три триггера н элемент НЕ, выход которого соединен с входами разрешения первых регистров адреса и данных, информационный вход, первого регистра данных соединен с входом первого селектора адреса и является первым адресным входом устройства, первый информационный входвыход первого регистра данных является первым входом-выходом данных ус тройства, выход первого регистра адреса через общую шину соединен с выходом второго регистра адреса и входом адреса общей памяти, второй входвыход первого регистра данных через общую шину соединен с первым входомвыходом второго регистра даннных и информационным входом-выходом общей памяти, информационный вход второго регистра адреса соединен с входом второго селектора и является вторым адресным входом устройства, второй информационный вход-выход регистра даннйх является вторым входом-выходом данных устройства, о т л и ч а ю щ ее с я. тем, что, с целью повышения пропускной способности за счет уменьшения времени ожидания процессором права доступа к общей памяти, в него

1580384 (2

: тр

Составитель Б.Резван

Редактор В.Данко Техред Л.Сердюкова Корректор С.Черни

Заказ 2014 Тираж 568 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям прн ГКНТ СССР

113035, Москва, Ж-35, Раушская наб. ° д. 4/5

Производственно-издательский комбинат Патент, г.ужгород, ул. Гагарина, 1 1

11 1!

Г на 101 введены арбитр, блок управления общей памятью и триггер, причем первые выходы первого и второго селекторов афреса соединены соответственно с первым и вторым входами требования обмена арбитра, первый и второй выходы разрешения обмена которого соединены с входами установки соответственно первого и второго триггеров, выходы которых соединены соответственно с первым и вторым входами блокировки арбитра и являются соответственно первым и вторым выходами прерывания устройства, вторые выходы первого и второго селекторов адреса соединены с входами установки соответственно третьего и четвертого триггеров, выходы которых соединены соответственно с первым и вторым входами блюка управления общей памятью и являются соответственно третьим и четвертым выходами прерывания устройства, третьи выходы первого и второго селекторов адреса соединены с входами сброса первого и третьего триггеров и с входами сброса второго и четвертого триггерон соответственно, выход второго .триггера соединен с третьим входом блока управления общей памятью, выход которого соединен с входом элемента НЕ и с входами разрешения вторых регистров адреса и данных.