Линейный экстраполятор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике. Цель изобретения - повышение точности и помехозащищенности достигается за счет поочередной работы двух экстраполирующих каналов, подключаемых к входу и выходу с помощью переключателей. Каждый канал содержит запоминающий элемент и периодически подключаемый к нему интегратор со сбросом. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„.,Я0„„158О404 (51)5 G 06 С 7/30

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4618819/24-24 (22) 09.12.88 (46) 23.07.90. Бюл. У 27 (72) Е.В.Архангельский, А.А.Замбржицкий, Н,А.Муратова, Г.-В.A.Ñâèöûí и Ю.H.Ñåìåíîâ (53) 681.3 (088.8) (56) Авторское свидетельство СССР

N 698012, кл. G 06 G .7/30, 1978.

Кузин Л.Т. Расчет и проектирование дискретных систем управления. — М.:

Машиностроение, 1962.

Изобретение относится к аналоговой вычислительной технике.

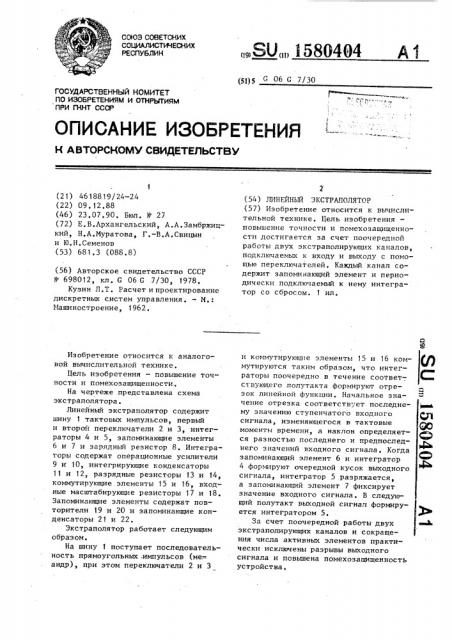

Цель изобретения — повышение точности и помехозащищепности, На чертеже представлена схема экстраполятора.

Линейный экстраполятор содержит шину t тактовых импульсов, первый и второй переключатели 2 и 3, интеграторы 4 и 5, запоминающие элементы

6 и 7 и зарядный резистор 8. Интеграторы содержат операционные усилители

9 и 10, интегрирующие конденсаторы

11 и 12, разрядные резисторы 13 и 14, коммутирующие элементы 15 и 16, входные масштабирующие резисторы 17 и 18.

Запоминающие элементы содержат повторители t9 и 20 и запоминающие конденсаторы 2t и 22.

Экстраполятор работает следующим образом.

На шину 1 поступает последовательность прямоугольных .импульсов (ме-. андр), при этом переключатели 2 и 3 (54) ЛИНЕЙНЫЙ ЭКСТРАЛОЛЯТОР (57) Изобретение относится к вычислительной технике. Цель изобретения повышение точности и помехозащищенности достигается за счет поочередной работы двух экстраполирующих каналов, подключаемых к входу и выходу с помощью переключателей. Каждый канал содержит запоминающий элемент и периодически подключаемый к нему интегратор со сбросом. 1 ил. и коммутирующие элементы 15 и 16 коммутируются таким образом, что интеграторы поочередно в течение соответ-. С ствующего полутакта формируют отрезок линейной функции. Начальное значение отрезка соответствует последнему значению ступенчатого входного Сз сигнала, изменяющегося в тактовые QO моменты времени, а наклон определяет- р ся разностью последнего н предпослед- р него значений входного сигнала. Когда запоминающий элемент 6 и интегратор

4 формируют очередной кусок выходного сигнала, интегратор 5 разряжается, а запоминающий элемент 7 фиксирует значение входного сигнала. В следующий полутакт выходной сигнал формируется интегратором 5.

За счет поочередной работы двух экстраполирующих каналов и сокращения числа активных элементов практически исключены разрывы выходного сигнала и повышена помехозащищенность устройства.

1580404

Ф о р м у л а и з о б р е т е н и я

Составитель Г.Осипов

Редактор О.Юрковецкая Техред М.Ходанич Корректор C.шевкун

Заказ 2015 Тираж 564 Подписное

ВНИИПИ Государственного. комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101

Линейный экстраполятор, содержащий первый запоминающий элемент и первый интегратор, выполненный на операционном усилителе с входным масштабирующим резистором, интегрирующим конденсатором, включенным между инвертирующим входом и выходом операционного усили- 10 теля, и с разрядной цепью, содержащей разрядный резистор и коммутирующий э цемент, подвижный контакт которого соединен с инвертирующим входом оперйционного усилителя, а замыкающий контакт через разрядный резистор с выходом операционного усилителя, отличающийся тем, что, с,целью повышения точности и помехо. защищенности, в него дополнительно вредены второй запоминающий элемент, второй интегратор, два переключателя и зарядный резистор, каждый запоминающий элемент содержит запоминающий конденсатор, первая обкладка которого 25 соединена с шиной нулевого потенциала, и повторитель, вход которого соединен с второй обкладкой запоминающего кон. денсатора, информационный вход устройства соединен с неинвертирующнми вкодами операционных усилителей первого и второго интеграторов и через зарядный резистор с подвижным контактом первого переключателя, замыкающий и размыкающий контакты которого соединены с входами повторителей соответственно первого и второго запоминающих элементов, выход повторителя первого запоминающего элемента соединен через входной масштабирующий резистор первого интегратора с размыкающим контактом коммутирующего элемента первого интегратора, выход повторителя второго запоминающего элемента соединен через входной масштабирующий резистор второго интегратора с замыкающим контактом его коммутирующего элемента, при этом во втором интеграторе инвертирующий вход операционного усилителя соединен с подвижным контактом коммутирующего элемента, размыкающий контакт которого через разрядный резистор соединен с выходом операционного усилителя, выходы первого и второго и интеграторов соединены соответственно с размыкающим и замыкающим контактами второго переключателя, подвижный контакт которого соединен с выходом экстраполятора, вход тактовых импульсов устройства соединен с управляющими входами первого и второго переключателей и коммутирующих элементов интеграторов.