Устройство одновременного контроля n импульсных последовательностей в реальном масштабе времени

Иллюстрации

Показать всеРеферат

Изобретение может быть использовано в устройствах импульсной и вычислительной технике для контроля импульсных последовательностей в реальном масштабе времени. Цель изобретения - повышение быстродействия при сохранении достоверности контроля - достигается за счет введения в состав устройства арифметико-логического устройства (АЛУ) 1 и новых связей. Кроме того, устройство содержит N-разрядный регистр 2, квазислучайный кодовый преобразователь 3, выполненный в виде постоянного запоминающего устройства, содержащего массив из двух N-разрядных неповторяющихся двоичных чисел, размещенных случайным образом, N-разрядную шину 4 контролируемых импульсных последовательностей, шину 5 переключения функции преобразования, шину 6 начальной установки, шину 7 синхронизации, выход 8 устройства. Введение новых элементов и связей позволяет в 2 M раз, где M - разрядность шины 5, уменьшить объем квазислучайного кодового преобразователя 3, что уменьшает время минимального цикла работы устройства. 1 ил.

119) 01) СОО3 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИМ

РЕСПУБЛИК

А1 (5I)5 Н 03 К 5 19

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

° б

°

I 0CVAAPCTBEHHblA КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4358467/24-21 (22) 04.01.88 (46) 23.07.90. Бюл. 11 27 (72) Д.В.Комков, Д.П.Михалев и В.М.Чистов (53) 621.373.4(088.8) (56) Журанлев Ю.П. и др. Надежность и контроль ЭВМ. — M. Советское радио, 1978, с.144, рис.3.28.

Авторское свидетельстнî СССР

9 1394422, кл. Н 03 К 5/19, 1986, (54) УСТРОЙСТВО ОДНОВРЕМЕННОГО КОНТРОЛЯ И ИМПУЛЬСНЬИ ПОСЛЕДОВАТЕЛЬНОСТЕЙ

В РЕАЛЬНОМ МАСШТАБЕ ВРЕМЕНИ (57) Изобретение может быть использовано в устройствах импульсной и вычислительной техники для контроля импульсных последовательностей в реальном масштабе времени . Цель изобретения — повышение быстродействия при сохранении достоверности контроля—

2 дсстигается за счет введения в состав устройства арифметико-логического устройства (АЛУ) 1 и новых снязей.

Кроме того, устройство содержит и-разрядный регистр 2, кназислучайный кодовый преобразонатель 3, выполненный в виде постоянного запоминающего устройства, содержащего массив из двух и-разрядных неповторяющихся двоичных чисел, размещенных случайным образом, п-разряцную шину 4 контролируемых импульсных последовательностей1 шину 5

t переключения функции преобразования, шину б начальной установки, шину 7 синхронизации, выход 8 устройства.

Введение новых элементов и связей по т О зволяет в 2 раз, где ш — разрядность Е шины 5, уменьшить объем кваэислучайного кодоного преобразователя 3, что уменьшает время минимального цикла работы устройства. 1 ил.

1580543

Изобретение относится к радиотехнике и автоматике, н частности к импульсной и вычислительной технике, и может быть использовано в устройствах импульсной и вычислительнои техники -., 5 для контроля импульсных последовательностей в реальном масштабе времени.

Целью изобретения является увеличе- 0 ние быстродействия устройства при сохранении достоверности контроля.

Поставленная цель достигается тем, что в устройство введены арифметикологическое устройство и новые связи.

Увеличение, быстродействия дос игается эа счет расположения медленно работающего квазислучайного кодового преобразователя, выполненного, например, в виде ПЗУ, после п-разрядного регистра, что позволяет сократить время "-аписи контрольного кода на время срабатывания квазислучайного кодового преобразонателя, а также за счет уменьшеHHH объема KBG3HcJI l ÉHo o преобразователя н 2 раз, где m разрядность шины, что уменьшает время цикла работы устройства °

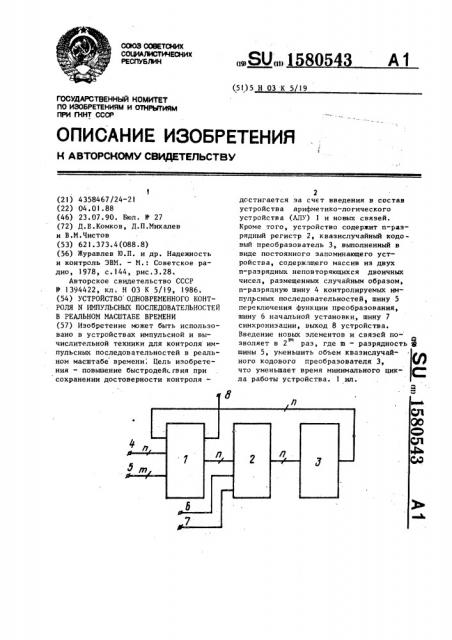

На чертеже изображена функциональная схема предлагаемого устройства.

В устройство входят арифметико-логическое устройство (АЛУ) 1, и-разрядный регистр 2, кваэислучайный кодовый преобразователь 3, и-разрядная шина 4 контролируемых импульсных

35 последовательностей, шины переключения функции преобразования 5, начальной установки 6 и синхронизации 7, выход Я устройства.

Устроиство состоит иэ АЛУ 1, lll входов управления которого соединены с шиной 5 переключения функции преобразования, и входов АЛУ 1 для подачи первого операнда являются и-разрядной шиной контролируемых импульсных псследовательностей, à и входов АЛУ 1 для подачи второго операнда соединены с и выходами .кваэислучайного кодового преобразователя 3.

Квазислучайный кодовый преобразователь 3 выполнен, например, в виде

50 постоянного запоминающего устройства (ПЗУ),имеющего и адресных входов и и выходов и содержащего 2 п.-разрядh ных ячеек памяти, в которых размещены квазислучайным образом 2 и-раз. рядных неповторяющихся двоичных чисел (н десятичном представленйи это чис,ло от 0 до 2 -15. Выход равенства ь нулю результата операции, выполняемой н АЛУ 1, является выходом 8 устройства. R-вход п-разрядного регистра 2 соединен с шиной 6 начальной установки, а С-вход и-разрядного регистра 2 соединен с шиной 7 синхронизации,п нходов и-разрядного регистра 2 соединены с и выходами АЛУ 1, а п выходов и-разрядного регистра 2 соединены с и входами квазислучайного кодового преобразователя 3.

Устройство работает следующим образом.

На шину 5 переключения функции преобразования подается m-разрядный код, который определяет операцию, выполняемую АЛУ 1. Затем на шину 6 на— чальной установки подается сигнал, устанавливающий и-разрядный регистр 2 н начальное состояние (например, нулевое), и-разрядный код с выхода регистра 2, проходя через квазислучайный кодовый преобразователь 3, преобразуется в другой и-разрядный код, который поступает на и входов АЛУ 1 для подачи нторого операнда. На этом начальные jjcTGHQBKH устройства заканчинают— ся, и устройство готово контролировать подаваемые на его импульсные последовательности. Затем на и-разрядную шину 4 контролируемых импульсных последовательностей подаются контролируемые импульсные последовательности, количество которых не должно превышать п, причем они должны сопровождаться подачей на шину 7 синхронизации синхроимпульсов, поступающих на

С-вход регистра 2, Фронт изменения и-разряднсй импульсной последовательности должен опережать передний фронт синхроимпульсов на время распространения сигналов в АЛУ 1.

Каждый синхроимпульс записывает в регистр 2:п-разрядный код результата выполненной в АЛУ 1 операции над первым и вторым операндами, С окончанием контролируемой последовательности заканчивают подачу синхроимпульсон на шину 7 синхронизации.

Далее на шину 5 переключения функции преобразования подается код операции поразрядного сравнения (Е ) первого и второго операндов или код операции вычитания первого операнда из второго ° На шину 4 для подачи контролируемых импульсных последовательностей подается п-разрядный эталонный код. Если и-разрядный код, полученный

1580543 на выходе преобразователя 3, в результате контроля совпадает по всем разрядам с эталонным кодом, то на выходе 8 устройства появляется уровень сигнала, свидетельствующий о правильности результата контроля. По наличию сигнала на выходе 8 устройства су. дят об исправности контролируемых импульсных последовательностей: если

10 есть сигнал, HcIIpBBHbl> если отсутствует, неисправны. Для определения исправности контролируемой последовательности могут быть использованы также выходы регистра 2, В этом случае необхо- 15 димо иметь и-разрядную схему сравнения и блок эталонньх кодов, причем выход схемы сравнения выполняет функции выхода равенства нулю АЛУ 1.

Предлагаемое устройство позволяет 20 увеличить быстродействие контроля и дает воэможность сравнивать результат контроля с эталоном, зафиксировать результат. сравнения, сохранив при этом высокую вероятность обнаружения корре.- gS лированных ошибок в произвольных импульсных последовательностях, т.е. сохранив эффективность и качество контроля устройств, формирующих контролируемые импульсные последовательности, ко- g0 торыми могут быть, например, многоразрядные кодовые последовательности, являющиеся частными случаями импульсных последовательностей.

Для современных усгройств автома35 тики, в которых для управления сложными объектами формируются одновременно на многих выходах сложные импульсные последовательности, особенно важно использование эффективного много- 40 канального устройства контроля, работающего в реальном масштабе времени.

Кроме того, использование предлагаемс— го устройства контроля позволит существенно поднять производительность 4 труда при проведении настроечных, рег— ламентных и ремонтных работ на различных устройствах автоматики и вычислительной техники. Если известны контрольные коды HB Bxcpcax H BbKo+Bx узлов .и блоков контролируемой аппаратуры, то, подключая последовательно предлагаемое устройство контроля к входам и выходам узлов и блоков аппаратур и проводя контроль, можно опре-. делить неисправный блок, а затем и неисправный узел. б

С помощью предлагаемого устройства контроля можно контролировать импульсные последовательности числом меньше и, вплоть до одиночной импульсной последовательности, тогда на свобод" ные и-1 входы устройства подается постоянный фиксированныч потенциал,и вероятность обнаружения ошибок в таких импульсных последовательностях при этом не уменьшается. Кроме того, устройство можно испольэовать для опознавания или идентификации импульсных последовательностей произвольной длины, для которых известны эталонные коды, причем опознавание можно вести с высокой, наперед заданной вероятностью.

Формул а изобретения

Устройство одновременного контроля и импульсных последовательностей в реальном масштабе времени, содержащее и-разрядный регистр, R-вход и

С-вход которого соединены соответственно с шиной начальной установки и шиной синхронизации, п-разрядную шину контролируемых импульсных последовательностей, шину для переключения функии преобразования, квазислучайный одовый преобразователь, выполненный в виде постоянного запоминающего устройства, имеющего п адресных входов и и содержащего массив из 2 и-разрядных нгповторяющпхся двоичных чисел, размещенных ква:и лучайным образом, о т л и ч а ю щ е е с я тем, что, с целью увеличения быстродействия при сохранении достоверности контроля, в него введено арифметико-логическое устройство, EEE входов которого соединены с itlHEioH переключения функции преобразования, первая группа входов арифметико-zEorEEwecE oro устройства соединена с и-разрядной шиной контролируемых импульсных последовательностей, вторая группа входов соединена с п выходами квазислучайного кодового преобразователя, и выходов соединены с входами и-разрядного регистра, выходы которого соединены с адресными входами квазислучайного кодового преобразователя, выход равенства нулю результата операции арифметико-логического устройства соединен с выходом устройства,