Следящий аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к аналогоцифровым преобразователям и может быть использовано в области вычислительной и измерительной техники, а также в автоматизированных системах управления технологическими процессами и в системах автоматизации научных исследований. Цель изобретения - повышение надежности при одновременном расширении диапазона входного сигнала. Для этого в преобразователь, содержащий генератор тактовых импульсов, первый, второй и третий логические блоки, первый и второй триггеры, блок сравнения, цифроаналоговый преобразователь, реверсивный счетчик, два элемента И, элемент задержки, группу элементов И, распределитель импульсов, введены нуль-орган, группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, два инвертора и триггер. При этом наличие в устройстве группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первого инвертора и нуль-органа позволяет отрабатывать биполярный входной аналоговый сигнал, а введение триггера и второго инвертора позволяет повысить надежность функционирования преобразователя. 1 з.п. ф-лы, 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

„„SU „„1580555 (51) 5 Н 03 M 1/48

ОПИСАНИЕ ИЗОБРЕТЕНИЯ н двтогскоьи свищткльствм

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ П4НТ СССР! (21) 4408013/24-24 (22) 11.04,88 (46) 23.07.90. Бюл. 9 27 (72) Ю.А.Андреев, В.А.Шувалов и В.П.Антонов (53) 681.325(088.8) (56) Авторское свидетельство СССР

У 797065, кл. H 03 M 1/48, 1979, Авторское свидетельство СССР

У 805489, кл. H 03 М 1/48, 1979. (54) СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ (57) Изобретение относится к аналогоцифровым преобразователям и может быть использовано в области вычислительнсй.и измерительной техники, а также в автоматизированных системах управления технологическими процессами и в системах автоматизации научных исследований. Цель изобретения — поИзобретение относится к аналогоцифровым преобразователям и может быть использовано в вычислительной и измерительной технике, а также в автоматизированных системах управления технологическими процессами и системах автоматизации научных исследований.

Цель изобретения — повышение надежности и расширение области применения за счет увеличения диапазона входного сигнала.

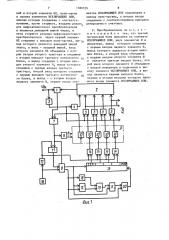

На фиг.l представлена функциональная схема следящего аналого-цифрового преобразователя; на фиг.2 — функцио2 вышение надежности при одновременном расширении диапазона входного сигнала, Для этого в преобразователь, содержащий генератор тактовых импульсов, первый, второй и третий логические блоки, первый и второй триггеры, блок сравнения, цифроаналоговый преобразователь, реверсивный счетчик, два элемента И, элемент задержки, группу элементов И, распределитель импульсов, введены нуль-орган, группа элементов

ИСКЛЮЧАЮЩЕЕ ИЛИ, два инвертора и триггер. При этом наличие в устройстве группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первого инвертора и нуль-органа позволяет отрабатывать биполярный входной (:2 аналоговый сигнал, а введение триггера и второго инвертора позволяет повысить надежность функционирования пре- VJ образователя. 1 з.п.ф-лы, 2 ил. нальная схема третьего логического .блока °

Преобразователь содержит блок 1 сравнения, цифроаналоговый преобразователь 2 (ЦАП), нуль-орган 3, элемент НЕ 4, группу элемечтов ИСКЛЮЧАЮЩЕЕ ИЛИ 5, логические блоки 6-8, реверсивный счетчик 9, состоящий из триггеров 10, первый ll, второй 12 и третий 13 триггеры, группы элементов

И 14, распределитель 15 импульсов, генератор 16 тактовых импульсов, элемент 17 задержки, элемент НЕ 18, элементы И 19 и 20. Третий логический блок содержит элемент ИСКЛЮЧАЮЩЕЕ

1580555

ИЛИ 21, элемент НЕ 22, элементы

И 23 и 24.

Блок 1 сравнения служит для сравнения входного сигнала U с образМ цовым уровнем По. Сигнал S на его выходе равен "О", если U ) U 9 и

9 если 1 11(Бо

Нуль-орган 3 предназначен для сравнения входного сигнала U< с ну— лем: если U„ ) О, то сигнал " на его выходе равен "О", если U„(0 то

V 1, Сигнал с выхода нуль-органа 3 имеет информацию о знаке входного сигнала и поступает на шину выходного сигнала, а также через первый элемент НЕ 4 йа старший разряд цифроаналогового преобразователя и на первые входы группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. Сигнал с выходов реверсивного счетчика проходит на младшие разряды цифроаналогового преобразователя с инверсией, если V = 1, и без инверсии, если V = О, тем самым обеспечивается четырехквадрантный режим работы цифроаналогового преобразователя, необходимый для обеспечения двухполярного образцового уровня.

Триггер 11 служит для запоминания ответа блока сравнения на предыдущем такте. Сигнал S на его выходе равен о

"1", если на предыдущем такте блок сравнения выдает сигнал S = 1.Сигнал на выходе первого логического блока 7 равен S = SII V SII, где П вЂ” сигнал с

35 выхода старшего разряда реверсивного счетчика.

На первом выходе третьего логического блока 8 сигнал f появляется при смене ответов блока сравнения на двух последовательных тактах f

1 (S S,чЯ„Я,)q, где S. — сигнал с выхода первого триго гера ll

q — сигнал от гененатора 16 тактовых импульсов.

На втором выходе третьего логического блока 8 сигнал проявляется при совпадении ответов блока сравнения послед2 (SîS VS S 9)q

Второй логический блок 6 при S 1

50 устанавливает режим вычитания реверсивного счетчика, а при S = Π— режим сложения.

Преобразователь работает следующим образом.

Сигнал начальной установки устанавливает первый 11, второй 12, третий 13 триггеры и реверсивный счетчик 9 в нулевое состояние, а в распредели" тель импульсов заносится код 0...10 (цепи начальной установки не показаны)

Так как в начале и при дальнейшей нормальной работе на выходе старшего разряда реверсивного счетчика присутствует сигнал П = О, то первый логический блок 7 пропускает на свой выход ответ блока сравнения без инвертирования.

После подачи входного сигнала, допустим положительной полярности (U 0) 9. блок 1 сравнения выдает сигнал S по которому с помощью второго логического блока 6 реверсивный счетчик переводится в режим сложения. Так как на первом триггере 11 хранится сигнал S, то третий логический блок 8 по сигналу от генератора тактовых импульсов выдает сигнал совпадения на второй выход, который устанавливает второй триггер в состояние "1". После этого сигнал с элемента 17 задержки добавляет единицу в разряд реверсивного счетчика, определяемый распределителем импульсов, и производит перепись ответа блока сравнения на первый триггер ll. После того как на третий вход третьего логического блока 8 поступит сигнал q с генератора 16 такто" вых импульсов, на его втором выходе появляется сигнал Е = О, который, пройдя через второй элемент НЕ 18 и элемент И 19, устанавливает третий триггер 13 в состояние "1". Предположим, что с приходом очередного сигнала от генератора тактовых импульсов блок l сравнения опять выдает сигнал S no которому второй логический блок 6 подтверждает режим сложения на реверсивном счетчике, а третий логический блок 8 выдает сигнал совпадения, который, пройдя через элемент И 20, производит сдвиг влево на один разряд содержимого распределителя импульсов.

После этого задержанный на линии задержки тактовый сигнал добавляет единицу в разряд реверсивного счетчика, определяемый распределителем 1.5 импульсов (вес этой единицы в два раза превышает вес предыдущей), и производит перепись ответа блока сравнения на триггер 11. Если далее опять поступают те же ответы от блока сравнения (S), то все происходит аналогично °

После первой смены ответа блока 1 сравнения, т.е. с приходом сигнала $

5 158 второй логический блок б переводит реверсивный счетчик в режим вычитания, а третий логический блок 8 выдает на первом выходе сигнал несовпадения текущего (S) и предыдущего (S) ответов блока сравнения. который производит сдвиг вправо на один разряд содержимого распределителя )5 импульсов и устанавливает второй !2 и третий 13 триггеры в "О". Затем задержанный на элементе 17 задержки сигнал от генератора 16 тактовых импульсов вычитает единицу из разряда реверсивного счетчика 9, определяемого распределителем импульсов, при этом вес единицы в два раза меньше веса предыдущей.

Если ответ блока 1 сравнения опять меняется (S), то происходит сдвиг вправо, и шаг квантования уменьшается в два раза. Если ответ блока 1 сравнения повторяется (S), то из-за нулевого состояния третьего триггера 13 сдвиг в распределителе !5 импульсов не происходит, величина шага квантования не меняется, но триггер 12 переходит в "!It Тем самым достигается режим работы преобразователя, позволяющий увеличить надежность преобразования, После этого с приходом сигнала q с генератора 16 тактовых импульсов на третий вход третьего логического блока 8 на его выходе появляется сигнал fq= О, который, пройдя через элемент HE 18 и элемент

И 19, устанавливает третий триггер 13 в состояние ".1 . С приходом следующего сигнала S из-за состояния "1" триггера 13 происходит сдвиг влево содержимого распределителя !5 импульсов и величина шага квантования удваивается.

При смене знака входного сигнала (V (0).на выходе нуль-органа 3 появv ляется сигнал V, который поступает на первые входы группы элементов

ИСКЛЮЧАЮЩЕЕ ИЛИ 15, которая пропускает на свои выходы проинвертированные сигналы с выходов реверсивного счетчика 9, в результате чего образцовый уровень на выходе цифроаналогового преобразователя меняет свой знак.

В остальном работа преобразователя аналогична указанному.

Если из-за большой скорости изменения сигнала вблизи границ диапазона происходит переполнение реверсивного счетчика, т.е. устанавливается код

> 01...! (нижняя и верхняя границы диапазона одинакuçbt и определяются модулем максимапьного входного сигнала), то иэ-за положения."!" старшего разряда реверсивного счетчика первый логический блок 7 передает на свой вьгход проинвертированный сигнал блока сравнения. Процесс работы остальных блоков преобразователя совпадает

10 с указанным.

Двоичный дополнительный код, характеризующий величину входного сигнала, снимается с выхода группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ вЂ” модуль числа, а с выхода нуль-органа — знак числа. формула изобретения!. Следящий аналого-цифровой пре?О образователь, содержащий блок сравнения, первый вход которого является входной шиной, а второй вход соединен с выходом цифроаналогового преобразователя, а выход соединен с первым

25 входом первого логического блока, второй вход которого соединен с выходом старшего разряда реверсивного счетчика, а выход соединен с первым входом первого триггера, с входом второго

3р логического блока и с первым входом третьего логического блока, второй вход которого соединен с выходом первого триггера, а третий вход объединен с входом элемента задержки и подключен к выходу генератора тактовых

35 импульсов, выход элемента задержки соединен со вторым входом первого триггера и с первыми входами группы элементов И, вторые входы которых соеди40 нены с соответствующими выходами распределителя импульсов, первый вход которого объединен с первым входом второго триггера и подключен к первому выходу третьего логического блока, второй выход которого соединен с первым входом первсг.о элемента И, выход которого соединен с вторым входом распределителя импульсов, первый вход второго элемента И соединен с выхо50 poM BToporo тригrepa, выходы BToporo логического блока соединены с входами управления счетом реверсивного счетчика, входы установки которого соединены с соответствующими выходами группы элементов И, отличающийся

55 тем, что, с целью повышения надежцости и расширения области прил1еыения за счет увеличения диапазона входного сигнала, введены третий триггер, пер1580555 вый и второй элементы НЕ, нуль-орган и группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых соединены с соответствующими, кроме старшего, входами разрядов цифроаналогового преобразователя

5 и являются, выходной шиной числа, а вход старшего разряда цифроаналогового преобразователя через первый элемент

НЕ соединен с выходом нуль-органа, выl0 ход которого является выходной шиной знака, а вход — входной шиной, вход второго элемента НЕ объединен с вторым входом второго триггера и соединен с вторым выходом третьего логического 15 блока, а выход соединен с вторым вхо\ дом второго элемента И выход которого соединен с первым входом третьеготриггера, второй вход которого соединен с первым выходом третьего логическо- 20

ro блока, и выход — с вторым входом первого элемента И, первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к выходу нуль-органа, а вторые входы соединены с соответствующими выходами реверсивного счетчика.

2. Преобразователь по п.1, о т л и ч а ю шийся тем, что третий логический блок выполнен на элементе

ИСКЛЮЧАЮЩЕЕ ИЛИ, двух элементах И и инвертбре, выход которого соединен с первым входом первого элемента И, выход которого является вторым выходом блока, а второй вход объединен с первым входом второго. элемента И и является третьим входом блока, вто. рой вход второго элемента И объединен с входом инвертора и подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход является первым выходом блока, первым и вторым входами которого являются входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

1580555

Составитель И.Романова

Техред Л.Сердюкова

Корректор М. Кучерявая

Редактор И.Горная

Заказ 2022 Тираж 669 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101