Преобразователь прямого 1-кода фибоначчи в обратный 1-код фибоначчи

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и автоматике и может быть использовано в отказоустойчивых системах обработки данных. Цель изобретения является повышение быстродействия. Для достижения поставленной цели в преобразователь , содержащий первый блок 4 элементов И, блок 5 приведения 1-кодов Фибоначчи к минимальной форме и блок 6 синхронизации, введены второй блок 8 элементов И, блок 7 контроля, инвертирующий денормализатор 3 и соответствующие функциональные связи, что позволяет реализовать более рациональный алгоритм получения обратных 1-кодов. При этом в среднем уменьшается количество сверток при формировании обратных 1-кодов Фибоначчи из прямых. 1 з.п.ф-лы, 3 ил.

СОЮЗ СОВЕТСНИХ

РЕСПУБЛИК

„.SU„„1580 (51)5 Н 03 М 7/02

А1

ОПИСАНИЕ ИЗОБРЕТЕНИ1

Н А STOPCHOMV СВИДЕТЕЛЬСТВУ (21) 4486824/24-24 (22) 26.09.88 (46) 23.07.90. Бюл. В 27 (72) С.Н.Мордашов (53). 681.3 (088.8) ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ П НТ СССР

I (56) Авторское свидетельство СССР

У 1392554, кл. Н 03 М 7/02, 1976.

Авторское свидетельство СССР !! 1032448, кл. Н 03 М 7/02, 1982. (.54) ПРЕОБРАЗОВАТЕЛЬ ПРЯМОГО I-! ОДА

ФИБОНАЧЧИ В ОБРАТНЫЙ I-КОД ФИБОНАЧЧИ

4 (57) Изобретение относится к вычислительной технике и автоматике и может быть использовано в отказоустойчивых

2 системах обработки данных. Целью изобретения является повышение быстродействия, Для достижения поставленной цели в преобразователь, содержащий первый блок 4 элементов И, блок 5 привецения I-кодов Фибоначчик минимальной форме и блок 6 синхронизации, введены второй блок 8 элементов И, блок 7 контроля, инвертирующий декор" мализатор 3 и соответствующие функциональные связи, что позволяет реализовать более рациональный алгоритм получения обратных I-кодов. При этом в среднем уменьшается количество сверток при формировании обратных

1-кодов Фибоначчи из прямых. 1 з.п. ф-лы, 3 ил.

1580560

Изобретение относится к вычислительной технике и может быть исполь-! зовано в отказоустойчивых системах обработки данных.

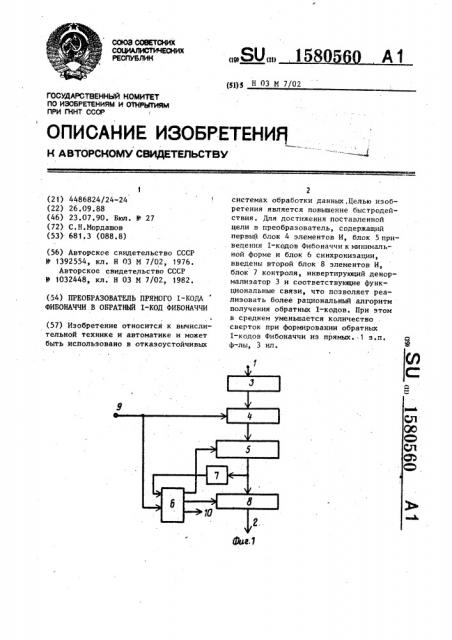

Целью изобретения является повышение быстродействия. ,На фиг. 1 представлена схема преобразователя прямого I-кода Фибоначчи в обратный I-код Фибоначчи; на фиг.2- 10, схема блока, синхронизации; на фиг.3— ! схема блока контроля.

Преобразователь (фиг.1) содержит

Iинформационный вход 1 преобразоваi теля, информационный выход 2 преобра- 15

: зователя, инвертирующий денормализатор 3, первый блок 4 элементов И, блок

5 приведения I-кодов Фибоначчи к минимальной форме, блок 6 синхронизации, блок 7 контроля, второй блок 8 20 элементов И, вход 9 запуска преобразователя и контрольный выход 10 пре, образователя.

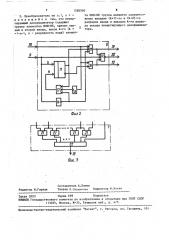

Блок 6 синхронизации (фиг.2) содержит триггер 11, элемент ИЛИ-НЕ 12, 25 первый 13 и второй 14 элементы НЕ, с первого по третий элементы И 15-17, вход 18 останова блока 6 синхрониза ции, первый 19 и второй 20 выходы блока 6 синхронизации, причем вход 30 запуска блока 6 синхронизации соединен с входом установки в единицу триггера 11 и с входом второго элемента НК 14, вход 18 останова блока

6 синхронизации соединен с первыми входами первого 15 и второго 16 элементов И и входом первого элемента HE

13, прямой выход триггера 11 соединен со вторым входом элемента И 15 и первым входом третьего элемента И 17, 40 выход которого соединен с входом установки в нуль триггера 11, инверсный выход которого соединен со вторйм входом элемента И 16, выход элемента

И 15, вход запуска блока 6 синхронизации и выход элемента И 16 соединены соответственно с входами элемента

ИЛИ-НЕ 12, выходы элемента И 15, элемента ИЛИ-НЕ 12 и элемента И 16 являются соответственно выходами с первого по третий блока 6 синхронизации, выход элемента НЕ 13 соединен со вторым входом элемента И 17, третий вход которого соединен с третьим входом элемента И 15 и выходом элемента НЕ 14 5

Блок 7 контроля (фиг.3) содержит группу элементов И 21 и элемент ИЛИ

22, причем входы разрядов со второго по (и-1)-й входа блока 7 контроля соединены соответственно с первыми входами элементов И "1 группы, выходы которых и вход первого разряда входа блока 7 контроля соединены соответственно с входами элемента ИЛИ 22, выход которого является выходом блока

7 контроля, входы разрядов с третьего по п-й входа которого соединены соответственно со. вторыми входами элемен( тов И 21 группы (и - разрядность кода) .

Инвертирующий денормализатор 3 предназначен для частичной развертки прямого I-кода Фибоначчи и выдачи инверсных (и-1) младших разрядов развернутого таким образом кода через первый блок 4 элементов И на входы (n-i) младших разрядов блока 5. Инвертирующий денормализатор 3 может быть реализован посредством группы из (n-1) элемента ИЛИ-НЕ.

Блок 5 приведения I-кодов Фибоначчи к минимальной форме предназначен для осуществления операции свертки

I-кодов. Блок 6 синхронизации предназначен для управления работой преобразователя. Блок 7 контроля предназначен для контроля кода в блоке 5 на минимальность формы, т.е. на отсутствие одновременно двух единиц в соседних разрядах или единицы в младшем разряде. Совместно с блоком 7 контроля блок 6 синхронизации определяет момент окончания сверток, а также формирует сигнал ошибки при ее возникновении во время хранения кода в блоке 5, Блок 8 элементов И предназначен для разрешения выдачи обратного кода, приведенного к минимальной форме, и прекращения его выдачи во время свертки или. при возникновении ошибки при хранении в блоке 5 свернутого кода.

Преобразователь работает следующим образом (фиг.1).

Исходный прямой I-код Фибоначчи с входа 1 поступает в инвертирующий денормализатор 3, где происходит частичная развертка исходного кода, т.е. каждая ециница в k-м разряде представляется двумя единицами в (k-1)"м и (k-. 2}-м разрядах, и инвертирование (и-1) разрядов -развернутого таким образом кода. Например: 10010000прямой код, 1101100 — развернутый код, 0010011 — проинвертированный развернутый код.

5 15805

С выхода инвертирующего денормализатора 3. преобразованный код через блок ч элементов И IIO сигналу на входе 9 поступает в (n-1) младших разрядов блока 5. Одновременно сигнал с входа 9 поступает в блок 6 синхронизации (фиг. 2) . При этом триггер 11 переводится в единичное состояние и на выходе 20 устанавливается нулевой сигнал, который поступает на вход блока 8 элементов И, запрещая тем самым выдачу кода из блока 5 на выход 2 преобразователя. С выхода блока 5 код поступает на вход блока 7 контроля. Последний (фиг.3) выдает единичный сигнал при наличии хотя бы двух единиц в соседних разрядах или единицы в младшем разряде. Если после поступления кода в блок 5 на вход 18 блока 6 20 синхронизации поступает единичный сигнал с выхода блока 7 контроля, что свидетельствует о необходимости сверток, то после снятия сигнала с входа

9 на выходе 19 блока 6 синхронизации 25 появляется единичный сигнал, который запускает в работу блок 5. При этом нулевой сигнал с выхода 20 продолжает поступать на вход блока 8 элементов И, запрещая выдачу кода на вы- 30 ход 2.

Запущенный в работу блок 5 производит операции свертки, т.е. приводит код к минимальной форме, напри— мер: 01100111 — — — 10001001 — — — 35

1000 t 010

После окончания переходных процессов на выходе блока 5 получают значение обратного I-кода, приведенного к минимальной форме. При этом gp на выходе блока 7 контроля устанавливается нулевой сигнал. Этот сигнал поступает на вход 18 блока 6 синхронизации, устанавливая нулевой сигнал на выходе 19, единичный сигнал на выходе 20, разрешая тем самым выдачу обратного кода на выход 2, и через элемент НЕ 13 единичный сигнал на нулевом установочном входе триггера 11.

После перехода триггера 11 в нулевое состояние снимается установочный сигнал с его нулевого установочного вхо- да, и блок 6 синхронизации переходит в режим контроля. При этом, если в результате ошибки на выходе блока 5 появляется запрещенная комбинация хранящегося обратного кода, единичный сигнал с выхода блока 7 контроля через элемент И 16 поступает на конт60 б рольный выход 10 преобразователя и на выходе 20 устанавливается нулевой сигнал, запрешающий выдачу кода через блок 8 элементов И на выход 2 преобразователя.

Если после преобразования в инвертирующем денормализаторе 3 прямого исходного кода полученный код сразу имеет минимальную форму, то после

era записи по сигналу на входе 9 в блок 5 на выходе блока 7 контроля действует нулевой сигнал, поэтому после снятия сигнала на входе 9 триггер 11 блока 6 синхронизации сразу переходит из единичного состояния в нулевое, не запуская тем самым в работу блок 5, и сразу разрешает выдачу обратного кода на выход 2 преобразователя.

Формула и з обретения

1. Преобразователь прямого I-кода

Фибоначчи в обратный I-код Фибоначчи, содержащий первый блок элементов И, блок приведения I-кодов Фибоначчи к минимальной форме и блок синхронизации, причем информационный вход и вход разрешения блока приведения I-кодов Фибоначчи к минимальной форме соединены с6ответственно с выходом перного блока элементов И и с первым выходом блока синхронизации, вход запуска которого соединен с входом запуска преобразователя, о т л и ч аю щ и и с я тем, что, с целью повышения быстродействия, он содержит инвертирующий денормализатор, блок контроля и второй блок элементов И, причем информационный вход преобразователя соединен с входом инвертирующего денормализатора, выход которого и вход запуска преобразователя соединены соответственно с первым и вторым входами первого блока элементов И, выход блока приведения I-кодов Фибоначчи к минимальной форме соединен с входом блока контроля и первым входом второго блока элементов И, второй вход и выход которого соединены соответственно с вторым выходом блока синхронизации и информационным выходом преобразователя, контрольный выход которого соединен с третьим выходом блока синхронизации, вход останова которого соединен с выходом блока контроля.

1580560

Составитель А.Клюев

Техред Л,Сердюкова Корректор И.Муска

Редактор И.Горная

Заказ.2023 . Тираж 659 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101 !

2. Преобразователь по и. 1, о т.л н ч а ю шийся тем, что инвертирующий денормализатор содержит группу элементов ИЛИ-НЕ; причем первый и второй входы, выход k-ro (k

=1-п-1, n — разрядность кода) элемента ИЛИ-НЕ группы являются соответственно входами (k+1)-ro и (k+2)"го разрядов входа и выходом k-ro разряда выхода инвертирующего денормалиэа- тора.