Устройство для оценки сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике. Цель изобретения - повышение достоверности оценки сигналов за счет уменьшения влияния помех. Устройство содержит преоразователь 1 частоты, преобразователь 2 код -частота, блок 3 регистров памяти кодов частот, делитель 4 импульсов, перемножители 5.1/ 5.2, интеграторы 6.1,6.2, генератор 7 опорных частот, фазовращатель 8, квадраторы 9.1,9.2, сумматор 10, стробирующий блок 11, нормирующий блок 12, пороговый блок 13, преобразователь 14, блок 15 сравнения , регистр 16 памяти, элемент И 17, генератор 18 счетной частоты, блок 16 регистров памяти фазовых кодов, блок 2 памяти кодов оптимальной структуры сигналов, элемент И 21, блок 22 памчти кодов оптимальной частоты. Введенная совокупность блоков позволяет за счет уменьшения влияния помехи повысить достоверность оценки сигналов. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСА БЛИН (51) 5 Н 04 В 17/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЦТИЯМ

ПРИ ГКНТ СССР

ОЛИСАНИЕ ИЗОБРЕТЕНИЯ, И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 . (61) 1363499 (21) 4465711/24-09 .(22) 25.07.88 (46) 23.07.90. Бюл. Р 27 (72) В.В.Федоренко и А.Г.Дубров (53) 621.396.664 (088..8) (56) Авторское свидетельство СССР

В 1363499, кл. Н 04 В 17/00, 1986. (54) УСТРОЙСТВО ДЛЯ ОЦЕНКИ СИГНАЛОВ (57) Изобретение относится к радиотехнике. Цель изобретения — повышение достоверности оценки сигналов за счет уменьшения влияния помех. Устройство содержит преобразователь 1 частоты, преобразователь 2 код — частота, блок.,SU„„1580576 А 2

3 регистров памяти кодов частот, делитель 4 импульсов, перемножители 5 ° 1, 5.2, интеграторы 6.1, 6.2, генератор 7 опорных частот, фазовращатель 8, квадраторы 9.1, 9.2, сумматор 1О, стробирующий блок 11, нормирующий блок 12, пороговый блок 13, преобразователь

14, блок 15 сравнения, регистр 16 памяти,- элемент И 17, генератор 18 счетной частоты, блок 16 регистров памяти фазовых кодов, блок 2 памяти кодов оптимальной структуры сигналов, элемент И 21, блок 22 памяти кодов оптимальной частоты. Введенная совокупность блоков позволяет за счет уменьшения влияния помехи повысить достоверность оценки сигналов. 1.ил.

1580576

Изобретение относится к радиотехнике и может использоваться для выбора сигналов, оптимальных к воздействию помех, и является усовершенствованием известного изобретения по авт, св. Ф 1363499.

Цель изобретения — повышение достоверности оценки сигналов за счет уменьшения влияния помех.

1О

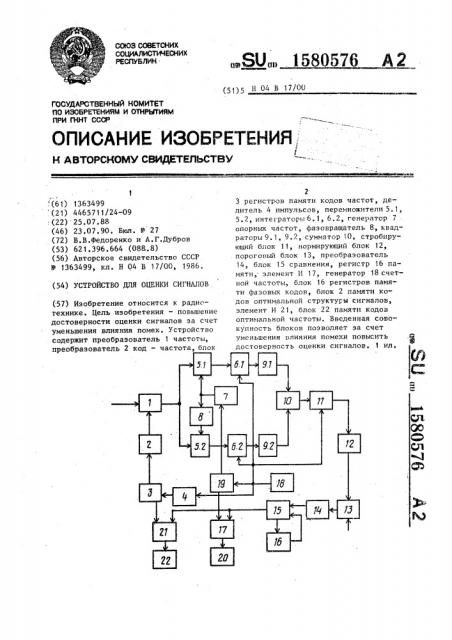

На чертеже представлена структурная электрическая схема предложенно1

I го устройства.

Устройство для оценки сигналов содержит преобразователь 1 частоты, преобразователь 2 код — час гота, блок 3 регистров памяти кодов частот, делитель 4 импульсов, первый и второй перемножители 5 ° 1, 5.2, первый и второй интеграторы 6.1, 6.2, генератор

7 опорных частот, фазовращатель 8, .первый и второй квадраторы 9.1, 9.2, сумматор 10, стробирующий блок 11, нормирующий блок 12, пороговый блок

13, преобразователь. 14, блок 15 срав- 25 нения, регистр 16 памяти, элемент И

17, генератор 18 счетной частоты, блок 19 регистров памяти фазовых кодов, блок 20 памяти кодов оптимальной структуры сигналов, второй элемент И 21, блок 22 памяти кода оптимальной частоты, Устройство работает следующим образом.

С выхода генератора 18 счетной частоты на вход блока 19 поступают тактовые импульсы с периодом Т для поочередного подключения регистров памяти фазовых кодов, определяющих структуру сигналов, H K генератору 7 40 опорных сигналов. Сигнал определенной структуры Z,(t) с выхода генератора

7 опорных сигналов поступает на второй вход одного из перемножителей

5.1, 5.2 и на вход фазовращателя 8, с выхода которого сигнал, сопряженный по Гильберту с опорным сигналом, поступает на второй вход перемножителя

5.2 . На первые входы первого и второго перемножителей 5.1 и 5.2 подается

5О помеха ZN(t) с,выхода преобразователя

1 частоты, поступающая на его вход с исследуемого (не показан) канала связи. На второй вход преобразователя

1 частоты с выхода преобразователя 2

55 код — частота подается гетеродинное напряжение с частотой, определяемой двоичным кодом на выходе блока 3 регистров памяти кодов частот.

Сигналы с выходов первого и второго перемножителей 5.1 и 5.2 поступают »а входы первого и второго интеграторов 6. 1 и 6.2 соответственно, где интегрируются на интервале длительности элемента опорного сигнала.

С выходов первого и второго интеграторов 6.1 и 6.2 сигналы поступают на входы первого и второго квадраторов

9.1 и 9.2, с выходов которых поступают на входы сумматора 10. Выход сумматора 10 соединен с входом стробирующего блока 11, в котором осуществля" ется отсчет результата в момент вре-, мени, кратный целому числу длительности элемента опорного сигнала, при поступлении на тактовый вход импульсов с выхода генератора 18 счетной частоты эти же импульсы поступают на тактовые входы первого и второго интеграторов 6.1 и 6.2 для сброса накопленного за период Т напряжения.

С выхода стробирующего блока 11 сигнал поступает на вход нормирующего блока 12, с выхода которого полученное значение коэффициента взаимного различия опорного сигнала и помехи q 1 (r E (1,2,...,I<), 1E(12,...L), где К вЂ” число анализируемых фазовых кодов, записанных в блоке 19 регистров памяти фазовых кодов; L — число значений гетеродинной частоты, определяемое количеством регистров в блоке 3), поступает в пороговый блок 13, где сравнивается с некоторым пороговым значением коэффициента q определяемым допустимым значением вероятности ошибки Po . С выхода порогового блока 13 напряжение U> 1, равное разности между пороговым значег г нием q и измеренным значением «11,1

Qop коэффициента взаимного различия U 1=

2 - 2

Р

=q -q 1 поступает на вход преобпор разователя 14, в котором происходит преобразование напряжения U<1 в двоичный код Х 1 поступающий затем на первый вход блока 15 сравнения, На второй вход блока 15 сравнения поступает информация с регистра 16 памяти о максим UIBHQM значении разности

q -q,1, i Е 1,2,. ° .,r-1 (соответ2 бар, ствующей минимальному значению q.l), I полученной при измерении коэффициента взаимного различия всех предыдущих r-1вариантов структур опорных сигналов при 1-й гетеродинной часто158057

Составитель Е. Голуб .

Техред Л. Сердюкова Корректор О. Ципле

Редактор С.Патрушева

Заказ 2023 Тираж 526 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035," Москва, Ж-35, Раушская наб., д. 4/5

Производственно-иэдательскчй комбинат "Патент", г.Ужгород, ул. Гагарина, 101 те либо всех К вариантов структур опорных сигналов при предыдущих

j 6 1,2, ° ° .,1"1 гетеродинных частотах и помехи. Если поступившее в блок

15 с выхода преобразователя 14 значение Х„1 превышает Х, 1, записанное в регистре 16 памяти, с выхода блока

15 в регистр 16 запишется новая информация Хь1, являющаяся максимальной для всех r структур опорных сигналов и 1 гетеродинных частот. При этом с первого выхода блока 15 сравнения на второй вход первого элемента И 17 и на первый вход второго элемента И 21 поступает сигнал, открывающий первый элемент И 17 для записи с блока 19 регистров памяти фазовых кодов в блок

20 памяти кодов оптимальной структу- 20 ры информацию об r-м коде структуры сигнала и второй элемент И 21 для записи с блока 3 регистров памяти кодов частот в блок 22 памяти кода оптимальной частоты информацию об 1-й гетеродинной частоте, при которых измеренное значение коэффициента взаимного различия q„l является наимень2, шим.

Если поступившее с преобразователя

14 в блок 15 сравнения значение разности не превышает значения Х,l, записанного в регистре 16 памяти, то сигналы на выходах блока 15 сравнения отсутствуют и в регистре 16 памяти и в блоках 20 и 22 остается прежняя, ранее записанная информация.

Таким образом, в блоке 20 записывается.информация о коде структуры 40 сигнала, оптимального к воздействию помехи в канале, а в блоке 22 — информация о номере (коде) гетеродинной частоты, при которой воздействие

6 6 помехи на сигнал данной структуры минимальное.

После поступления с генератора 18

R тактовых импульсов на вход делителя 4 импульсов на К, осуществляющем деление частоты следования импульсов на число анализируемых фазовых кодов, на его выходе формируется импульс, поступающий в блок 3 регистров памяти кодов частот. С выхода блока 3 в преобразователь 2 код— частота поступает информация в виде двоичного кода о значении очередной (1+1)-й гетеродинной частоты, обеспечивающей в преобразователе 1 сдвиг полосы пропускания радиотракта по частоте на значение Ь . После этого цикл измерения коэффицйента взаимного различия сигналов различной структуры, определяемой фазовыми кодами в блоке 19, и помехи, присутствующей в канале, повторяется.

Формула изобретения

Устройство для оценки сигналов по авт. св. Y - 1363499, о т л и ч а— ю щ е е с я тем, что, с целью повышения достоверности оценки сигналов за счет уменьшения влияния помехи, между выходом генератора счетной частоты и первыми входами первого и второго перемножителей введены последовательно соединенный делитель импульсов, блок регистров памяти кодов частот, преобразователь код — частота и преобразователь частоты, второй вход которого является входом устройства, кроме того введены последовательно соединенные второй элемент И, первый и второй входы которого соединены соответственно с выходом блока регистров памяти кодов частот и с выходом блока сравнения, и блок памяти кода оптимальной частоты.