Устройство автоматического поиска и контроля радиоканалов

Иллюстрации

Показать всеРеферат

Изобретение относится к технике радиосвязи. Цель изобретения - повышение точности. Устройство содержит управляемый антенный коммутатор 1, радиоприемник 2, блок 3 фильтров, коммутатор 4 фильтров, блок 5 измерения, блок 9 памяти, триггер 10, элемент И 11, таймер 12, запоминающий регистры 13,14, дешифраторы 15, 16, блок 17 перестройки частоты, элемент ИЛИ 18, адресный регистр 19, счетчики 20,21, формирователь 22 импульсов, сумматор 23 , блок 24 памяти, вычитающий блок 25, блок 26 деления, блок 27 памяти, коммутатор 28, счетчики 29,30, элементы И 31,32,33, элементы задержки 34,35,элемент ИЛИ 36, инвертор 37, блок 38 регистрации, элемент ИЛИ 39. Введенная последовательность блоков позволяет за счет анализа радиочастот (РЧ) увеличить точность поиска и контроля радиоканалов. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОВ 01) (51) 5 Н 04 J 1/16 // Н 04 В 3/46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ:

К A ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И О 1НРЫТИЯМ

rid ГКНТ СССР

1 (21) 4478362/24-09 (22) 23.08.88. (46) 23.07.90. Бюл. У 27 (72) А.А.Козлов, Б.С.Егоров и П.П.Рыжов (53) 621.396 ° 668(088.8) (56) Авторское свидетельство СССР

У 1443191, кл. Н 04 J 1/16 // Н 04

В 3/46, 1987. (54) УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА И КОНТРОЛЯ РАДИОКАНАЛОВ (57} Изобретение относится к технике радиосвязи. Цель изобретения - повышение точности. Устройство содержит управляемый антенный коммутатор 1, радиоприменик 2, блок 3 фильтров, 2 коммутатор 4 фильтров, блок 5 измерения, блок 9 памяти, триггер 10, элемент И 11, таймер 12, запоминающий регистры 13, 14, дешифраторы 15, 16, блок 17 перестройки частоты, элемент

ИЛИ 18, адресный регистр !9, счетчики 20, 21, формирователь 22 импульсов, сумматор 23, блок 24 памяти, вычитающий блок 25, блок 26 деления, блок 27 памяти, коммутатор 28, счетчики 29, 30, элементы И 31, 32, 33, элементы задержки 34, 35, элемент

ИЛИ 36, инвертор 37, блок 38 регистрации, элемент ИЛИ 39. Введенная последовательность блоков позволяет эа счет анализа радиачастот (РЧ} увеличить точность поиска и контроля радиоканалов. 1 ил.

1580578

Изобретение относится к технике радиосвязи и может использоваться на приемных центрах узлов связи для анализа состояния радиоканалов при групповом использовании всеми радионаправленияыи узла одних и тех же рабочих частот.

Цель изобретения - повышение точ,ности ° !

О

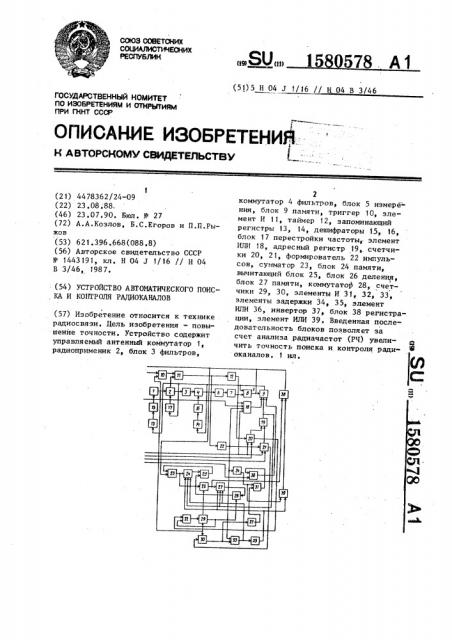

На чертеже представлена структур ная электрическая схема предложенного устройства.

Устройство автоматического поиска

I и контроля радиоканалов содержит уп равляемый антенный коммутатор 1, радиопнименик 2, блок 3 фильтров, коммутатор 4 фильтров, блок 5 измерения, состоящий из логарифмического усилителя 6, аналого-цифрового преобразова-20 теля 7 и решающего блока 8, первый блок 9 памяти, триггер 10, первый элемент И 11, таймер 12, первый и второй задоминающие регистры 13 и 14, первый и второй дешифраторы 15 и 16, 25 блок 17 перестройки частоты, первый элемент ИЛИ 1,8, адресный регистр 19, первый и второй счетчики 20 и 21, формирователь 22 импульсов, сумматор

23, второй блок 24 памяти, вычивающий блок 25, блок 26 деления, третий блок 27 памяти, коммутатор 28, третий и четвертый счетчики 29 и 30, второй, третий и четвертый элементы

И 31 — 33 первый и второй элементы

34 и 35 задержки, второй элемент

ИЛИ 36, инвертор 37, блок 38 регистрации, третий элемент ИЛИ 39.

Устройство работает следующим образом.

Перед началом работы в первый блок

9 памяти заносятся номиналы РЧ и, кроме того, для каждого радионаправления номера фильтров, обеспечивающих требуемую для каждого .радионаправления скорость передачи. Для этого код номинала частоты и код номера фильт. ра подаются на информационный вход первого блока 9 памяти по первому входу устройства, код адреса этой частоты и коды адресов радионаправлен-

50 ний записываются в первый и второй счетчики. 20 и. 21 по четвертому и пятому входам соответственно. После этого по второму входу устройства через второй элемент ИЛИ 36 подается сигнал на вход записи первого блока 9 памяти. При этом информация, поступаюшая по первому входу устройства, будет записана по соответствующим адресам первого блока 9 памяти, Для запуска устройства подают сигнал "Пуск" по третьему входу. При этом триггер 10 открывает первый элемент И 11, первый, второй, третий и четвертые счетчики 20, 21, 29, 30 приводятся в исходное состояние, при котором в первый счетчик 20 записывается код адреса первой радиочастоты (РЧ), а счетчики второй, третий и четвертый 21, 29, 30 обнуляются. Через первый элемент ИЛИ 18 "Пуск" поступает йа вход считывания первого блока 9 памяти и код первой РЧ поступает в блок 17, который настраивает на эту частоту радиоприемник (РПУ)

2. По окончании процесса перестройки с выхода радиоприемника 2 поступает сигнал готовности, который через открытый первый элемент И 11 запускает таймер 12 и формирователь 22 импульсов.

Формирователь 22 выдает серию импульсов, частота следования которых выбирается такой, чтобы за время анализа РЧ, формируемое таймером 12, антенна каждого радионаправления посредством управляемого антенного коммута тора 1 многократно подключалась к вхс ду радиоприемника 2. Эти импульсы с выхода формирователя 22 поступают на счетный вход второго счетчика 21 и через первый элемент ИЛИ 18 на вход считывания, а через первый элемент

34 задержки, второй элемент И 3 1 и второй элемент ИЛИ 36 — на вход записи первого блока 9 памяти, второй элемент И 3 1 открыт сигналом с выхода инвертора 37. Первым импульсом с выхода формирователя ?2 записывается единица во второй счетчик 21, что соответствует коду адреса первого радионаправления. Этот код с выхода второго счетчика 21 поступает на соответствующие разряды адресного регистра 19. При этом сигналом, поступающим с выхода формирователя 22 через первый элемент ИЛИ 18 на вход считывания первого блока 9 памяти, в первый и второй запоминающие регистры 13 и

14, заносятся код номера первого радионаправления и код фильтра, соответствующего скорости передачи этого радионаправления. При этом первый дешифратор 15 подключает посредством управляемого антенного коммутатора 1 к входу радиоприемника 2 антенну перво8 6 вертор 37 закрывает второй элемент

И 31. Поэтому при последнем за данное время анализа опросе антенн второй элемент И 31 закрыт. По входу записи в первый блок 9 памяти записывается код уровня помех. При этом решающий блок 8 определяет среднее (например, среднее квадратичное) значение уровней помех на данной РЧ для каждого радионаправления. С выхода решающего блока 8 эти значения уровней помех поступают в блок 38 регистрации и на вход сумматора 23. При этом с выхода четвертого элемента И 33 поступают импульсы на вход считывания второго блока 24 памяти, а через первый элемент 34 задержки и третий элемент

ИЛИ 39 на вход записи блока 38 регистрации. При этом в блоке 38 регистрации производится регистрация текущего уровня помех на первой РЧ для каждого радионаправления. Поскольку в исходном состоянии второй блок 24 памяти очищен, а коммутатор 28 закрыт сигналом с выхода последнего разряда счетчика 29, то на второй вход сумматора 23 с выхода вычитающего блока 25 ничего не поступает . Поэтому во второй блок 24 памяти при поступлении на его вход записи импульсов из формирователя 22 через четвертый элемент. И 33 и второй элемент 35 задержки записываются средние-за время анализа уровни помех на данной РЧ для каждого радионаправления.

После окончания времени анализа импульсом с выхода таймера 12 будет записываться единица в первый счетчик 20. При этом первый счетчик 20 формирует код адреса второй РЧ, который поступает на соответствующие входы адресного регистра 19. Через первый элемент ИЛИ 18 этот импульс поступает на вход считывания первого блока 9 памяти и код второй РЧ выдается в блок 17. После этого все описанное повторяется на второй РЧ, а так до тех пор пока не завершится анализ всех РЧ.

После анализа последней РЧ импуль-. сом с выхода таймера 12 переполняется первый счетчик 20 и с сигналом с выхода его последнего разряда записывается единица в третий счетчик

55—

29 через третий элемент И 32, которьф открывается сигналом, поступающим с выхода последнего разряда третьего счетчика 29 при установке последнего

5 158057 го радианаправления, а второй дешифратор 16 посредством коммутатора 4 фильтров подключает выход соответствующего фильтра к входу блока 5 измерения.

Сигнал помехи, принимаемый с первоЬ го радионаправления, с выхода радиоприемника 2, через блок 3 фильтров и коммутатор 4 поступает в блок 5 измерения и на вход логарифмического усилителя 6 и через анолого-цифровой преобразователь (АЦП) 7 на вход решающего блока 8, где суммируется с кодом уровня помех первого радионап15 равления, поступающим на второй вход решающего блока 8 с выхода первого блока 9 памяти под воздействием импульса, поступающего на вход считывания этого первого блока 9 из формирователя 22 через первый элемент ИЛИ 18.

Поскольку в исходном состоянии в первом блоке 9 памяти отсутствует информация об уровне помех, то при первом опросе антенн информация на выходе решающего блока 8 будет равна информации на выходе АЦП 7. Импульсом с выхода формирователя 22, поступающим через первый элемент 34 задержки, второй элемент И 31 и второй элемент

ИЛИ 36 на вход записи первого блока 9 памяти, код величины уровня помех на первый РЧ, для первого радианаправления будет записан по соответствующему адресу первого блока 9 памяти, Вторым импульсом с выхода формирователя

22 к входу радиоприемника 2 подключается антенна второго радионаправления, а к входу блока 5 измерения — выход блока 3 фильтров, соответствующего

40 скорости передачи этого радионаправления, и описанный процесс повторяется.

После окончания опроса антенн всех радионаправлений переполняется и сбра- 45 сывается в исходное состояние второй счетчик 21, и с его выхода записывается единица в четвертый счетчик 30, к входу радиоприемника 2 снова подключается антенна первого радионаправления и весь цикл измерений повторяется, и так до тех пор пока не закончится время анализа, формируемое таймером 12.

По окончании предпоследнего за вре. мя анализа опроса антенн заполняется четвертый счетчик 30, и сигналом с выхода его последнего разряда открывается четвертый элемент И 33,,а ин1580578 в исходное состояние командой "Пуск".

Третий счетчик 29 подсчитывает число циклов анализа РЧ. за время прогноза и тем самым задает это время. При пе5 реполнении первый счетчик 20 сбрасы" вается в исходное состояние, а адресный регистр 19 снова записывается код адреса первой РЧ, и цикл анализа рабочих частот повторяется. 10

При втором и последующих циклах анализа РЧ в сумматоре 23 складываются текущее значения уровней помех ! на РЧ для каждого радионаправления и записанные во втором блоке 24 памяти, 15 так как на второй вход вычитающего блока 25 через закрытый коммутатор 28 ничего не поступает. Таким образом, во втором блоке 24 памяти накапливаВ ются суммарные за время прогноза зна- 20 чения уровней помех на РЧ для всех радионаправлений. Кроме того, суммарные значения уровней помех с выхода сумматора 23 поступают»а блок 2б деления, где делятся на число циклов 25 измерений, записанное в тертий счетчик 29. С выхода блока 26 деления средние за время прогноза значения уровней помех на РЧ для каждого радионаправления заносятся в третий блок

27 памяти, с выхода которого прогнозируемое значения уровней помех в конце каждого цикла анализа РЧ выдают в блок 38 регистрации.

При заполнении третьего счетчика

29 сигналом с выхода его последнего разряда закрывается третий элемент

И 32 и открывается коммутатор 28, После этого третий счетчик 29 сохраняет свое состояние на все последующее время работы. Начиная с этого момента, при каждом последующем заполпении четвертого счетчика 30 .на входы вычитающего блока ?5 поступают с выходов второго и третьего блоков 24 и 27 45 памяти соответственно суммарное за время прогноза значение уровней помех на анализируемой РЧ и среднее за время прогноза значения уровней помех на этой РЧ для каждого радионаправления. Зто происходит под воздействием импульсов, поступающих на входы считывания второго и третьего блоков

24 и 27 памяти с выхода формирователя 22 через четвертый элемент И 33.

Разность между суммарным и средним за время прогноза значениями уровней помех на анализируемой РЧ складывает.,ся в сумматоре 23,с текущим значением уровней помех на этой РЧ за очередное время анализа..С выхода сумматора

23 результат сложения поступает на вход второго блока 24 памяти и на блок 2б деления, где делится на число циклов анализа за время прогноза, поступающее из третьего счетчика 29.

Под воздействием импульсов, поступающих из формирователя 22 через четвертый элемент И 33 и второй элемент задержки 35 на входы записи второго и третьего блоков 24 и 27..памяти, в них заносятся соответственно новые значения суммарного за время прогноза и программируемого значений уровня помех для каждого радионаправления.

Кроме того, прогнозируемое значение уровней помех для каждого радионаправления регистрируется в блоке 38 регистрации под воздействием импульсов, поступающих на вход записи с выхода второго элемента 35 зацержки через третий элемент ИПИ 39. В итоге каждый раз по истечении времени анализа

РЧ, задаваемого таймером 12, в блоке

38 регитсрации фиксируется текущее и прогнозируемое значения уровней помех на этой РЧ для каждого радионаправления.

Для выключения устройства подается команда Стоп" на второй вход триггера 10, при этом закрывается первый элемент И 11, и сигналы на запуск таймера 12 и формирователя 22 импульсов не проходят.

Формула изобретения Устройство автоматического поиска и контроля радиоканалов, содержащее первый и второй элементы ИЛИ, первый и второй счетчики, последовательно соединенные управляемый антенный коммутатор и радиоприемник, последовательно соединенные блок измерения и первый блок памяти, адресный регистр, последовательно соединенные триггер, первый элемент И, второй вход которо го соединен с выходом сигнала готовности радиоприемника, и таймер, выход которого подключен к первому входу первого элемента ИЛИ и к счетному входу первого счетчика, выход которого подключен к первому входу адресно-!

ro регистра, выход которого соединен! с адресным входом первого блока памяти, формирователь импульсов, вход которого соединен с выходом первого

1580578 элемента И„а выход подключен к второму входу первого элемента ИЛИ, выход которого подключен к входу считывания первого блока памяти, и счетному входу второго счетчика, блок перестройки частоты, вход которого соединен с выходом первого блока памяти, а выход подключен к управляющему входу радиоприемника, первый элемент задержки, вход которого соединен с выходом формирователя импульсов, а выход подключен к первому входу второго элемента ИЛИ, выход которого соединен с входом записи первого 15 блока памяти, первый вход которого является первым входом устройства, вторым входом которого является второй вход второго элемента ИЛИ, входы сброса триггера, первого и второго счетчиков и третий вход первого элемента ИЛИ объединены и являются третьим входом устройства, четвертым и пятым входами которого являются установочные входы соответственно первого 25 и второго счетчиков, четвертый вход первого элемента ИЛИ является соответственно шестым входом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения точности, введены вто-ЗО рой элемент И, первый вход и выход которого соединены соответственно с выходом первого элемента задержки и первым входом второго элемента ИЛИ, последовательно соединенные сумматор, первый вход которого соединен с первым входом первого блока памяти, вто1 рой блок памяти, второй вход которого соединен с выходом адресного регистра и вычитающий блок,,выход которо- 4О

ro подключен к второму. входу сумматора, последовательно соединенные блок деления, первый вход которого соединен с выходом сумматора, третий блок памяти, второй вход которого соеди- 4 нен с выходом адресного регистра и коммутатор, выход которого подключен к второму входу вычитающего блока, последовательно соединенные третий элемент И, первый вход которого соеди"" 5О нен с выходом первого счетчика, и третий счетчик, первый выход которого подключен к второму входу блока деления, а второй выход третьего.счетчика соединен с вторым входом коммутатора и с вторым входом третьего элемента И, последовательного соединенные четвертый счетчик, первый вход которого соединен с выходом второго счетчика, четвертый элемент И, второй вход которого соединен с выходом формирователя импульсов, второй элемент задержки, третий элемент ИЛИ, I второй вход которого соединен с выходом первого элемента задержки, и блок регистрации, второй и третий входы которого соединены соответственно с выходом блока деления и первым входом первого блока памяти, инвертор, вход и выход которого соединен соответственно с выходом четвертого счетчика, вторым входом второго элемента И, выход четвертого элемента И соединен с третьими входами второго и третьего блоков памяти, четвертые входы которых соединены с выхо- дом второго элемента задержки, входы сброса третьего и четвертого счетчиКоВ соединены с входами первого и второго счетчиков, последовательно соединенные блок фильтров, вход которого соединен с выходом радиоприемника, и коммутатор фильтров, выход которого подключен к входу блока измерений, управляющий вход которого соединен с выходом первого блока памяти, последовательно соединенные первый запоминающий регистр, вход которого соединен с выходом первого блока памяти, и первый дешифратор, выход которого подключен к управляющему входу управляемого антенного коммутатора, последовательно соединенные второй запоминающий регистр, вход которого соединен с выходом первого блока памяти, и второй дешифратор, выход которого подключен к управляющему входу коммутатора фильтров, выход второго счетчика соединен с вторым входом адресного регистра, второй вход триггера является седьмым входом устройства.