Преобразователь телевизионного стандарта

Иллюстрации

Показать всеРеферат

Изобретение относится к технике средств связи. Цель изобретения - повышение точности преобразования при несовпадающих напрвлениях развертки изображений входного и выходного стандартов. Преобразователь телевизионного стандарта содержит АЦП 1, регистры 2,3,17,18 и 22, блоки 4,19 и 24 памяти, коммутаторы 5,16 и 21 , счетчики 6-8 импульсов, D-триггеры 9,11 и 14, эл-ты И 10 и 13, блок 12 управления, блок 15 предустановки, ЦАП 20 и формирователь 23 управляющих импульсов. В предлагаемом преобразователе асинхронное сопряжение по тактовым и кадровым частотам и циклический режим работы блока 4, 19 и 24 памяти, при котором не производится запись видеоинформации в блок, из которого считывается информация. Такой режим исключает возможность появления искажений типа смаза для любых направлений развертки изображений входного и выходного стандартов. Преобразователь по пп. 2 и 3 ф-лы отличается выполнением блока управления 12 и формирователя 23. 2 з.п.ф-лы, 6 ил.

СОЮЗ С(.ЕЕТСКИХ

РЕСПУБЛИК (292 (222 щ) Н 04 Ж 7/01

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

Н А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (21) 4484832/24-09 (22) 19.09,88 (46) 23.07.90. Бюл. № 27 (72) С.А.Куликов и В.Г.Вариади (53) 621.397.3 (088.8) (56) Авторское свидетельство СССР

¹ 1418927, кл. Н 04 N 7/01, 1987. (54) ПРЕОБРАЗОВАТЕЛЬ ТЕЛЕВИЗИОННОГО

СТАНДАРТА (57) Изобретение относится к технике средств связй. Цель изобретения — повьпиение точности преобразования при несовпадающих направлениях развертки изображений входного и выходного стандартов. Преобразователь телевизионного стандарта содержит АЦП 2, регистры 2,3, 17,18 и 22, блоки 4,19 и 24 памяти, коммутаторы 5,16 и 21, 2 счетчики 6-8 импульсов, D-триггеры

9,11 и 1 4, эл-ты И 10 и 13, блок 12 управления, блок 15 предустановки, ЦАП 20 и формирователь 23 управляющих импульсов. В предлагаемом преобразователе. асинхронное сопряжение по тактовым и кадровым частотам и циклический режим работы блока 4, 19 и 24 памяти, при котором не производится запись видеоинформации в блок, из которого считывается информация ° Такой режим исключает воэможность появления искажений типа смаэа для любых направлений развертки иэображений входного и выходного стандартов. Преобразователь по пп.2 и 3 ф-лы отличается выполнением блока управления 12 и формирователя 23. 2 з.п. ф-лы, 6 ил.

1580589

Изобретение относится к промышленности средств связи и может быть ис- .

: пользовано при построении устройств . сопряжения малокадровых телевизионных систем с телевизионными система"

5 ми,работающими в вещательном стандарте.

Цель изобретения — повышение точности преобразования при несовпадающих направлениях развертки нзображений входного и выходного стандартов.

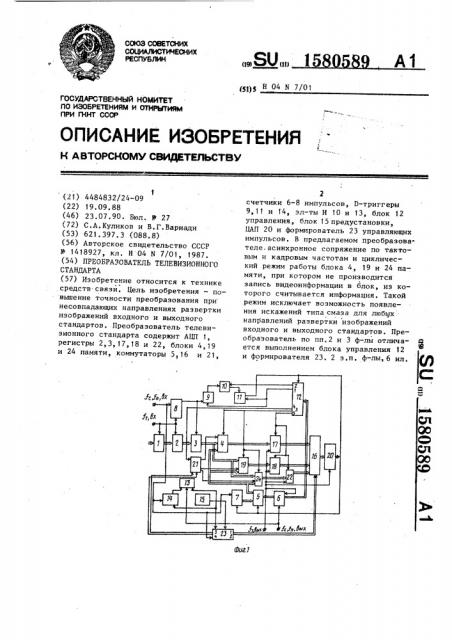

На фиг. 1 представлена электричес кая структурная схема преобразова теля телевизионного стандарта; на фиг.2 — схема блока управления; на

;фиг.3 — схема формирователя управляющих импульсов; на фиг.4-6 временные диаграммы, поясняющие работу преоб1 разователя.

Преобразователь телевизионного стандарта содержит аналого-цифровой преобразователь (АЦП) 1, первый 2 и второй. 3 регистры, первый блок 4 памяти, второй коммутатор 5, первый 25

6, второй 7.и третий 8 счетчики импульсов, первый 0-триггер 9, первый элемент И 10, второй D-триггер 11, блок 12 управления, второй элемент

И 13, третий B-триггер 14, блок 15-предустановки, первый коммутатор 16, третий 17 и четвертый 18 регистры, второй блок 19 памяти,цифро-аналоговый преобразователь (ЦАП) 20, третий коммутатор 21, пятый регистр 22, формирователь 23 управляющих импуль ..

35 сов и третий блок 24 памяти.

Блок 12 управления (фиг. 2), содержит дешифратор 25, первый элемент

И 26, элемент ИЛИ 27, первый 28, второй 29 и третий 30 RS-триггеры и второй элемент. И 31 °

Формирователь 23 управляющих импульсов (фиг,3) содержит первый 32 и второй 33 счетчики импульсов и первый 34 и второй 35 элементы И, Преобразователь телевизионного стандарта работает следующим образом.

Аналоговый видеосигнал поступает на вход АЦП 1, где преобразуется в восьми-разрядный параллельный цифровой код. С выхода АЦП 1 цифровой код поступает на вход первого регистра 2, запоминающего 16 элементов входной развертки. Синхроимпульсы строк входной развертки поступают

55 на вход установки 15-разрядного второго счетчика 7, генерирующего адреса записи, и на вход сброса третьего счетчика 8. Последний подсчитывает

16 периодов тактовой частоты {фиг.4а) входной реэвертки и формирует последовательность импульсов с частотой в 16 раз более низкой, чем частота элементов входной развертки. Положительными фронтами этих импульсов осуществляется перезапись 16 элементов из первого регистра 2 во второй регистр 3. Таким образом осуществляется распараллеливание входной информации, т.е. каждый элемент изображения входной развертки будет присутствовать на информационном входе блока памяти в течение времени, равного 16 периодам тактовой частоты входной развертки.

Синхроимпульсы строк, опережающие начало активной частоты выходной развертки, поступают от синхрогенератора выходной развертки на вход установки первого, счетчика 6, генерирующего адреса считывания.

Синхроимпульсы строк устанавливают первые десять разрядов первого счетчика б, а синхроимпульсы кадров выходной развертки устанавливают остальные его пять разрядов. Первые четы-ре разряда первого счетчика 6 подключены к групповому. входу блока 12 управления, формирующего сигналы управления работой преобразователя телевизионного стандарта, синхронные с частотой выходной развертки.

По сигналу с распараллеливающего третьего счетчика 8 производится запись 16 элементов во второй регистр 3 и логической "1" в первый D-триггер

9 (фиг.4и), сигнал логической "1" с выхода которого поступает на первый вход первого элемента И 10 и разрешает прохождение на выход последовательности импульсов (фиг.4д), пос-. тупающих с выхода блока 12 управления и определяющих начало циклов записи. С выхода первого элемента И 10 эти импульсы поступают на синхровход второго D-триггера и по фронту первого импульса производится запись логической "1". Сигнал логической "1" с выхода второго D-триггера 11 поступает.на вход блока 12 управления, где разрешает прохождение на выход последовательности импульсов (фиг.4л), определяющих конец цикла .записи. Эти импульсы поступают на входы сброса первого 9 и второго 11

D-триггеров. Таким образом, на выходе

80589

50 второго D-триггера 11 формируется сигнал, разрешающий прохождение импульса записи, формируемого блоком

12 управления, на третий выход и далее на вход третьего коммутатора 21..

Кроме того, этот же сигнал поступает на вход первого коммутатора 5, обеспечивающего подключение к адресным входам блоков 4, 19 и 24 памяти адресных кодов записи или считывания и на синхровход второго счетчика 7, генерирующего адресные коды записи.

Таким образом осуществляется запись информации несинхронного источника в момент времени, определяемый ближайшим циклом записи к моменту поступления информации на блоки памяти (фиг.4п).

Для обеспечения адресации в блоке

12 управления формируется сигнал выборки кристалла (фиг.4б), который поступает на выход блока 12 памяти управления и далее на вход блоков 4, 19 и 24 памяти.

Считанная иэ блокон 4, 19 и 24 памяти информация поступает на вход последовательно-параллельных третьего 17, четвертого 18 и пятого 22 регистров, сворачивающих параллельный цифровой поток в последовательный.

В результате этого частота элементов на выходе этих регистров в 16 раз выше частоты на входе.

Импульсы записи информации, поступающей с выходов блоков 4, 19 и 22 памяти в третий 17, четвертый 18 и пятый 22 регистры, формируются блоком 12 управления (фиг.4г) и с его выхода поступают на вход записи регистров 17, 18 и 22., На их синхровходы подается тактовая частота элементов выходной развертки. С выходов регистрон 17,. 18.и 22 восьмиразрядные параллельные, цифровые потоки поступают на первый, второй и третий групповые входы второго коммутатора 16. С выхода коммутатора 16 цифровой видеосигнал- в вещательном стандарте поступает на Ц>П 20, где преобразуется в аналоговую форму.

: Сигнал управления первым 16 и третьим 21 коммутаторами формируется формирователем 23. Входными сигналами формирователя 23 являются кадровые синхроимпульсы входного стандарта (фиг.4а), импульс с выхода блока 15 ,предустановки (фиг.4б) и сигнал с выхода устройства асинхронного сопряжения по кадровым частотам (фиг.4в), состоящего иэ третьего триггера t4 и второго элемента И 13. По переднему фронту кадровых синхроимпульсов (фиг.5а), поступающих на синхровход четвертого 0-триггера 14, осуществляется запись логической "1" (фиг.

5б). Уровень логической "1" с выхода третьего D-триггера 14 подается на первый вход второго элемента И 13, разрешая прохождение кадровых синхроимпульсов выходной развертки (фиг.5б) через другой вход второго элемента И 13 на первый вход формирователя 23 и на вход сброса третьего D-триггера 14 снимая тем самым разрешение прохождения кадровых синхроимпульсов выходной резвертки на первый вход формирователя 23 (фиг.5в).

Формирователь 23 (фиг.3) работает следующим образом. В момент включения преобразователь стандартов предустанавливается в исходное состояние импульсом предустановки, который По ступает на вход формирователя с выхода блока 15 предустановки (фиг.бб).

Импульс предустановки устанавливает двоичные двухразрядные счетчики 32 и 33 в состояние 2(1.0) и 0(0.0) соответственно. Счетчик 32 подсчитывает импульсы (фиг.бн), поступающие с блока сопряжения по кадровым частотам на первых вход блока управления. Кадровые телевизионные синхроимпульсы, поступающие с выхода устройства асинхронного сопряжения по кадроным частотам, определяют момент переключения блоков памяти по считыванию. Двухразрядный код с выхода счетчика 32 поступает на вход управления коммутатора 16, который поочередно подключает к ЦАП 20 один из информирующих групповых выходов блоков 4, 19 и 24 памяти по циклическому закону: 3 - 1 - 2 - 3. Элемент

И 34 выполняет функцию дешифратора.

При возникновении на входе запрещен-. ного состояния 3(11) элемент И 34 формирует сигнал сброса счетчика в состояние "0" (0.0) . Этим обеспечивается работа двухразрядного счетчика 32 по модулю три. Счетчик 33 подсчитывает кадровые синхроимпульсы входного стандарта (фиг.6а), поступающие на вход преобразователя стандартон. Эти импульсы определяют момент переключения блоков памяти по

1580589 записи. Двухраэрядный код с выхода счетчика 33 поступает на управляющие входы коммутатора 21, который поочередно подключает групповой вы5 ход параллельного регистра 3 к информационным входам блоков 4, 19 и

24 памяти по циклическому закону:

1 - 2 3 - 1. Элемент И 35 функционирует аналогично элементу И 34.

Такая реализация работы формирователя 23 позволяет избежать искажений в результате преобразования движущихся иэображений при произвольном направлении развертки входного стан- 15 дарта.

Блок 12 управления (фиг.2) работает следующим образом. На вход блока

12 управления поступает четырехразрядный цифровой код из первого 20 счетчика 6. Этот код представляет собой четыре младших двоичных раз,.- Ряда 15-разрядного первого счетчика 6,.десять младших разрядов которого сбрасываются в нулевое состояние 25 строчным синхроимпульсом. Три младшие кодовые последовательности поступают на вход дешифратора.25, а четвертый старший разряд (фиг.4и) на вторые входы первого 26 и второго 30

31 элементов И. Дешифратор 25 представляет собой устройство, которое формирует на одном иа шести входов уровень. логического "0" в зависимости от двоичного кода на входе (фиг.

4д,е,ж,з,и,к). Эти импульсы формируются на выходе дешифратора 25 с длительностью в один такт и с периодом в восемь тактов частоты элементов в выходной развертке. Импульсы с 40 третьего выхода дешифратора 25 периодически обнуляют третий RS-триггер

30, а импульсы с пятого выхода устанавливают его в единичное состояние.

В результате этого на выходе третьего 45

RS-триггера 30 формируется периодический сигнал (фиг.4б), который поступает на выход блока 12 управления и представляет собой сигнал выборки . кристалла блоков 4,19 и 24.памяти.

Аналогичным образом на выходе второ"

ro RS-триггера 29 формируется периодический сигнал (фиг.4в), поступающий на первый вход второго элемента И 31.

Этот .сигнал предназначен для включения блоков 4, 19 и 24 памяти преобразователя телевизионного стандарта в ре,жим записи. На второй вход второго элемента И 31 поступает четвертый разряд (фиг.4и), .уровень логического

"0" которого соответствует во времени циклу записи, а уровень логической

"1" — циклу считывания. На третий вход второго элемента И 31 поступает сигнал с входа блока 12 управления

1 (фиг.4в), который формируется вторым

D-триггером 11. В результате на выходе второго элемента И 31 формируется импульс записи (фиг.4п), соответст- . вующий ближайшему циклу записи к моменту поступления информации на вход блоков 4,19 и 24 памяти. Аналогично на выходе первого RS-триггера 28 формируется последовательность импульсов (фиг..4г), которая поступает на вход первого элемента И 26, формируется последовательность импульсов (фиг.4р), которая поступает на выход блока 12 управления и обеспечивает запись информации из них в ге- риод цикла считывания в регистры 17, 18 и 22. На вход элемента ИЛИ 27 поступает последовательность импульсов (фиг.4к), а на другой era вход— сигнал.с второго D-òðèããeðà 11. EIa выходе элемента ИЛИ 27 формируется последовательность импульсов (фиг.4л), которая поступает на выход блока 12 управления и служит для сброса первого 9 и второго 11 D-триггеров в нулевое состояние, что приводит к формированию на них входных сигналов (фиг.4н,о) соответственно.

В предлагаемом преобразователе реализовано асинхронное сопряжение по тактовым и кадровым частотам (общее с известным преобразователем) и циклический режим работы блоков памяти, при котором не производится запись видеоинформации в блок, из которого считывается информация.

Такой режим исключает возможность появления искажений типа смаэа пля любых;направлений. развертки изображений входного и выходного стандартов.

Формула и з о б р е т е н и я

1. Преобразователь телевизионного стандарта, содержащий последовательно соединенные аналого-цифровой преобразователь (АЦП), сигнальный. вход которого является сигнальным входом преобразователя телевизионного (ТВ) стандарта, первый регистр, второй регистр, первый блок памяти,„ третий

9 15805 регистр, первый коммутатор и цифроаналоговый преобразователь (ЦАП), выход которого является выходом преобразователя телевизионного стандарта, последовательно соединенные первый счетчик импульсов и второй коммутатор, к другому входу которого подключен выход второго счетчика, а выход соединен с адресными входами первого блока памяти и второго

1О блока памяти, выход которого через четвертый регистр объединен с вторым сигнальным входом первого коммутатора, последовательно соединенные

15 третий счетчик, тактовый вход которого соединен с тактовыми входами АЦП и первого регистра и является тактовым входом стандарта преобразователя

ТВ стандарта, первый D-триггер, первый элемент И, второй D-триггер и

20 блок управления, к другому входу которого подключен выход первого счетчика, тактовый вход которого соединен с управляющими входами ЦАП, третьего и четвертого регистров и является входом тактовых импульсов выходного стандарта преобразователя ТВ стандарта, последовательно соединенные третий D-триггер, первый вход которого соединен с входами сброса второго и третьего счетчиков и является входом строчных синхроимпульсов входного стандарта преобразователя ТВ стандарта, и второй элемент И, выход которого соединен с 35 вторым входом третьего D-триггера, при этом второй вход второго элемента И соединен с входом сброса перво:го счетчика и является входом строч1 ного и кадровых синхроимпульсов вы- 40 ходного стандарта преобразователя

ТВ стандарта с первого по пятый выходы блока управления соединены соответственно с вторым входом первого элемента И, с объединенными вторыми входами первого и второго

D-триггеров, первым входом третьего коммутатора, объединенными управляющими входами первого и второго блоков памяти и объединенными дополнительными управляющими входами третьего и четвертого регистров, объединенные установочный вход вт6рого счетчика и управляющий вход второго коммутатора соединены 55 с первым входом блока управления, сигнальный вход второго блока памяти соединен с выходом второго ре89 гистра, к второму входу которого подключен выход третьего счетчика, первый и второй выходы третьего коммутатора соединены соответственно с вторыми управляющими входами первого и второго блоков памяти, о т л и— ч а ю шийся тем„ что, с целью повышения точности преобразования пои несовпадающих направлениях развертки и иэображений входного и выходного стандартов, введены последовательно соединенные третий блок памяти и пятый регистр, выход которого соединен с третьим сигнальным входом первого коммутатора, и последовательно соединенные блок предустановки и формирователь, управляющих импульсов, первый и второй выходы которого соединены с первым и вторым управляющим входами первого коммутатора, третий и четвертый выходы соединены с вторым и. третьим входами третьего коммутатора, третий выход которого соединен с первым управляющим входом третьего блока памяти, второй управляющий вход, сигнальный вход и адресный вход которого соединены соответственно с четвертым выходом блока управления, выходами второго регистра и второго коммутатора, прн этом к первому и второму управляющему входам пятого регистра подключен соответственно пятый выход блока управления и первый управляющий вход четвертого регистра, а к второму и третьему входам формирователя управляющих импульсов подключены соответственно выход второго элемента И и первый вход третьего D-триггера.

2. Преобразователь по п.1, о тл и ч а ю шийся тем, что блок управления содержит дешифратор, трн RS-триггера, два элемента И и элемент ИЛИ, первый вход которого является первым входом блока управления, вторым входом которого является вход дешифратора, первый выход которого является первым выходом блока управления, а второй — шестой выходы дешифратора соединенны соответственно с R-входом второго Rs-триггера, R-входом третьего RS-триггера, S-входом первого RS-триггера, с объединенными S-входами второго,и третьего

RS-триггеров и объединенными R-входом первого RS-триггера и вторым

1580589!

2 входом элемента ИЛИ, выход которого является вторым выходом блока ygравления, при этом выход третьего

RS-триггера является четвертым

5 выходом блока управления выход

4 второго RS-триггера соединен с первым входом второго элемента И, второй вход которого объединен с первым входом первого элемента И и соединен с первым входом блока управления,а третий вход объединен с первым входом элемента ИЛИ, выход первого RS-триггера соединен с вторым входом первого элемента И, выход которого являетz5 ся пятым выходом блока управления, третий выход которого является выходом второго элемента И.

3. Преобразователь цо п.1, о т— л и ч а ю шийся тем, что форми- {) рователь, управляющих импульсов содержит два счетчика импульсов и два элемента И, причем объединенные V-входы первого и второго счетчиков являются первым входом формирователя управляющих импульсов, второй и третий входы которого являются соответственно С-входами первого и второго счетчиков импульсов, первый и второй выходы первого счетчика импульсов соединены с соответствующими входами первого элемента И, выход которого соединен с R-входом первого счетчика импульсов, первый и второй выходы которого являются первым и вторым выходами формирователя управляющих импульсов, первый и второй выходы второго счетчика импульсов соединены соответственно с первым и вторым входами второго элемента И, выход которого является

R-входом второго счетчика импульсов, выходы которого являются третьим и четвертым выходами формирователя управляющих импульсов.

158058 а б

Фиг. Ф

1580589

1 !

I б

1

1!

t

Составитель И.Грацианская

Редактор А.Козориз Техред М.Ходанич Корректор Т Малец

Подписное

Тираж 533

Заказ 2024

ВНИИПИ Государственного комитета по изобретениям и открытиям прн ГКНТ СССР

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-издательский комбинат "Патент", г ° Ужгород, ул. Гагарина, 101