Устройство для защиты транзисторов от перенапряжений

Иллюстрации

Показать всеРеферат

Изобретение относится к микроэлектронике. Цель - повышение надежности защиты при улучшении воспроизводимости порога срабатывания устройства. Поставленная цель достигается благодаря тому, что при повышении питающего напряжения выше допустимого коэффициент лавинного размножения носителей транзисторного датчика 6 увеличивается и достигает значения, при котором произведение его с коэффициентом передачи тока в схеме с общей базой достигает значения единицы. Дальнейшее повышение напряжения приводит к быстрому нарастанию тока и повышению напряжения на первом 8 и втором 10 резисторах и открыванию шунтирующего 7 и исполнительного 9 транзисторов. Исполнительный транзистор 9 шунтирует базовую цепь защищаемого транзистора, а шунтирующий транзистор 7 ограничивает ток через транзисторный датчик 6. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (19) (11) (g1)g H 02 H 7/10

А1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОсудАРстВенный кОмитет

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

flPH ГКНТ СССР

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (21) 4475560/24-07 (22) 21.06.88 . (46) ЗО.О7.90. Бюл. V 28 (71) Институт. физики полупроводников

АН ЛитССР (72) В.Ю, Юодвалькис, Д.В. Баранаускас и В.В. Иванов (53) 621,316.925.4(088.8) (56) IEEE Transuctions on Consummer

Electronics. Vol.. СЕ-.26. February

1980, с. 64, рис. 15.

ЕЕЕЕ Jornal of. Solid-State circuits. Vol se-22, N01, February, 1987, с. 87, рис. 8. (54) УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ТРАНЗИСТОРОВ ОТ ПЕРЕНАПРЯЖЕНИИ . (57) Изобретение относится к микроэлектронике. Цель - повышение надежности защиты при улучшении воспроиз2 водимости порога срабатывания устройства. Поставленная цель достигается благодаря тому, что при повышении питающего напряжения выше допустимого коэффициент лавинного размножения носителей транзисторного датчика 6 увеличивается и достигает значения, при котором произведение его с коэффициентом передачи тока в схеме с общей базой достигает значения единицы. Дальнейшее повышение напряжения приводит к быстрому нарастанию тока и повышению напряжения на первом 8 и втором 10 резисторах и открыванию шунтирующего 7 и исполнительного 9 транзисторов. Исполнительный транзистор 9 шунтирует базовую цепь защищаемого транзистора, а шунтирующий транзистор 7 ограничивает ток через транзисторный датчик 6. 1 ил.

1582264

Изобретение относится к микроэлектронике и может быть применено для. защиты транзисторов и интеграль- . ных схем от перенапряжений.

Целью изобретений является повышение надежности защиты при улучшении воспроизводимости порога срабатывания устройства .

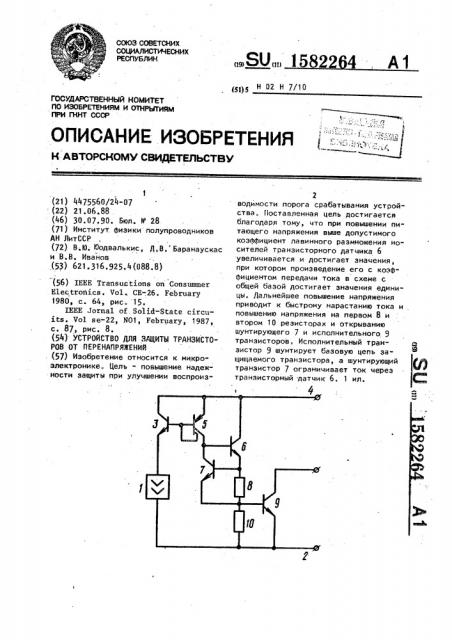

На чертеже представлена схема уст- 1О ройства для защиты транзисторов от

l еренапряжений.

Устройство содержит источник то.ка 1, подключенный между отрицательной шиной питания 2 и эмиттером пер- 15 ,ного транзистора 3, коллектором под,ключенного к положительной шине пита-, ния 4, эмиттеру второго транзистора 5 и коллектору транзисторного датчика

1 6 база которого подключена к кол- 20 лектору шунтирующего транзистора 7, 1 оаза которого подключена к эмиттеру .ранзисторного датчика. 6, и через . первый резистор 8 - к базе исполнительного транзистора 9 и .эмиттеру шунтирующего транзистора 7, подклю ченного через второй резистор 10 к эмиттеру исполнительного транзистора

9 и отрицательной шине питания 2.

База первого транзистора 3 подключена к базе и первому коллектору вто, рого транзистора 5, второй. коллектор

,которого подключен к коллектору шун-

,тирующего транзистора ! Устройство работает следующим об- Ç5

;разом.

11

В исходном состоянии источник тока задает ток Та в эмиттерной цепи ! первого транзистора 3, а в цепи его 40 базы устанавливается ток, определяемый выражением

199 (1)

Р э+1 где p - статический коэФФициент пере- 5 з дачи тока первого транзистора 3;

I g — ток базы транзистора 3.

Ток 1gg поступает на базу и коллектор второго транзистора 5. При этом.„ ток в цепи второго коллектора можно записать в следующем виде (2) где N — соотношение площадей первого и второго коллекторов транзистора 5.

Ток в эмиттерной цепи транзистора 6 можно записать а6 Гкал(Ь+ 1), (3)

1 где в - статический коэФФициент пе" редачи тока транзистора 6;

I9< - ток эмиттера .транзистора 6.

Подставляя выражение (1) в выражение (2), а потом " в уравнение (3), можно получить следующее

Х99 (ф +1) N

I (4)

96 /Ьз+ 1

Первый транзистор 3 и транзисторный датчик 6 выполняются в одном кармане, поэтому. можно принять, что я

= р, тогда выражение (4) принимает вид эй. аз 11

Таким образом, ток эмиттера транзисторного датчика 6 зависит от только от соотношения. коллекторных площадей N второго транзистора 5 и не зависит от р транзисторов первого 3 и транзисторного датчика 6, ток эмиттера которого на первом и втором резисторах 8 и 10 создает падения напряжения, равные соответственно

UéR â 1ý„R„(S) (7) где И вЂ” падение напряжения на перйз вом резисторе 8;

U — падение напряжения на втоRgo ром резисторе 10;

R >, R„ — сопротивление первого и второго резисторов 8 и 10 соответственно.

При максимально допустимом напряжении питания для данной интегральной схемы (8) (9) 8 Б97

Й 10 699 где U — напряжение база-эмиттер бзт шунтирующего транзистора 7;

U Бэ 9 напряжение база эмиттер ис полнительного транзистора 9.

Как следует из выражений (8) и (9) эти транзисторы при допустимом питающем напряжении закрыты и на работу защищаемой схемы не влияют.

При повышении питающего напряЖения выше допустимого, коэФФициент лавинного размножения носителей M тран- зистора транзисторного датчика 6 уве" личивается и достигает значения при котором

2264 6

158 (10) 5

1О формула изобретения

40 ра подключена к базе второго транзистора и первому его коллектору, второй коллектор которого подключен к коллектору шунтирующего транзистора.

Составитель В.

Бояринов

Редактор Н. Ывыдкая Техред Л.Олийнык

Корректор t1. Кучерявая

Заказ 2093 Тираж 475 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Ъ

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина,101 где y(- коэффициент передачи тока транзисторного датчика 6 в схеме с общей базой.

Дальнейшее повышение напряжения приводит к быстрому нарастанию тока и повышению напряжения на первом и втором резисторах 8 и 10 и открыва" нию шунтирующего 7 и исполнительного

9 транзисторов. Исполнительный транзистор 9 шунтирует базовую цепь защищаемого транзистора (не показан), а шунтирующий транзистор 7 ограничивает ток через транзисторный датчик

6. Поскольку защищаемый транзистор сформирован в одном кристалле с транзисторным датчиком 6; максимальное

его напряжение U, при котором

K Э Mo(leg становится действительным соотношение (10), равно соответствующему напряжению транзисторного датчика 6.

Для надежности защиты ток, создаваемый источником тока 1, выбирается согласно соотношению (5) при условии, что через первый транзистор 3, транзистор 3, транзисторный датчик 6 протекает ток, соответствующий максимальному статическому коэффициенту передачи тока, который в свою очередь определяется иэ конкретных тополо ических и технологических параметров транзисторов.

В устройстве, в цепи управления режима транзистора-датчика напряжения "пинч" резистор, имеющий низкую воспроизводимость сопротивления, заменен транзисторной схемой. Напряжения на первом и втором резисторах

8 и 10, как следует из выражений (5), (6) и (7), не зависит от транзисторов, а лишь от хорошо воспроизводимого соотношения площадей коллекторов, транзистора 5 и сопротивлений резисторов. Поэтому увеличивается воспроизводимость величИны дарения напряжения на первом и втором резисторах

8 и 1О, и тем самым, как следует, из выражения (8) и (9), воспроиэводимость порога срабатывания устрой" ства, что обуславливает увеличение надежности защиты.

Устройство для защиты транзисторов,от перенапряжений, содержащее источник тока, транзисторный датчик, предназначенный для подключения коллектором к положительной шине питания, исполнительный транзистор, подключен" ный Ьазой к одному выводу первого резистора, а эмиттером - к одному выводу второго резистора, предназначенного для подключения к отрицательной шине питания, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности защиты при улучшении воспроизводимости порога срабатывания устройства, оно снаЬжено первым и вторым транзистором, причем, другой вывод второго резистора подключен к эмиттеру транзисторного датчика и базе шунтирующего транзистора, эмиттер которого подключен к Ьазе исполнительного транзистора, а коллектор - к базе транзисторного датчика, коллектор первого транзистора подключен к эмиттеру вто" рого транзистора и коллектору транзисторного датчика, эмиттер первого транзистора через источник тока подключен к эмиттеру исполнительного транзистора, и база первого транзисто