Логическая матрица с программируемой памятью

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для реализации управляющих и коммутирующих устройств в микропроцессорных системах. Цель изобретения - увеличение информационной емкости логической матрицы, достигаемое путем динамической перестройки триггеров. Устройство содержит с первого по четвертый блоки 1 - 4 памяти, с первого по N-й коммутационные блоки 5 1 - 5 N, блок 6 дешифраторов, вход 7 начальной установки устройства, группу управляющих входов 8, первые 9 - 12 и вторые 13 - 16 адресные входы с первого по четвертый блоков памяти, а также информационные выходы 17 - 20 этих блоков, первые группы входов 21 и выходов 22, вход-выход 23, синхровход 24, вход 25 начальной установки управляющих входов 26 I-го коммутационного блока, первый 27 и второй 28 синхровходы устройства, вторые группы выходов 29 и информационных входов 30 I-го коммутационного блока. 1 з.п. ф-лы, 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН щ)5,Н 03 K 19/177,: 19/20

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н Д BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

Г1РИ ГКНТ СССР (21) 4494765/24-21 (22) 14.10.88 (46) 30.07.90. Бюл. N 28 (72) В.Ф.Криворучко, Г.М.Попова, С.Ф.Кибирев и Е.А.Шаламов (53) 681.324(088.8) (56) Баранов С.И., Скляров В..А. Цифровые устройства на программируемых

БИС с матричной структурой. М.: Радио и связь, 1986.

EPLD Handbook, Altera corporation, 1984. (54) ЛОГИЧЕСКАЯ МАТРИЦА С ПРОГРАММИРУЕМОЙ ПАМЯТЬЮ (57) Изобретение относится к вь1числительной технике и может быть использовано для реализации управляющих и коммутирующих устройств в микропроцессорных системах. Цель изобрете„„SU„„1582353, А1

2 ния - увеличение информационной емкости логической матрицы, достигаемое путем динамической перестройки триггеров. Устройство содержит с первого по четвертый блоки 1-4 памяти, с первого по N-й коммутационные блоки 5, -5y, блок 6 дешифраторов, вход

7 начальной установки устройства, группу управляющих входов 8, первые

9-12 и вторые 13-16 адресные входы с первого по четвертый блоков памяти, а также информационные выходы 17-20 этих блоков, первые группы входов 21 i и выходов 22, вход-выход 23, синхро- . вход 24, вход 25 начальной установки, группу управляющих входов 26 i-ro коммутационного блока, первый 27 и второй 28 синхровходы устройства, вторые группы выходов 29 и информационных входов 30 1. го коммутационного блока. 1 з.п. ф"лы, 3 ил.

15823 53

Изобретение относится к вычислительной технике и может быть использовано для реализации управляющих и коммутирующих устройств в микропроцесс:pHblx системах. .5

Цель изобретения - увеличение информационной емкости матрицы путем динамической перестройки триггеров.

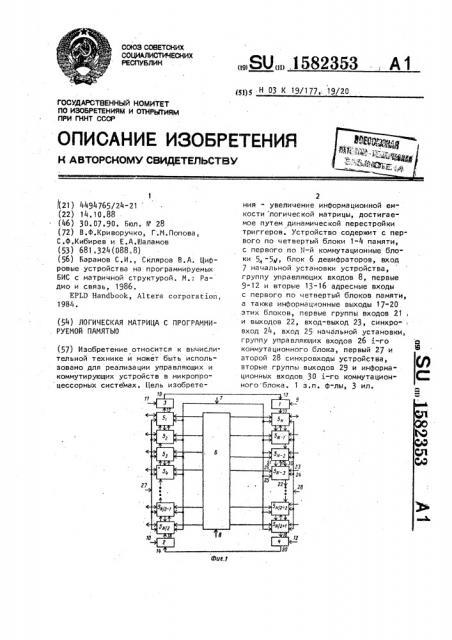

На фиг. 1 представлена структур,,ная схема матрицы; на Фиг ° 2 - струк-! ! турная схема i-го коммутационного блока; на Фиг. 3 - структурная схема ;блока ввода.-вывода.

Матрица (фиг. 1) содержит с пер.вого по четвертый блоки 1-4 памяти, :с первого по N-й коммутационные блоки 5, -5, блок б дешифраторов, вход

7 начальной установки устройства, :группу управляющих входов 8 устрой:ства, первые адресные входы 9-12 с ,. первого по четвертый блоков памяти, вторые адресные входы 13-16 с перво:го по четвертый блоков памяти, инФормационные выходы 17-20 с первого 2 о четвертый блоков памяти, первую группу информационных входов 21 i-го коммутационного блока, первую группу выходов 22 1 го коммутационного блока, вход-выход 23 i-ro коммутационно- З0 го блока, синхровход 24 i-ro коммутационного блока, вход 25 начальной . установки i-rn коммутационного блока, группу управляющих входов 26 i-го коммутационного блока, первый 27 и . второй 28 синхровходы устройства, вторую группу выходов 29 i-ro комму тационного блока и вторую группу инФормационных входов 30 1.-го коммутационного блока.

i-й коммутационный блок (фиг. 2) включает первый 3 1 и второй 32 узлы памяти, первый 33 и второй 34 мультиплексоры, первый 35 и второй

36 элементы ИЛИ, блок 37 ввода-вывода„ первый синхровход 38 блока вводавывода, пеовый управляющий вход 39 . блока ввода-вывода, информационный вход 40 блока ввода-вывода, второй управляющий вход 41 блока ввода-вывода, вход 42 сброса блока ввода-вы50 вода и выход 43 блока ввода-вывода.

Блок ввода-вывода (Фиг. 3) образуют мультиплексор 44, первый 45 и второй 46 узлы коммутации, элемент

47 с тремя состояниями, элемент

НЕ 48, с первого по шестой элементы

И 49-54 и с первого по пятый. элементы ИЛИ 55-59.

Перестраиваемый триггер, реализованный на элементах 49-59, предназначен для хранения одного разряда внутреннего состояния автомата, реализуемого на логической матрице с программируемой памятью. Подача на второй управляющий вход блока 37 сигнала "0" или "1" определяет соответственно настройку триггера на реализацию D- или Т-триггера.

Устройство работает следующим образом.

Перед началом работы на вход начальной установки устройства приходит сигнал, устанавливающий перестраиваемые триггеры устройства в начальное состояние., Работа устройства начинается с подачи на er o группу управляющих входов настроечного кода, который через блок 6 децифраторов задает мультиплексорам 33, 34 и 44 и узлам 45 и 46 коммутации i†- го коммутационного блока, где i = 1,..., N, соответствующий режим работы. По этому же настроечному коду i-й вход-выход устройства настраивается либо на выход устройства, либо на вход устройства в зависимости от сигнала на управляющем входе элемента

47. Соответствующий настроечный код позволяет использовать для реализации булевой функции на информационном или втором управляющем входе блока 37 от одного до четырех узлов памяти устройства. При этом возможно использование информации (термов) одних и тех же узлов памяти для реализации от двух до четырех булевых функций. Такт работы устройства определяется в зависимости от сигналов на первом и втором синхровходах устрой- ства, а также информации на первом информационном выходе узла 31 памяти

1 го коммутационного блока, 1 = 1, N„ Пусть на первый и второй синхровходы устройства поступает один и тот же тактовый сигнал 7, а на вход 8 устройства подан настроечный код, который настраивает мультиплексор 44 на выдачу сигнала на входы элементов И 51-54. Тогда такт работы устройства определяется периодом следования тактового сигнала, Рассмотрим t-й такт работы устройства.

На информационные входы и входы-вы" ходы устройства, настроенные по настроечному коду как входы, поступает входной код, которo é "обозначим сос5 15823

t тоянием х . Код х и состояние пев 8 рестраива емых триггеров коммута ционных блоков устройст ва, соста вляющи х

1 5 внутреннее состояние а; логической матрицы, определяют адреса на адресных входах блоков 1-4 памяти и узлов

31 и 32 памяти коммутационных блоков устройства. На информационных выходах блоков 1-4 памяти и узлов 31 и 32 памяти появляются коды, определяющие код выходного состояния у, который выдается по входам-выходам устройства, настроенным как выходы логической матрицы. Одновременно на вторые управляющие входы блоков 37 ввода-вывода с выходов элементов ИЛИ 36 поступает код настройки P перестраива- 2О

1 мых триггеров на типы триггеров в следующем (t+1)-м такте работы. На информационные входы блоков 37 вводавывода коммутационных блоков устройства с выходов элементов ИЛИ 35 коммутационных блоков поступает код с возбуждения R .. При поступлении сле-! и дующего (t+1) -го сигнала на первый и второй синхровходы устройства перестраиваемые триггеры коммутационных

ЗО блоков устанавливаются в новые состояния, что соответствует коду следующего внутреннего состояния а ".+ .

Информация в блоках 1 — 4 памяти и узлах 31 и 32 памяти коммутационных блоков определяет режим коммутации информационных входов. и выходов устройства наряду с информацией на группе управляющих входов 8. Это позволяет использовать устройство для реализации различных функций коммутации, систем булевых функций, а также функций возбуждения автомата, Логическая матрица с программируемой памятью позволяет при эквивалентных аппаратных затратах увеличить эффективную информационную емкость устройства по записи в него реализуемой системы булевых функций коммутаций или цифрового автомата.

Это достигается за счет двух факторов: в устройстве используются общие термы для реализации различных как выходных функций. коммутации, так и функций возбуждения автоматов, в устройстве динамически перестраиваются типы триггеров автомата в

53 б процессе его функционирования, что позволяет задавать оптимальный набор типов триггеров не статически (как в известном устройстве, т.е. не изме- няя этот набор в процессе функционирования автомата), а динамически в каждом такте работы устройства. формула изобретения

1. Логическая матрица с программируемой памятью, содержащая с пер" вого по четвертый блоки памяти, с первого по N-й коммутационные блоки, где N — число входов-выходов устройства, блок дешифраторов, причем группа управляющих входов устройства соединена с группой информационным входов блока дешифраторов, вход на" чальной установки устройства подключен к входу начальной установки К-го коммутацибнного блока, К = 1, ...,N

1-й информационный вход устройства соединен с первым адресным входом

i-го блока памяти, i = 1,4, вторые адресные входы первого и второго блоков памяти соединены с инФормационными выходами соответственно третьего и четвертого блоков памяти, вторые адресные входы которых соединены с первыми группами выходов соответственно первого и (N/2+1)-го коммутационных блоков, информационные выходы первого и второго блоков памяти соединены с первыми группами информационных входов соответственно

N-го и И/2-го коммутационных блоков, первая группа информационных входов

j-го коммутационного блока соединена с первой группой выходов (1+1.)-го коммутационного бпока, j = 1, (, 2-1), (N/2+ ) ° ..,,N-1 вх .-д-выход

К-го коммутационного блока, К = 1, М является входом-выходом устройства, первый синхровход устройства соединен с синхровходами с первого по

N/2-й коммутационных блоков, второй синхровход устройства соединен с синхровходами с (N/2+1)-го по N-й коммутационных блоков, К-я группа выходов блока дешифраторов соединена с группой управляющих входов К-ro коммута ционного блока, K=1,..., N, вторая группа вьходов 1 — го коммутационного блока соединена с второй группой информационных входов (1+1)го коммутационного блока, 1 = 1,3,5, N 1, вторая группа информационI нык Входов 1-ro коммутационного оло- третьим входами группы управляющих ка соединена с второй группой выхо- входов К-го коммутационного блока, дов "„ +t)"-ão коммутационного блока, первые выходы первого и второго муль1 " 1,3„5 N-l причем К-й ком- типлексоров соединены соответственно мутационный блок содержит первый с первым и вторым входами первого узел памяти, первый элемент ИЛИ и элемента ИЛИ К-го коммутационного блОк ВВОда Вывода р причем первая блока, третьи и четвертые входы котогруппа информационных входов К-го рог о соединены с первым и вторым коммутационного олока соединена с lg входами второй группы информационных, первым адресным входом первого узла входов К-ro коммутационного блока, ! flBHR TM первый информационный выход вторые выходы первого и второго муль, первого узла памяти соединен с пер - типлексоров соединены соответствен, вым синхровходом блока ввода-вывода, но с первым и вторым входами второго

; второй синхровход которого соединен l5 элемента ИЛИ К-ro коммутационного

: с синхровходом К-го коммутационного блока, третьи и четвертые входы котоблока, лервый вход группы управляю- рого соединены соответственно с щих входов которого соединен с. первым третьим и четвертым входами второи управляющим входом блока ввода-выво- -руппы информационных входов К-го да, вход начальной установки которо- 2 коммутационного блока,, первый и Вто» го соединен с одноименным входом рой выходы второй груп-ы выходов ко"

К"го коммутационного блока. вход-вы- торого соединены соответственно с ход которого соединен с входом-вы- третьим и четвертым выходами первого ходом блока ввода-вывода, выход кото- мультиплексора К-ro коммутационного рого соединен с вторым адресным вхо- 25 блока,, третьи и четвертые выходы втодом первого узла памяти К-го комму- рого мультиплексора К-го коммутационтационного блока, информационный ного блока соединены соответственно вход блока Ввода-вывода соединен с с третьим и четвертым выходами второи выходом первого элемента ИЛИ К-"o группы Выходов К-го коммутационного коммутационного блока, о т л и ч а- „-.;, блока. юща я с я тем, что, с целью уве- 2. Иатрица поп., 1, от л и ч а личения информационной емкости уст- ю щ а я с я тем, что блок вводаройства за счет динамической перест- вывода содержит мультиплексор, пер" ройки триггеров в К-й коммутационный вый и Второй узлы коммутации, элемент

Р ! 1 блок устройства введены второй узел, с тремя состояниями„элемент lr, с памяти, первый и второй мультиппек- первого по щестой элементы ИЛ,, присоры, второй элемент ИЛИ, причем вто- чем первый и Второй информационные рой информационный выход первого уз- входы мультиплексора соединены соотла памяти соединен с первым адресным ветственно с щинои логическои еди входом второго узла памяти К-го ком- АО ницы и нуля, третьи р третьи и четвертые ин" мутационного блока, первыи информа- формационные в одь у .- р фо ма ионные вхо ы мультиплексора, ционный выход которого соединен с д соединены соответственно с первым и первои группои информацион вторым синхровходами блока ввода-выдов К-го коммутационного блока. Вто- вода, первый управляющий вход которой адресный вход второго узла памяти, рого со дине у р" ого сое инен с прoo"вляюлими входами соединен с выходом олока ввода-выво- мультиплексор р

/ м льтиплексора первого и Второго да К-ro коммутационного блока, второй узлов коммутации, выход второго узла управляющии вход которого с торого соединен коммутации является выходом блока с Выходом второго элемента ИЛИ, вто- ввода-вывода, вход-выход которого рой информационныи выход второго у ход второго уз- соединен с первым информационным ла памяти соединен с входом с5ооо х дом сороса Входом Второго узла коммутации и с

К-г оммутацион- входом-Выходом элемента с тпемя сосблока ввода-вывода К-го коммут ц тояниями, управляющий вход которого ного блока, третьи инц ормационные .выходы первого и второго узлов и т рого узлов памяти соединен с первым выходом мультисоединены с информационными вход ф ионными входами плексора, информа ционный вход элемента с тремя состояниями соединен с соответственно первого и второго выходом первого узла коммутации, .мультиплексоров ""ãî коммутационного информационный вход блока ввода-вывоблока, управляющие входы которых да соединен с первыми входами перво" соединены соответственно с вторым и го и второго элементов И, выходы которых соединены с входами первого элемента ИЛИ, выход которого соединен с первым входом третьего элемента И, первый вход четвертого элемента И соединен с информационным входом блока ввода-вывода, с входом элемента НЕ, с первым информационным входом первого узла коммутации, второй информационный вход которого соединен с выходом элемента НЕ, вторые входы третьего и четвертого и первые входы пятого и шестого элементов И соединены с вторым выходом мультиплексора, выходы третьего и четвертого элементов И соединены с первыми входами второго и третьего элементов ИЛИ, выходы которых соединены соответственно с вторыми входами пятого и шестого элементов И, выходы которых соединены с первыми входами четвертого и пятого элементов

ИЛИ, выходы которых соединены соответственно с третьими входами треть2353 о его и четвертого элементов И, выход второго элемента ИЛИ. соединен с вторым входом третьего элемента ИЛИ, 5 выход которого соединен с вторым входом второго элемента ИЛИ, выход четвертого элемента ИЛИ соединен с третьим информационным входом первого узла коммутации, вторым информационным входом второго узла коммутации и вторым входом пятого элемента ИЛИ, выход которого соединен с четвертым информационным входом первого узла коммутации и вторым входом четвертого элемента ИЛИ, третий вход которого является входом начальной установки блока ввода-выво" да, вход сброса которого соединен с третьим входом пятого элемента ИЛИ, 20 третий информационный вход второго узла коммутации соединен с информа" ционным входом блока ввода-вывода, второй управляющий вход которого соединен r. вторыми входами первого

25 и второго элементов И.

1582353

Составитель С.Шевцов

Техред Л.Серд скова Корректор С.Черни

Редактор А.Огар. Заказ 2097 Тираж 670 Подписное

ВНИИПЯ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Рауаская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101