Измеритель скорости звука

Иллюстрации

Показать всеРеферат

Изобретение касается акустических измерений и может быть использовано для измерения скорости звука в жидкостях. Цель изобретения - повышение точности измерений за счет исключения неравномерности пульсаций частоты выходного сигнала. При работе измерителя происходят сравнение времени задержки сигнала в акустическом тракте с длительностью заданного импульса и в зависимости от результата подстройка управляющего напряжения. В установившемся режиме происходит чередование сигналов высокого и низкого логических уровней, приводящее соответственно к росту или снижению управляющего напряжения на равные величины. 1 з.п.ф-лы, 3 ил.

СОЮЗ ООВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51)5 С 01 H 5/00

Lbiuii.;, ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н A ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ МОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ. И ОТНРЫ! ИЯМ

ПРИ ГКНТ СССР

1 (21) 4433366/25-28 (22 ) 11.05.88 (46) 07.08,90. Бюл. ¹ 29 (7 1) Научнс -производственное объединение космических исследований (72) А.И.Измайлов, З.Ш.Аллахвердова, Н.А.Насибов и А.А.Камилсв (53) 534.22 (088.8) (56) Исмаилов Т.К, Измайлов А.З., Аллахвердов Ф.M. Состояние и некоторые перспективы развития средств измерения гидрологических параметров

Мирового океана.-Измерение, контроль, автоматизация, 1985, № 4, с.3-11. (54) ИЗИЕРИТЕЛЬ СКОРОСТИ ЗВУКА (57) Изобретение касается акустических измерений и может быть использоИзобретение относится к области акустических измерений и может быть использовано для измерения скорости . звука в жидкостях.

Цель изобретения — повышение точности измерений скорости звука в контролируемой среде за счет исключечия неравномерности пульсаций частоты выход но го с иг н ал а.

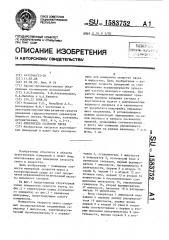

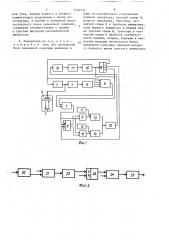

На фиг.1 представлена структурная схема измерителя скорости звука; на фиг.2 — структурная схема логического элемента; на фиг.3 — временные диаграммы, иллюстрирующие работу измерителя.

Измеритель скорости звука содержит последовательно соединенные ге" нератор 1 импульсов, электроакустический преобразователь 2 с отража„„SU„„1583752 . А 1

2 вано для измерения скорости звука в жипкостях. Цель изобретения — повышение точности измерений за счет исключения неравномерности пульсаций частоты выходного сигнала. При работе измерителя происходят сравнение времени задержки сигнала в акустическом тракте с длительностью заданного импульса и в зависимости от результата подстройка управляющего напряжения. В установившемся режиме происходит чередование си налов высокого и низкого логических уровней, приводящее соответственно к росту или снижению управляющего напряжения на равные величины. 1 з.п. ф-лы, 3 ил. телем 3, ограничитель 4 импульсов и компаратор 5, логический блок 6 временной селекции, первый формирователь 7 импульсов, дискриминатор 8 длительности, первую 9 и вторую 10 схемы И, первый 11 и второй 12 источники тока, первый 13 и второй 14 коммутаторы и последовательно соединенные интегратор 15, управляемый генератор 16, второй формирователь

17 импульсов, делитель 18 и распреде" литель. 19 импульсов.

Вход генератора 1 импульсов подключен к первому выходу распределителя 19 импульсов, первые входы первой 9 и второй 10 схем И соединены соответственно с первым и вторым выходами дискриминатора 8 длительности, выходы первой 9 и вто1583752

40 рой 10 схем И соединены соответствен- но с перными входами первого 13 и второго 14 коммутаторов, нторые входы которых подключены соотнетст5 венно к источникам 11 и 12 тока, выходы первого 13 и второго 14 коммутаторов соединены с входом интегратора 15, выход первого формирователя 7 импульсов соединен с первым входом дискриминатора 8 длительности и с вторыми входами первой 9 и второй 10 с.хем И, второй вход дискриминатора 8 длительнос-..и подключен к второму выходу распределителя 19 I5 импульсов, первый и второй входы первого формирователя 7 импу,. ьсов соединены соответственно с выхс Дом логического блока Ь временной се-. лекции и с третьим выходом распре делителя 19 импульсов, а первый, второй, третий и четвертый входы .лигического блока 6 временной селекции подклкчены соответственно к выходам компаратора 5 и делителя 18 25 и к первому и третьему выходам распределителя 19 импульсон.

Логический блок 6 временной селекции может быть выполнен н виде последовательно соединенных первого инвертора 20, третьей схемы И 21, второго инвертора 22, триггера 23, четвертой схемы И 24 и третьего инвертора 25, выход которого служит выходом логического элемента 6, выход первого инвертора 20 и вторые входы третьей схемы И 21, триггера 23 и четвертой схемы И 24 являются соответственно первым, вторым, третьим и четвертым входами логического блока 6 временной селекции.: Временные диаграммы 26-30 приведены HR фиг.З.

Измеритель скорости звука работает следующим образом. 45

Выходной сигнал генератора 1 импульсов поступает на пьезоэлемент электроакустического преобразователя

2>преобразующего электрический импульс в ультразвуковой. Ультразвуковой импульс после зондирования контролируемой среды и отражения от отражателя 3 преобразуется преобразователем 2 и электрический сигнал, который через ограничитель 4 импуль55 ссв поступает на вход компаратора 5 и с его выхода — на первый вход логического блока 6 временной селекции. Далее сигнал с выхода ло ического блока б. пс ступает на пер-, вый выход перво1о формирователя 7 им пульсов. Перевод формирователя 7 в псложение " 1" (передний фронт приемного сигнала ) осуществляется импуль-. сом компаратора 5 при поступлении приемного сигнала через логический блок 6, а возврат в исходное состояние — импульсом с третьего выхода распределителя 19 импульсов. Выходной сигнал формирователя 7 поступает на первый (П) информационный вход дискриминатора 8 длительности, а также на вторые входы первой 9 и второй 10 схем И. На второй (С) вход дискриминатора 8 длительности поступает выходной сигнал с второго выхода распределителя 19 импульсов.

Дискриминатором 8 осуществляется с.равнение времени зондирования ультразвуковым импульсом контролируе— мой среды с длительностью импульса на выходе распределителя 19. При этом сравнивается нременное расположение переднего фронта приемного сигнала относительно переднего фронта импульса, формируемсго на втором выходе распределителя 19.импульсон (задний фронт импульса на первом выходе распределителя 19 импульсов).

Если передний фронт приемного сигнала опережает во времени передний фронт. импульса, формируемого на втором выходе распределителя 19 импульсов, то на первом выходе дискриминатора 8 формируется сигнал высокс:го уровня ("1"), а на втором — низкого урсвня (0"). В противном случае, на первом выходе дискриминатора 8 формируется сигнал низкого уровня ("0"), а на втором выходе — высокого уровня ("1").

Сигналы высокого и низкого логических уровней на выходах первой 9 и второй 10 схем И формируются лишь при наличии импульса на выходе формирователя 7, причем, если передний фронт премного сигнала опережает передний фронт импульса, формируемого на втором выходе распределителя 19, то на выходе первой схемы И 9 действует сигнал высокого логического уровня, а на выходе второй схемы И 10 — сигнал низкого логического уровня. В прстивном случае— наоборот.

Сигнап высокого логического уровня с выхода схемы И 9 открывает первый коммутатор 13, подключая выход

1583752

6 ное состояние по фронту б (29, фиг.3) .

Триггером 23 и четвертой схемой И 24 обеспечивается прохождение приемного сигнала с выхода компаратора 5 на

t вход формирователя 7. Пропуск сигнала схемой И 24 осуществляется при рабочем состоянии триггера 23. Приемный сигнал инвертируется третьим инвертором 25 и поступает на первый вход формирователя 7. первого источника 1! тока к входу интегратора 15. Ток источника 11 вызывает рост напряжения на конденсаторе интегратора с практически постоянной крутизной. При этом на выходе схемы И 10 действует сигнал низкого логического уровня.и второй коммутатор 14-закры1..

Если передний фронт приемного сигнала отстает от переднего фронта импульса, формируемого на втором выходе распределителя 19, то напряжение на интепраторе 15 .убывает с практически постоянной крутизной

Ф так KdK при этом на выходе схемы

И 10 действует сигнал высокого логического уровня, приводящий к отпиранию коммутатора 14 и тем самым к подключению второго источника 12 тока к входу интегратора 15. Конденсатор интегратора 15 при этом разряжается током источника 12 тока, а коммутатср 13 закрыт. В установившемся режиме работы измерителя на выходе дискриминатора 8 длительности происходит чередование сигналов высокого и низкого логических уровней

9 приводящее соответственно к росту или снижению управляющего напряжения на выходе интегратора 15 на практически одинаковые величины.

Выхсд интегратора 15 соединен с входом управляемого генератора 16, выходные синусоидальные сигналы которого нормализуются вторым формирователем 17 импульсов и в виде прямоугольных импульсов поступают на делитель l8 Сигналы с выхода делителя 18 поступают на вход распределителя 19 импульсов, задающего пссле- довательность работы функциональных блоков измерителя.

Логический блок 6 выполняет .функции "временных Bnpc:ò" и обеспечивает прохождение на вход формирователя 7 только приемного сигнала. Прямоугольные импульсы 26 (Аиг.3) .,с выхода делителя 18 поступают на первый ин-. вертор 20, откуда подаются на первый вход третьей схемы И 21, на второй вход которой пс ступают импульсы 27 с первого выхода (фиг.3).распределителя 19. На выходе второго инвертора 22 формируется импульс 26, передний фронт ксторого совпадает с фронтом а. Триггер 23 переходит в новое состояние (рабочее) по фронту а (26, фиг.З), а возвращается в исходФормула изобретения

1. Измеритель скорости звука, содержащий последовательно соединенные генератор импульсов, электроакусти,ческий преобразователь с отражателем, ограничитель импульсон и компаратор, 20 логический блок временной селекции, первый формироватех ь импульсов, дискриминатор длительности и пс следовательно соединенные интегратор, управляемый генератор, второй фор25 мирователь импульсов, делитель и распределитель импульсов, первый и второй входи логического блока временной селекции соединены соответственно с выходами компаратора и делителя, первый вход первого формирователя импульсов подключен к выходу логического бпока временной селекции, вход генератора импульсов соелинен с первым выходом распрецелителя импульсов, пеРвый и втоРой входы дискриминатора длительности соединены соответственно с выходом первого формирователя импульсов и вторым выходом р.-спределителя импульсов, третий выход которого подключен к второму входу первого формирователя импульсов, о т л и ч а юшийся тем, что, с целью повышения точности измерений за счет

45 исключения неравномернс:сти пульсаций частоты выходного сигнала, он снабжен первой и второй схемами И, первым и вторым коммутаторами и первым и вторым источниками тока, первые входы первой и второй схем И соединены соответственно с первым и вторым выходами дискриминатора длительности, вторые входы первой и второй схем И подключены к выходу первого

55 формирователя импульсов первыи и второи входы первого и второго коммутаторов соединены соответственно с выходами первой и второй схем И и с выходами первого и второго источни.

7 15837 ков тока, выходы первого и второго коммутаторов подключены к входу интегратора, а третий и четвертый входы логического блока временной селекции, 5

c .oåäèíåíû соответственно с первым и тр ет ьим выход ами р аспр еделит е ля импульсов. !

2. Измеритель по п.3, о т л и— ч а ю шийся тем, что логический блок временной селекции выполнен в

52 виде последовательно соединенных первого инвертора, третьей схемы И, вторс ro инвертора, триггера, четвертой схемы И и третьего инвертора, вход первого инвертора и вторые входы третьей схемы И, триггера и четвертой схемы И являются соответственно первым, вторым, третьим и чет" вертым входами логического блска временной селекции, выходом которого является выход третьего инвертора

Фиг. z

15837 2

Составитель Д.Широчин Редактор Н. Тупица Техред А, Кравчук Корректор В. Гирняк

Заказ 2246 Тираж 420 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101