Измеритель скорости изменения частоты линейно-частотно- модулированного сигнала

Иллюстрации

Показать всеРеферат

Изобретение относится к радиоизмерительной технике и может быть использовано для измерения скорости изменением линейно-частотно-модулированных сигналов. Цель изобретения - повышение быстродействия-достигается путем получения информации о скорости изменения частоты сигнала из произведения двух сигналов, сформированных во введенных блоках перемножения 10 и вычитания 3, а также введенными фильтром 5, блоком 6 нелинейного преобразования, фазовращателем 7, линий 8 задержки, перемножителем 9. На чертеже также показаны линия 1 задержки и перемножителем 9. На чертеже также показаны линия 1 задержки и перемножитель 2. 1 ил.

СОЮЗ СОВКТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51) 5 G 01 R 23/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГДсУДАРстВенный нОмитет

О ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

И ГКНТ СССР (21) 4345395/24-21 (22) 16,12.87 (46) 07.08.90. Бюл, Р 29 (71) Уральский политехнический инсТитут им. С.М.Кирова (72) В.И.Лузин, А.А.Дурнаков, 9.А.Добряк, В.Д,Нехорошев

Н.П.Никитин (53) 621.317 (088.,8) (56) Патент США У 3528033, кл. 331-178, 1968. (54) ИЗМЕРИТЕЛЬ СКОРОСТИ ИЗМЕНЕНИЯ 1АСТОТЫ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННОГО СИГНАЛА

;57) Изобретение относится к радиоизмерительной технике и может быть использовано для измерения скорости изменения линейно-частотно-модулированных сигналов. Цель изобретения повышение быстродействия — достигается путем получения информации о скорости изменения частоты сигнала из произведения двух сигналов, сфорMHpoBQIiHblx íî BpåäåHHûõ блоках перемножения 10 и вы ппания Э, а также введенными фильтром 5, блоком 6 нелинейного преобразования, фазовращателем 7, линией 8 задержки, перемнажителем 9. На чер-еже также показаны линия 1 задержки и перемножитетп, 2, 1 ил..1583862

Изобретение относится к радиоизмерительной технике и предназначено для измерения скорости изменения частоты линейно-частотно-модулированного сигнала, Цель изобретения — повышение быстродействия измерителя скорости изменения частоты линейно-частотно"модулированного сигнала. 10

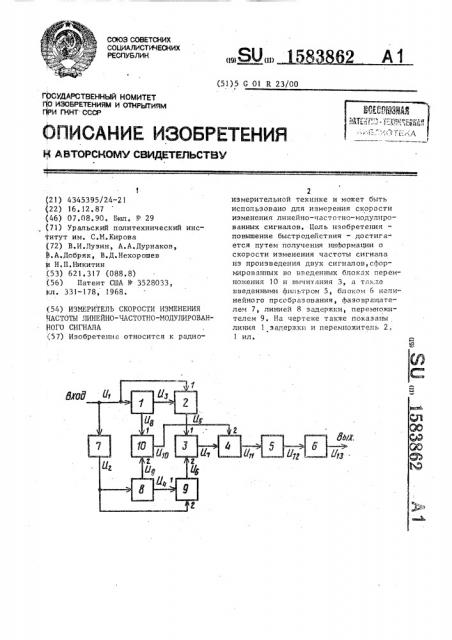

На чертеже приведена структурная схема измерителя скорости изменения частоты линейно-частотно-модулированного сигнала.

Измеритель скорости изменения час- 15 тоты линеййо-частотно-модулированного сигнала содержит последовательно соединенные первую линию I задержки, первый перемножитель 2, второй вход которого и вход первой линии эадерж- 20 ки подключены к входу измерителя, блок 3 вычитания, третий перемножитель 4, фильтр 5 и блок 6 нелинейного преобразования, выход которого подключен к выходу измерителя, последовательно соединенные фазовращатель

7, вторую линию 8 задержки и четвертый перемножитель 9, второй вход которого подключен к выходу фаэовращателя 7, а выход соединен с вторым 30 входом блока вычитания, отводы линий

1 и 8 задержек соединены с входами перемножителя 10, а вход фаэовращателя 7 — с входом первой,.линии 1 задержки. 35

Измеритель скорости изменения частоты линейно-частотно-модулированного сигнала работает следующим образом. На вход измерителя поступает напряжение 40 ц, = П. c os fat + Чс j, где U — - амплитуда сигнала;

V — скорость изменения частоты М сигнала; 45

t — - время.

Фазовращатель 7 поворачивает фазу входного напряжения на f j/2, Тогда на выходе фазовращателя 7 имеют напряжение

U, = U sin(t + Vt1j.

Учитывая, что время задержки в первой 1 и второй 8 линиях задержки составляет 2 > в каждой, имеют на 55 выходе первой линии 1 задержки,напряжение

Q3» U cos (ы(й - 2 1j) +

+ Ч(— 2 )1) при ) 2 на выходе второй линии 8 задержки

Я = U sin (td {t — 2 >) +

+ V(t - 2С3) ) при t)2 <, Тогда на выходе первого перемножителя 2

IL cos(yt + Vt ) соэ Lu(t

12

2j.) + V(t — 2 Г)2j при е>20

3 > ) °

На выходе четвертого перемножителя 9

5< = - — — sin(a t +

+ Vt ) sin (u)(t — 2 д ) +

) + V(t — 2i ) ) при t) 2 (, > 9 на выходе блока 3 вычитания

П G.g — K " — — — cosf2(zt +

7 2

+ Vt ) - 2Ы - 4Ч t + 4Ч. 1.

3 3 > при t 3 2Я>.

Время задержки сигнала на выходе отводов в первой линии 1 и второй 8 линиях задержки составляет .1 для каждой. Поэтому сигнал на выходе отвода первой линии 1 задержки имеет вид

Ц = U cos(t0(t -cf ) + V(t -ь )

3 при t ) 6) на выходе отвода второй линии 8 saдержки

Ц = U. sin((d (t - ) + V(t

- 71) ) при t > j. . г 2

Тогда на выходе перемножителя 10

П = Ц„. G = -- - э*- (2{м. +

10 3 3 2

+ Vt + q ) 2(4Чл

"Ъ

2Ч 2 t n

Следовательно, на выходе перемножителя 4 при t 7 2 напряжение имеет

> вид

1583862 6 тельно меньшую инерционность, чем соответствующие цепи в известном измерител е. ц4

К, =ц U = — — sin 2У +

4 ") ПФ

+ - — — sin (4(ыс + Vt + g)

Формула изобретения

4 ц) — 8У + 6У ) Составитель В.Новоселов

Редактор А.Коэориз Техред Л.Сердюкова Корректор С.Шевкун

Заказ 2252 Тираж 561 Подписное

ВНИИПИ I oñóäàðñòâåísoão комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r.Óæãoðîä, ул. Гагарина, 101

Фильтр 5 отфильтровывает вторую составляющую сигнала U, . Блок 6

10 нелинейного преобразования производит нелинейное преобразование arcs in (...) над выходным напряжением фильтра 5, Поэтому на выходе блока 6 нели15 нейного преобразования ц. = — 2У

13 Ф

Таким образом, на выходе измерителя при известной величине выход3 ное напряжение пропорционально величине скорости изменения частоты входного сигнала.

По сравнению с известным быстродействие предлагаемого измерителя больше. Информационным параметром в устройстве является не частота биений между прямым и задержанным сигналами, а разность набегов фаз двух сигналов Ц и- К«, В связи с тем, что эти сигналы являются высокочас- 30 тотными, фильтр 5 нижних частот после перемножителя 4 может иметь значи,Измеритель скорости изменения частоты линейно-частотно-модулированного сигнала, содержащий последовательно соединенные первые линию задержки и перемножитель, второй вход которого соединен с входом устройства и входом первой линии задержки, о т— л и ч а ю шийся тем, что, с целью повышения быстродействия, в него введены последовательно соединенные второй перемножитель, третий перемножитель, фильтр, блок нелинейного преобразования и последовательно соединенные фазовращатель, вторая линия задержки, четвертый перемножитель, блок вычитания, при этом вход фазовращателя соединен с входом устройства, à его выход — с вторым входом четвертого перемножителя, отводы линий задержек соединены с входами второго перемножителя, выход первого перемножителя соединен с вторым входом блока вычитания, выход которого соединен с вторым входом четвертого перемножителя,