Устройство для регистрации последовательности данных

Иллюстрации

Показать всеРеферат

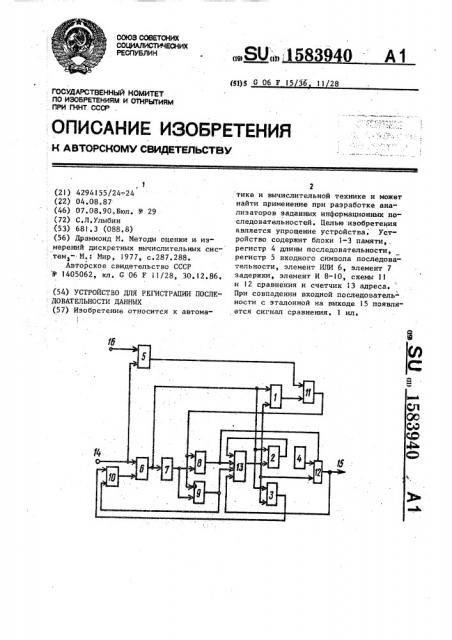

Изобретение относится к автоматике и вычислительной технике и может найти применение при разработке анализаторов заданных информационных последовательностей. Целью изобретения является упрощение устройства. Устройство содержит блоки 1 - 3 памяти, регистр 4 длины последовательности, регистр 5 входного символа последовательности, элемент ИЛИ 6, элемент 7 задержки, элемент И 8 - 10, схемы 11 и 12 сравнения и счетчик 13 адреса. При совпадении входной последовательности с эталонной на выходе 15 появляется сигнал сравнения. 1 ил.

- СОЮЗ GOBETCHHX

СОЦИАЛИСТИЧЕСНИХ

РЕСПУВЛИН

Щ)$ G 06 F 15/36 11 28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОбРЕТЕНИЯМ И (ЛНРЫТИЯМ

ПРИ ГКНТ СССР

l (21) 4294155/24-24 (22) 04.08.87 (46) 07.08.90.Бюл. N- 29 (72) С.Л.Улыбин (53) 681 3 (088,8) (56) Драммонд M. Методы оценки и. измерений дискретных вычислительных сис тем - N.: Мир, 1977, с.287.288.

Авторское свидетельство СССР В 1405062, кл. С 06 F 11/28» 30.12.86, (54) УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ПОСЛЕДОВАТЕЛЬНОСТИ ДАННЫХ (57) Изобретение относится к автома1

„„SU;, 15839 0 А1

2 тике и вычислительной технике и может найти применение при разработке анализаторов заданных информационных последовательностей. Целью изобретения является упрощение устройства. Устройство содержит блоки 1-3 памяти, регистр 4 длины последовательности, регистр 5 входного символа последовательности, элемент ИЛИ 6, элемент 7 задержки, элемент И 8-10, схемы ll и 12 сравнения и счетчик 13 адреса.

При совпадении входной последовательности с эталонной на выходе 15 появля" ется сигнал сравнения. 1 ил, 1583Ì0

Адреса ячеек блоков 1-3 памяти

Адреса пере- Признаки хода (содержи- цикла (сомое блока 2 в держимое блопамяти) ка 3 памяти) Эталонная последовательность (содержимое блока l памяти) 00

0l

10 где А и С - двоичные коды, 1-3 памяти, адрес которых приходит на

Анализируемая. последовательность 4 адресные входы блоков с выхода счетчипоступает на вход 16 устройства. В ка 13, считывается информация. Код пермамеит появления очередного символа ваго элемента эталонной последовательвходной последовательности на такто- ности А с выхода блока 1 памяти постувый вход 14 устройства приходит сигнал . пает на первый вход схемы 11 сравнения, Этот сигнал поступает на вход записи . На второй вход схемы 11 сравнения пос50 регистра 5, записывая. в него ;двоич- - тупает код входного символа с выхода иый код символа последовательности,. регистра 5. Адрес перехода 00 с выхода поступающий с входа 16 на его информа- блока 2 памяти поступает на информационный вход. Кроме того, этот сиг- ционный вход счетчика 13. Признак цик-., Нал поступает va первый вход элемента ла 0 с выхода блока 3 памяти поступа-

ИЛИ 6 на выходе которого появляет» ет на первыи вход элемента И 10. На

Э ся сигнал, который поступает на вход первый вход элемента И 8 и прямой элемента 7 задержки и входы считыва- вход элемента И 9 с выхода элемента 7 сия блоков 1-Э памяти. Иэ ячеек блоков задержки поступает сигнал, задержанный

Изобретение относится к автоматике и вычислительной технике и может быть использовано в анализаторах при отладке программ и аппаратно-программных

5 средств ЭВМ.

Целью изобретения является упрощение устройства, Иа чертеже представлена схема уст" ройства. 10

Устройство содержит три блока 1-3 памяти, регистр 4 длины последовательности, регистр 5 входного символа последовательности, элемент ИЛИ 6, элемент 7 задержки, три элемента И 8" 15

10, две схемы 11 и 12 сравнения, счетчик 13 адреса тактовый вход !4 устрой,, ства,выход 15 признака конца регистрации устройства и вход lб анализируемой последовательности устройства. 20

Блок 1 памяти имеет емкость n x ш, где n — длина (количество ::элементов) эталонной последовательности;,ш - разрядность входного символа последова-... тельности. В нем хранится эталонная последовательность, т.е последова--:.: тельность, которую надо обнаружить во входном потоке. В первой ячейке блока

1 памяти хранится первый элемент эта-, лонной последовательности, во второй -30 второй элемент и т,д..

Блок 2 памяти имеет емкость n x k, где k 1og n, и предназначен для хранения адресов перехода, ðåñ пе" рехода представляет собой адрес ячейки блока 1 памяти, хранящий элементэталонной последовательности, к сравнению с которым надо перейти при не".с совпадении очередного элемента с пос" тупившим символом последовательности, Блок 3 памяти имеет емкость и х 1 и предназначен для хранения признаков цикла. Единичный признак цикла разрешает провести повторный цикл сравнения, в котором поступивший символ последовательности сравнивается с элементом эталонной последовательности, адрес которого считан их блока 2 памяти, Регистр 4 предназначендля хранения кода количества элемен-. тов эталонной последовательности.

Устройство работает следующим образом.

В исходном состоянии(цепи установки узлов устройства в исходное состояние не показаны счетчик 13 обнулен. Пусть в потоке входных символов необходимо обнаружить последовательность из трех символов: А,А, С. Тогда в блоках 1-3 памяти прошивается следующая информация:

lQ

35

Формула

5 158 на время срабатывания блоков 1 "3 памяти и схемы Il сравнения.

Если символ, записанный в регистр

5, является символом А, то на выходе схемы li сравнения появляется единичный сигнал, который поступает на второй вход элемента И 8 и инверсный вход элемента И 9. При этом на выхо" де элемента И 8 появляется сигнал, который поступает на счетный вход счетчика 13 и тактовый вход схемы 12 сравнения, Передний фронт этого сигнала увеличивает содержимое счетчика 13 на единицу, На выходе схемы

12 сравнения сигнала нет, так как содержимое регистра 4 (двоинный код

11) не совпадает с содержимым счетчика 13 (двоичный код 01). Таким об„разом, устройство подготовлено к приему следующего символа анализируемой последовательности.

Если следующий символ, поступивший на вход 16, является символом А, т.е. совпадает с вторым элементом эталон- ной последовательности, то, устройство работает так же, как и при анализе первого входного символа. В результате на счетчике 13 формируется двоичный код 10.

Если третий символ, поступивший на вход 16, является символом С, т,е. совпадает с третьим элементом эталонной последовательности, то сигналом с выхода элемента И 8 на счетчике 13 формируется двоичный код 11. Этот код поступает на первый вход схемы 12 сравнения, второй вход которой соединен с выходом регистра 4. Так как регистр 4 также хранит двоичный код 11, то по приходу сигнала на тактовый вход схемы 11 сравнения она на своем выходе вырабатывает сигнал. Этот сигнал поступает на вход начальной установки счетчика 13, обнуляя его, и на выход 15 устройства, сообщая о том, что во входном потоке символов обнаружена последовательность, совпадающая с с эталоннойъ

Ясли третий символ, поступивший на вход 16,не является-символом С,т.е. не совпадает с третьим элементом эталонной последовательности, то на выходе схемы I! сравнения появляется нулевой сигнал, а..сигнал с выхода элемента 7 задержки проходит через эле-. мент И 9. С выхода элемента И 9 сигнал поступает на вход записи счетчика 13 и записывает в него двоичный код 01

3940 6 считанный из третьей ячейки блока 2 памяти. Кроме того, этот сигнал постуА пает на второй вход элемента И 10, на первый вход которого поступает l считанная из третьей ячейки блока 3 памяти. На выходе элемента И 10 появляется сигнал, который поступает на второй вход элемента ИЛИ 6. Последний вырабатывает на своем выходе сигнал, в результате этого в устройстве запускается цикл сравнения третьего символа из входной последовательности с вторым элементом A эталонной последовательности. Это необходимо, так как третий символ из входной последовательности может быть элементом А, а четвертый символ — элементом С. Тог" да второй, третий и четвертый входные символы образуют последовательность, совпадающую с эталонной.

Если третий входной символ не сравнится и с вторым элементом эталонной последовательности, то в счетчик 13 запишется двоичный код 00 из второй ячейки блока 2 памяти, а "0", считанный из второй ячейки блока 3 памяти, не пропустит сигнал с выхода элемента

И 9 через элемент И 10.

Таким образом, устройство возвращается в исходное состояние и анализ четвертого входного символа производится аналогично анализу первого входного символа, изобретения

Устройство для регистрации последовательности данных, содержащее три блока памяти, счетчик адреса, первый элемент И и элемент ИЛИ, выход элемента ИЛИ соединен с входами считывания первого, второго и третьего блоков памяти, информационные выходы счетчика адреса соединены с адресными входами первого, второго и третьего блоков памяти, выход первого элемента И соединен со счетным входом счетчика адреса, о т л и ч а ю щ е— е с я тем, .что, с целью упрощения, устройство содержит регистр длины последовательности, регистр входного: символа последовательности, первую,и вторую схемы сравнения, второй и третий элементы И и элемент задержки, причем тактовый вход устройства соединен с первым входом элемента ИЛИ и входом записи регистра входного символа последовательности, - выход которо-:

158394

Ъ

Составитель И. Сигалов .Шулла Техред Л.Сердюкова Корректор А.Осауленко.Редактор И факаз 2256 Тираж 570 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035 ° Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород,,ул. Гагарина, 101

7 го соединен с первым входом первой схемы сравнения, вход анализируемой последовательности устройства соединен с информационным входом регистра входного символа последовательности, выход элемента ИЛИ через элемент задержки соединен с первым входом первого элемента И и первым входом второго элемента И, выход которого соеди- 10 нен с входом записи счетчика адреса и . первым. входом третьего. элемента И, информационный выход первого блока памяти соединен с вторым входом пер-. вой схемы сравнения, выход которой r соединен с инверсным входом второго элемента И и вторым входом первеге в элемента И, выход которого соединен с тактовым входом второй схемы срав*ения, информационные выходы Второго и третьего блоков памяти соединены соответственно с информационным входом счетчика адреса и вторым входом третьего элемента И, выход которого соединен с вторым входом элемента

ИЛИ, информационные выходы счетчика адреса и регистра длины последовательности соединены соответственно с первым и вторым входами второй схемы сравнения, выход которой соединен с входом начальной установки счетчика адреса и является выходом признака конца регистрации устройства.