Цифровой синтезатор частоты

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и может быть использовано для формирования сетки частот. Целью изобретения является уменьшение уровня дискретных паразитных составляющих в спектре выходного сигнала. Синтезатор содержит накопительный сумматор (НС) 1, генератор 2 случайных чисел, сумматоры 3 и 4, блок 5 памяти, ЦАП 6 и ФНЧ 7. Текущая фазовая ошибка ε на выходе НС 1 имеет квазипериодический характер и в зависимости от кода управления A дискретные паразитные составляющие отстоят от несущего колебания на частоты, кратные шагу перестройки частоты синтезатора. Путем периодического добавления случайного числа X в сумматор 4 можно нарушить периодичность фазовой ошибки, разрушив дискретный характер сигнала, т.е. происходит уменьшение уровня дискретных паразитных составляющих благодаря увеличению их количества при неизменной суммарной мощности. 1 ил.

СОН..З СОВЕТСКИХ

СОЦИАЛИС ИЧЕСКИХ

РЕСПУБЛИК (я)5 Н 03 В 19/00

ГОСУДАРСТВЕННЫ И КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4428782/24-09 (22) 23.05.88 (46) 07.08.90. Бюл. ¹ 29 (72) M.Ô.Êóäðÿøîâ и С.Н.Гертель (53) 621.373.42 (088,8) (56) Авторское свидетельство СССР № 1188845, кл. Н 03 В 19/00, 29.03.84.

Гнатек. Ю.P. Справочник по цифроаналоговым и аналого-цифровым преобразователям. — М.: Радио и связь, 1982, с. 255. (54) ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТЫ (57) Изобретение относится к радиотехнике и м.б, использовано для формирования сетки частот, Целью изобретения является уменьшение уровня дискретных паразитных составляющих в спектре выходного сиг„„5U„„1584065 А1 нала. Синтезатор содержит накопительный сумматор (НС) 1, генератор 2 случайных чисел, сумматоры 3 и 4, блок 5 памяти, ЦАП 6 и ФНЧ 7, Текущая фазовая ошибка E на выходе НС 1 имеет квазипериодический характер и в зависимости от кода управления

А дискретные паразитные составляющие отстоят от несущего колебания на частоты, кратные шагу перестройки частоты синтезатора. Путем периодического добавления случайного числа Х в сумматор 4 можно нарушить периодичность фазовой .ошибки, разрушив дискретный характер сигнала, т.е. происходит уменьшение уровня дискретных паразитных составляющих благодаря увеличению их количества при неизменной суммарной мощности. 1 ил.

1584065

Изобретение относится к радиотехнике

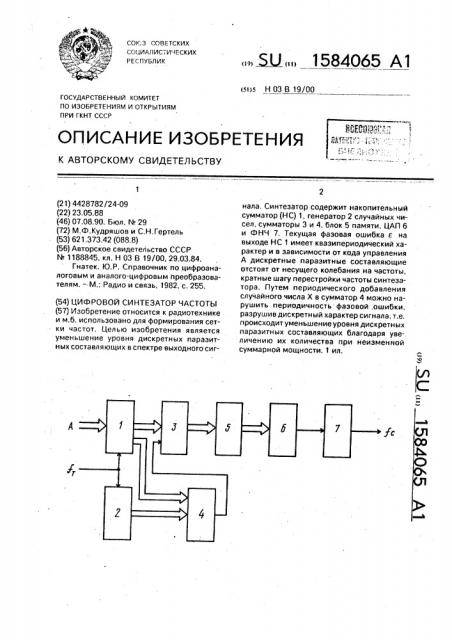

| и может использоваться для формирования сетки частот, Целью изобретения является уменьшение уровня дискретных паразитных состав- 5 ляющих в спектре выходного сигнала, На чертеже приведена структурная электрическая схема цифрового синтезатора частот.

Цифровой синтезатор час-.от содержит 10 накопительный сумматор 1, генератор 2 случайных чисел, первый 3 и второй 4 сумматорь., блок 5 постоянной памяти, цифроаналоговый преобразователь 6 и фильтр 7 нижних частот. 15

Цифровой синтезатор частот работает следующим образом.

На накопительный сумматор 1 поступает и-разрядный двоичный код синтезируемой частоты А = ai2 + ар2 + ... + ал2", 20 пропорциональный отношению синтезируемой f и тактовой 1т частот(А = И fc/ft ,N = 2"). С частотой тактовых импульсов ft в накопительном сумматоре 1 вычисляется текущая фаза выходного сигнала. 25

На выходах накопительного сумматора

1 в каждый тактовый момент времени тк =

=KT, К = О, 1, 2, 3 (Т = 1/fT — длительность тактового периода) формируется код фазы

ВК синтезируемого колебания по следую- 30 щему алгоритму: Вк+1 — Вк+ А, при этом Вр начальное состояние накопительного сумматора 1. I-раз рядн ый код с выхода старших разрядов накопительного сумматора 1, причем > 2, обычно =- 3 — 8, поступает на 35 первый сумматор 3, а m-разрядный код с выхода младших разрядов на второй сумматор 4, на второй вход которого поступает

m-разрядный код от генератора 2 случайных чисел. ао

Генератор 2 случайных чисел с тактовой частотой 1т формирует случаиные числа Х в диапазоне 0 X (2 -1). Сигнал с выхода переноса второго сумматора 4 поступает на второй вход первого сумматора 3, 1-разряд- 45 ный код фазы с выхода первого сумматора

3 поступает на вход блока 5 постоянной памяти, из которого выбирается число, про- порциональное амплитуде выходного сигнала при данной фазе, С помощью 50 цифроаналогового преобразователя 6 выбранное число преобразуется в напряжение. Для выделения первой гармоники после цифроаналогового преобразователя

6 включается фильтр 7 нижних частот. 55

В случае цифрового синтеза колебаний имеет место ухудшение спектральной чистоты выходного сигнала, обусловленное шумами квантования фазы, Эти шумы определяются разрядностью числа поступа ющего на вход блока 5 постоянной памяти.

Если емкость накопительного сумматора 1 определяется и-разрядным числом, а для блока 5 постоянной памяти используется

l0flbKo 1-разрядный выход старших разрядов накопительного сумматора 1, то m-разрядный выход младших разрядов (m = и-I) образуют текущую фазовую ошибку е, которая распределена в диапазоне 0 к < 2

Эта ошибка имеет кваэипериодический характер и в зависимости от кода управления

А дискретные паразитные составляющие отстоят от несущего колебания на частоты кратные шагу перестройки частоты синтезатора. Путем периодического добавления случайного числа Х в сумматор 4 можно нарушить периодичность фаэовой ошибки, разрушив таким обоазом дискретный характер образующего спектра.

Генератор 2 случайных чисел с тактовой частотой fl формирует случайные числа Х из равномерно распределенного ряда в диапазоне О Х < 2 . m-разрядные числа X u к суммируются в m-разрядном втором сумматоре 4, сигнал переноса которого суммируется с I-разрядным числом на разрядном выходе старших разрядов накопительного сумматора 1. На выходе второго сумматора

4 сигнал равен нулю, если Х + к < 2, или

0 < Х< 2 -t .,так как Х > О, Следовательно, на выходе первого сумматора 3 код текущей фазы имеет ошибку, определяемую младшими разрядами накопительного сумматора 1. Эта ошибка, P1= Е.

На выходе переноса второго сумматора 4 появляется сигнал, равный единице, если Х вЂ” E > 2 или 2" > X > 2"-с (так как

Х < 2 ) .Следовательно, к коду текущей фазы накопительного сумматора 1 определяемого его разрядным выходом старших разрядов, т. е. к I-разрядному числу подсуммирована единица. В этом случае код текущей фазы на выходе первого сумматора 3 имеет ошибку, равную р =2 — e, так как

X случайное число с равномерным распределением, вероятность того, что на выходе переноса второго сумматора 4 сигнал равен нулю, равна

2 — ŠF, P(P1 = 2 - =-1 --.-

Ф азова я ошибка в этом случае

P1 = — Г.

Вероятность того, что на выходе переноса второго сумматора 4 появляется сигнал, равный единице:

1584065

Составитель А.Мышакин

Техред M.Ìîðãåíòàë Корректор И.Муска

Редактор М. Бланар

Заказ 2262 Тираж 653 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

P = —.

Е

Фазовая ошибка в этом случае

„щ =2 — я.

Математическое ожидание . фазовой зшибки (т,е. ее средняя величина) м (.rp ) = Р!Рр! + p2 РР2 =

= — с(1 — — ) + (2 — е) — =О.

2 2

Это означает, что средняя величина фазовой ошибки на выходе второго сумматора

3 равна нулю, что соответствует точному вычислению текущей фазы. А тот факт, что 15 фазовая ошибка в моменты прихода тактовых импульсов меняется по случайному закону. представляет собой явление фазового шума. Таким образом, происходит уменьшение уровня дискретных паразитных со- 20 ставляющих благодаря увеличению их количества при неизменной суммарной мощности.

Формула изобретения

Цифровой синтезатор частоты. содержащий последовательно соединенные блок постоянной памяти, цифроаналоговый преобразователь и фильтр нижних частот, накопительный сумматор, отличающийся тем, что, с целью уменьшения уровня дискретных паразитных составляющих в спектре выходного сигнала, введены первый и второй сумматоры и генератор случайных чисел, при этом разрядный выход старших разрядов накопительного сумматора соединен с первым входом первого сумматора, второй вход которого соединен с выходом переноса второго сумматора, разрядный выход младших разрядов накопительного сумматора соединен с первым входом второго сумматора, второй вход которого соединен с выходом генератора случайных чисел,.тактовый вход которого соединен с тактовым входом накопительного сумматора, а выход первого сумматора соединен с входом блока постоянной памяти.