Устройство для свертки кода фибоначчи

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для свертки кода Фибоначчи с контролем. Цель изобретения состоит в расширении функциональных возможностей за счет обнаружения ошибок, возникающих в результате сбоев и отказов элементов. Устройство содержит группу блоков 1 свертки, элемент ИЛИ 2, формирующий сигнал ошибки при неправильном выполнении операции свертки, а каждый блок 1 свертки содержит триггеры 17 и 18, элемент И 19, первый и второй элемент ИЛИ 20 и 21, элемент ИЛИ-НЕ 22. 1 з.п. ф-лы, 2 ил.

СОЮЗ СОВЕТСНИХ

СОИИАЛИСТИЧЕСНИХ

РЕСПУБЛИК ((9> SU (((l

А1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И OTHPblTHRM

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ASTOPCHOMY СВИДЕТЕЛЬСТВУ

+U8 . 2 (21) 4600640/24-24 (22) 31. 10.88 (46) 15.08.90, Бюл. У 30 (71). Специальное конструкторско-технологическое бюро "Модуль" Винницкого политехнического института (72) А. П. Стахов, В. А. Лужецкий, В. Г. Ваховский, В. В. Коротин и И. M. Нопович (53) 68 1.3(088 .8) (56) Авторское свидетельство СССР

В 1392554, кл..Н 03 M 7/30, 1986 °

Авторское свидетельство СССР

У 842782, кл. Н 03 М 7/30, 1979. е ц)5 Н 03 М 7/30, 6 06 F.: 1 4 /00

-.:-: 1! (2 (54) УСТРОЙСТВО ДЛЯ СВЕРТКИ КОДА ФИБОНАЧЧИ (57) Изобретение относится к вычислительной технике и предназначено для свертки кода Фибоначчи с контролем.

Цель изобретения — расширение функциональных возможностей за счет обнаружения ошибок, возникающих в результате сбоев и отказов элементов. Устройство содержит группу блоков 1 сверт.ки, элемент ИЛИ 2, формирующий сигнал ошибки при неправильном выполнении операции свертки, а каждый блок 1 свертки — триггеры 17 и 18, элемент

И 19, первый и второй элемент ИЛИ 20 ц 21, элемент ИЛИ-НЕ 22. 1 s.ï. ф-лы, 2 ил.

1585901

Изобр;тение относится к вычисли-" тельной технике и может быть использонова для свертки кодов Фибоначчи.

Пельш изобретения является расши5 речие функциональных возможностей за счет обнаружения ошибок, возникающих в результате сбоев и стказов элементов.

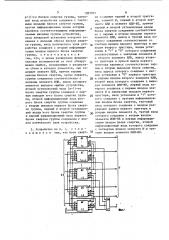

На фиг. 1 изображена структурная 1g схема устройства для свертки кода

Фибоначчи (для р = 1); на фиг. 2— функциональная "хема L1nQKG, свертки, ."стро" ..ство (фиг„ 1) содержит группу блоков свертк; 1. 1- 1.п, =лемент f5

И)И 2, гоуппу информационных выходов

3 усгро- тва, тактовьй вход 4 устройства, группу информационных вхсдов 5 устроиства, вход о начальной установ-. ки устрсй.".тва, выход 7 ошибки устрой- 20 ства и рвый и зторой уста,:.овочпые входы 8 и 9 блока 1 свертки группы, первый и второй информационные входы ,10 и 11 блока 1 свертки группы, тактовь;й вход 12 блока 1 свертки группы, 25 третий и нф. рмасасо нпьй вход 13 блс ка

1 свертк:;" группы, вход 14 сброса блока 1 сверт.си группы> первый и второй выходы 13 ., 16 блока 1 свертки группы.

Блок 1 св ертки (фиг „2) содержит первый и второй триггеры 17 и I8„. элемент:," 9., первый i : второй элементы 1ПИ 20 и 21 и элемент ИЛИ-HL 22.

Устройство (фиг. I ) работает сгледующим о бр а з ом „

Перед началом работы поцачей единичного сигнала на вход 6 устройства триггеры всех блоков 1 свертки устанавливаются в нулевое состояние, После записи в триггеры 17 п-разрядного кода исходной информапии,. пода".асмого на входы 13 блоков 1 свертки,, устройств- гатовс к рабсте, В сл < ее если #op, записанньй B триггерах 17 блоков 1., 1. (i-1) и

1. (1 2) cBFpTicH удовлетворяе f условию свертки, т.е. он равен "011", по приходу ча вход 13 синхроимпульс=! на выходе элемента И 19 блока 1.1 сверт ки формируется единичньй сигнал, ко.торый, поступая на вход установки в триггера 18 этого блока свертки, переводит его в единичное состояние.

Единичньй сигнал с прямо-а выхо-" да триггера 18 блока 1. i сверт«:55 ки nîñ. Упает на соответствуюшие входы элементов ИЧИ 20 блоков

1., 1, (i — 1) и I . (i--2) свертки, а с Bblxopов элементов ИЛИ 20 — на счетные входы триггеров 17 этих блоков свертки. Эти триггеры по заднему фронту того же синхроимпульса изменя ют свое состояние на противоположное.

При правильном переключении триг»герьг 17 блоков 1. i, 1.(i-1) и 1.(i2) свертки переходят в состояние

"100". Это свидетельствует о правильном выполнении операции свертки исходного кода, записанного в этих триггерах. После этого на выходах элемента

ИЛИ-HF. 22 блока 1.i свертки появляется единичный сигнал, который через элемент ИЛИ 21 поступает на вход установки в "0" триггерА 18 блока этого блока свертки и сбрасывает его в исходное нулевое состояние, В случае переключения триггеров

17 блоков 1.i, 1. (i-1) и 1. (i-2) свертки в состояние "000", "001", "010" "011" "101 ™ 110" или "111"

9 Э 9 являющееся результатом неправильного ьыполнения операции свертки исходного кода, на вьссоде элемента ИЛИ-НЕ 22 блока 1. 1 свертки присутствует нулевой сигнал, который поступаетчерез элемент

ИЛИ 21 на вход установки в "0" триггера 18 этого блока свертки. В резуль" тате триггер 18 блока 1.1 Свертки остается в единичном состоянии и единичньй сигнал с его прямого выхода через элемент ИЛИ 2 поступает на выход 7 устройства, с которого через фиксированное время с момента поступления импульса на вход 12, равное времени свертки, считывается единичный сигнал ошибки. В случае правильного выполнения операции свертки на всех входах элемента ИЛИ 2 и на выходе 7 устройства в указанное время присутствуют нулевые сигналы.

Формула изобретения

Устройство для свертки кода

Фибоначчи., содержащее группу блоков свертки„причем первый выход 1 Fo блока свертки группы (i = 1-n, n— количество разрядов кода) соединен с первым установочным взводом (i-1)-ro и вторым установочным входом (1-р-1)гQ блоков свертки группы (р = 1 2 ° ° ° ) второй вьпсод i-го блока свертки rpyqпы является i — è информационным выходом группы устройства и соединен с первым информационным входом (i+1)-го и вторым информационным входом (i +

15859

p+1)-го блоков свертки группы, такто- вый вход устройства соединен с тактовыми входами блоков свертки группы, третьи информационные входы которых являются соответствующими информаци5 онными входами группы устройства, вход начальной установки которого соединен с входами сброса блоков свертки группы, вход логического нуля устройства соединен с вторым информационным входом первого блока свертки группы, о т л и ч а ю щ е е с ятем, что, с целью расширения функциональных возможностей за счет обнаружения ошибок, возникающих в результате сбоев и отказов элементов, оно содержит элемент ИЛИ, причем первые выходы блоков свертки, кроме первого, группы соединены соответственно с 20 входами элемента ИЛИ, выход которого является выходом ошибки устройства, второй установочный вход (n-1)-ro блока свертки группы соединен с пер-. вым выходом n-ro блока свертки груп- 2 пы, второй информационный вход второго блока свертки группы соединен с вторым выходом первого блока свертки группы, первый и второй установоч; ный входы и-го блока свертки группы и первый информационный вход первого блока свертки группы соединены с входом логического нуля устройства, 2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что блдк сверт- З5

01 ки содержит первый и второй триггеры, элемент, И, первый и второй элементы ИЛИ и элемент ИЛИ-НЕ, причем. первый и второй установочные входы блока свертки соединены соответствен но с первым и вторым входами первого элемента ИЛИ, выход и третий вход которого соединены соответственно со счетным входом первого триггера и выходом второго триггера, входы уста-. новки в "1" и "0" которого соединены соответственно с выходами элемента И и второго элемента ИЛИ, выход- второго триггера и прямой выход первого триггера являются соответственно перзым и вторым выходами блока свертки, вход адреса которого соединен с входом установки в "0" первого триггера и первым входом второго элемента ИЛИ, второй вход которого соединен с выходом элемента ИЛИ-НЕ, первый вход которого соединен с первым входом элемента И и инверсным выходом первого триггера, вход установки в "1" которого соединен с третьим информационным входом блока свертки, тактовый вход которого соединен с входом разрешения записи первого триггера и вторым входом элемента И, третий вход которого соединен с вторым входом. элемента ИЛИ-НЕ и первым информаци- онным входом блока свертки, второй информационный вход которого соединен с четвертым входом элемента И. и третьим входом элемента ИЛИ-НЕ,