Устройство для умножения двоичных чисел

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и позволяет выполнить умножение чисел в последовательном коде. Цель изобретения - сокращение аппаратурных затрат. В предлагаемое устройство, содержащее регистры множимого 3 и множителя 4, группу элементов И 5, блок сложения 6 и триггер 1, введен триггер 2, что позволяет использовать вместо двух групп элементов И одну и записывать разряды множителя в регистр множителя с задержкой в полтакта, а не такт, что в свою очередь повышает быстродействие устройства. 3 ил.

СОЮЗ СОНЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (!9) {!!) 498 А1 (S1)S Г 06 Е 7/52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ П.(НТ СССР

1 (21) 4412658/24-24 (22) 21 ° 04,88 (46) 23.08.90. Вил. 1> 31 (71) Одесский политехнический институт (72) А.В. Дрозд, Е.Л. Иолин, В.H Огинский, E.A. Родись и 1(.Р>. Дрозд (53) 681.325 (088.8) (56) Авторское свидетельство СССР

h 656056, кл. G 06 Е 7/38, 1976.

Авторское свидетельство СССР

М 441563, кл. G 06 Е 7/44, 1972, (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ДВОИЧНЫХ ЧИСЕЛ

2 (57) Изобретение относится к вычислительной технике и позволяет выполнить умножение чисел в последовательном коде. Цель изобретения сокращение аппаратурных затрат, В предлагаемое устройство, содержащее регистры множимого 3 и множителя 4, группу элементов И 5, блок сложения

6 и триггер 1, введен триггер 2, что позволяет использовать вместо двух групп элементов И одну и записывать разряды множителя в регистр множителя с задержкой в полтакта, а не такт, то в свою очередь повышает быстродействие устройства. 3 ил, 1587498

Изобретение относится к вычислительной технике и может быть исполтзовано для выполнения арифметических действий.

Пель изобретения — сокращение аппаратурных затрат.

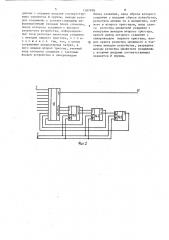

11а фиг.l представлена функциональная схема устройства для случая n=S; на фиг.2 — пример реализации блока сложения; на фиг.3 — временные диаграммы работы устройства.

Устройство (фиг.l) содержит пер— вый 1 и второй 2 триггеры, регистры множимого 3 и множителя 4, элементы

И 5.1-5.8 группы, блок 6 сложения, вход 7 множимого устройства, вход

8 множителя устройства, тактовый вход 9 устройства, вход 10 сброса устройства, выход 1! результата устройства и тактовый выход 12 устройства. Блок сложения (фиг.2) содержит многовходовой одноразрядный сумматор

l3 и регистры 14.1-14.3 группы.

Устройство работает следующим обра-25 зом.

Па вход 10 сброса устройства поступает импульс, определяющий начало работы. Этот импульс сбрасывает в ноль триггеры 1 и 2,регистры 3 и 4 30 и регистры блока 6 сложения, Па тактовый вход устройства поступают спнхроимпульсы СИ1 типа Меаттдр, тактирующие работу у стройства. Отттт ттодаются на счетный вход триттгера 2, который на прямом и инверсном выходах формирует соответственно прямое и инверсное значение синхросигналов СИ2 (фиг.3). Прямое значение синхрс сигналов СИ2 выдается на тактовый выход устройства для синхронизации приема сомножителей. На входы 7 и 8 множимого и множтттеля с частотой следования синхроимпульсов СИ2 поступают в последовательном коде разряды, начиная с первого — младшего, множимого и множителя соответственно.

Под действием синхроимпульсов СИ2, поступающих на вход сдвига регистра

3 множимОГО разряды мттожттмого прОд 50 вигаются в каждом такте в регистре

3 множимого на одпу позиттттто Е3 сторону старших разрядов. Разряды множителя вдвигаются в регистр 4 множителя чеРез триггер 1, в который Разря ды записываются по синхросигналам

СИ2, а в регистр 4 множителя вдвига— ются по инверсным синхросигналам

СИ2 с задержкой на полтакта (фит .3), на одну позицию в сторону младших разрядов регистра 4 множтттеля.

При этом на выходах регистров

3 и 4 формируются последовательности разрядов множимого и множителя в соответствии с временными диаграммами. Числа, указанные на времетитых диаграммах выхода в раз рядов регистров 3 и 4, означают номера разрядов множимого и множителя, причем младшему разряду соответствует номер

1, а старшему номер 8 °

Под действием указанных последовательностей разрядов множимого и множи.теля иа выходах элементов 5 группы формируются последовательности конъюнкций, отображенных на соответствующих временных диаграммах двухразрядными

1 кодами, которые соответственно являтотся номерами разрядоп множпмого и множителя, формируемыми элементами И группы. При этом на выходах элементов

И 5. 1-5. 8 группы формируются коттъюттко т а ции с весовыми функциями 2, 2, 2

2 . Эти конъюнкции поступают на входы блока сложения, который в каждом такте с частотой синхронизации

СИ! складывает поступающее с выходов элементов И группы 5 коттъюнкции с учетом сигналов переносов с предыдущих тактов, задержанных на регистрах

14 группы, причем сигнал переноса с первого выхода переноса многовходового одноразрядного сумматора 13 за;,ерживается íа один такт на регистре

14 l.группы, сигнал переноса задерживается на два такта на первых двух регистрах 14.1 и 14.2 группы и т.д.

В результате сложения конъюнкций тта выходе блока б сложения формируется очередной разряд результата, который таким образом ттоступает на выход 11 устройства в последовательттотт коде.

Форм улан зобретени я

Устройство для умножения двоичных чисел, содержащее регистры множимого и множителя, группу элементов

И, блок сложения и первый триггер, информационный вход которого .соединен с входом множителя устройства, вход множимого которого соединен с информационным входом регистра множимого, разрядные выходы которого сое5 15 динены с первыми входами соответствующих элементов И группы, выходы которых соединены с соответствующими индюрмационными входами блока сложения, выход которого соединен с вы;оро» результата устройства, и формационный вход регистра множителя соединен с выходом первого триггера, о т л ич а ю щ е е с я тем, что, с целью сокращения аппаратурных затрат, в него введен второй триггер, счетный вход которого соединен с тактовым входом устройства и синхровходом

87498 б блока сложения, вход сброса которого соединен с входами сброса устройства, регистров множим го и множителя, пер5 вого и второго триггеров вход сдвига реги стра множителя соединен с инверсным выходом второго триггера, прямой выход которого соединен с синхровходом первого триггера, входом сдвига регистра множимого и тактовым выходом устройства, разрядные выходы регистра множителя соединены с вторыми входами соответствующих элементов И группы.

Риг.2

9ã.10

Вх. У

Вх,7,8

Выход

Вых.1м йа2м.5

888д .3

Й х 4 ля

Вых5эл5

Вых Е8л.г

Вьи. 78л 5

Йи.дзл 3 йа.Э1.2

ВыхВзл4

Вых7у, 4

Вых.6у 4 йа58,,1 4

Вых.4эл4

Вых.5 и Ф

Bblx.Z зл 4

BbN 1Щ ff

Вых.эл 55 й/х. м 54

Вых. ю5.6 йи. зл.55

Вых. м 5.7 йв м.52 йа.м 58

Вых. эл.5,1

ВЫх. 17

6 7 8.Г

5 6 7 8

2 ф 6 7

7 2 3 Ф 5 6 7 8

1 2 3 Ф 5 6 7 8

7 2 3 9 5 . 6 7 8

1 2 3 4 5 6 7 8

1 2 3 5 7 d

6 7 8

5 6 7 8

Ц 6 7 8

Ф 5 б 7 8

5 б 7 d

5 б 7 8 г

6 7 8

1 2 3 9 5 б

11 12 22 13 33 3 С Ч5 55 5666 7 77 78 88

21 31 32 Ô2 43 53 Я 4 Ф 65 75 76 86 д7

1 1 2v 2 Л ЛБФБФ73 56Б6

41 51 52 62 6 3 73 7Ф д 83

/5 16 26 77 37 38 ФВ

61 71 72 Вг 83

28 гк 272 222 2 г 321

Фиг 5

Составитель E. Г1урзина

Редактор Н. Яцола Техред M.Цидьис Корректор Т. Г1алец

Заказ 2420 Тираж 566 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГЕНТ ГССР

113035, Москва, Ж-3), Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул, Гагарина, 101