Устройство для регенерации динамической памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств на основе элементов полупроводниковой динамической памяти. Цель изобретения - повышение быстродействия устройства. Устройство содержит блок 1 синхронизации, счетчик 2 регенерации, коммутатор 4 адреса, блок 5 памяти, регистр 6, приоритетный шифратор 7, коммутатор 8, триггер 9. В устройстве запоминаются признаки внешних обращений по строчным адресам, а затем при регенерации производителя опрос строчных адресов в соответствии с этими признаками, а незадействованные строчные адреса из процесса регенерации исключаются. 1 з.п. ф-лы, 6 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 G 11 С 21/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

° а

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Ф (21) 4492769/24-24 (22) 10.10.88 (46) 23.08,90; Бюл. М 31 (71) Львовский политехнический институт им.Ленинского комсомола (72) И.Б,Боженко и О,К.Мешков (53) 681.329 (088.8) (56) Авторское свидетельство СССР

N. 1198474, кл. G 11 С 21/00, 1985.

Авторское свидетельство СССР

N. 1251183, кл. G 11 С 21/00, 1986. (54) УСТРОЙСТВО ДЛЯ РЕГЕНЕРАЦИИ

ДИНАМИЧЕСКОЙ ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть использовано при Ы 1587594 А1 построении запоминающих устройств на основе элементов полупроводниковой динамической памяти. Цель изобретения— повышение быстродействия устройства. Устройство содержит блок 1 синхронизации, счетчик 2 регенерации, коммутатор 4 адре. са, блок 5 памяти, регистр 6, приоритетный шифратор 7, коммутатор 8, триггер 9. В устройстве запоминаются признаки внешних обращений по строчным адресам, а затем при регенерации производителя опрос ! строчных адресов в соответствии с этими признаками, а незадействованные строчныее адреса из процесса регенерации исключаются. 1 з.п.ф-л ы, 6 ил.

1587594

10

25

55

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств на основе элементов полупроводниковой динамической памяти„

Цель изобретения — повышение быстродействия устройства.

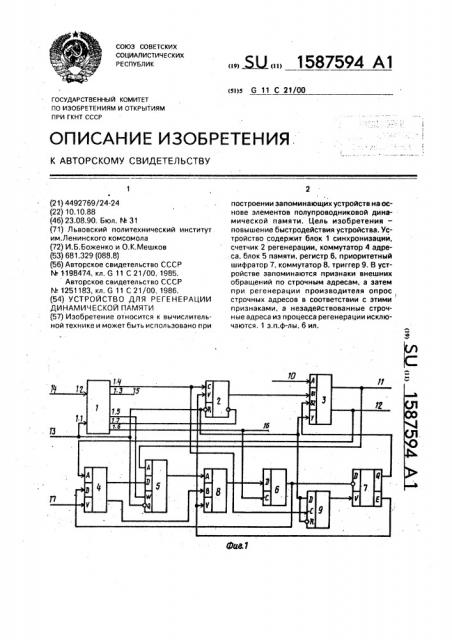

На фиг. 1 представлена функциональная схема устройства; на фиг, 2 — функциональная схема преобразователя кода адреса; на фиг, 3 — функциональная схема блока синхронизации; на фиг. 4 — временная диаграмма работы устройства; на фиг. 5 и 6— временные диаграммы работы устройства в режимах внешнего обращения и регенерации соответственно, Устройство (фиг.1) содержит блок 1 синхронизации, счетчик 2 регенерации, адресный коммутатор 3, преобразователь 4 кода адреса, блок 5 памяти, регистр 6, приоритетный шифратор 7, второй коммутатор 8, триггер 9, адресный вход 10, первый 11 и второй 12 адресные выходы, вход 13 запроса на регенерацию, стробирующий вход 14, выход 15 окончания регенерации, выход 16 стробирования и вход 17 начальной установ:ки.

Преобразователь 4 кода адреса (фиг.2) содержит дешифратор 18, элементы И 19, элементы 20 эквивалентности, элементы

ИЛИ 21.

Блок 1 синхронизации в реализованном варианте предлагаемого устройства (фиг,3) содержит элементы ИЛИ 22 и И 23, триггеры 24 и 25, синхрогенератор 26 и регистр 27 сдвига.

На фиг. 4 обозначены: а — выход синхрогенератора 26, б — сигнал запроса на регенерацию с входа 1.1, в — сигнал стробирования на входе 1.2, r — выход триггера 25, д-з — соответственно выходы первого — четвертого разрядов регистра 27, и — выход переноса счетчика 2 на входе 1.7, к — состояние триггера 24.

На фиг, 5 и 6 обозначены: а — сигнал запроса на регенерацию на входе 13, б — r— первый — третий синхросигналы с блока 1, д —, выход запроса шифратора 7, е — старшие разряды строчных адресов на выходе 11, ж— младшие разряды строчных адресов на выходе 12, з — к — соответственно первый, второй и седьмой выходы дешифратора 18 преобразователя 4, л — н — соответствующие . разряды блока 5 памяти, о — р — соответству. ющие разряды регистра 6, с — выход переноса счетчика 2.

Устройство преднаэнаяено для адресации динамической памяти по 128-ми строчным адресам, Счетчик 2 выполнен на основе микросхемы К555ИЕ10,коммутаторы 3,8— на К555КП11, блок 5 памяти представляет собой матрицу 7 х 16, выполненную на основе микросхем К155РУ2. Регистр 6 выполнен на К555ТМ9, шифратор 7 — на К155ИВ1, регистр 27 — на К555ИР16. Прочие узлы устройства также выполнены на основе серии

К555.

Устройство работает следующим обра-зом, Синхрогенератор 26 генерирует импульсы (фиг.4а), поступающие на синхровход регистра 27 сдвига. Режим внешнего обращения задается уровнем "0" на входе

13 (фиг,4б). Внешние строчные адреса сопровождаются стробирующими импульсами (фиг.4в), поступающими с входа 14 через вход 1.2 и элемент ИЛИ 22 на установку триггера 25 (фиг.4г), По состоянию "1" триггера 25 регистр 27 переходит из режима установки в режим сдвига и с его выходов поступают синхроимпульсы на выходы 1.4—

1,6 (фиг,4д-ж), По сигналу с четвертого разряда регистра 27 (фиг,4з) триггер 25 сбрасывается, регистр 27 вновь переходит в режим установки, его первый разряд устанавливается в "1" (фиг. 4д), а прочие — в "0".

При этом сигнал, поступающий с выхода 1.6 на выход 16 (фиг.4ж) используется как сигнал подтверждения приема адреса.

Режим регенерации задается уровнем

"1" на входе 13. По нему триггер 25 переводит регистр 27 в режим сдвига, а элемент И

23 блокирует сброс триггера 25 по сигналу с четвертого разряда регистра 27, и синхроимпульсы генерируются непрерывно. По окончании регенерации счетчик 2 выдает сигнал переноса (фиг,4и), который своим положительным фронтом через вход 1.7 устанавливает триггер 24 (фиг.4к) и его состояние через выход 1,3 поступает на выход 15 как сигнал окончания регенерации.

По нему запрос на выполнение регенерации сбрасывается, и,соответственно, сбрасываются триггеры 25 и 24; регистр 27 вновь перехо„ит в режим установки.

При включении питания для установления рабочего режима динамической памяти необходимо провести до десяти циклов регенерации, Для этого осуществляется внешнее обращение по всем строчным адресам.

Одновременно на вход 17 подается сигнал начальной установки. По нему на выходах элементов ИЛИ 21 преобразователя 4 уста-навливаются "1" и они заносятся во все ячейки блока 5 памяти.

По окончании начальной установки и состоянии "0" на входе 13 (фиг.5а) осуществляется внешняя загрузка памяти, сопровождаемая генерацией синхросигна1587594 лов (фиг,5б-г). Строчные адреса (фиг. 5е,ж) поступают к входу 10, который коммутатор

3 подключает к выходам 11 и 12. Младшие адреса с выхода 12 поступают на адресный вход преобразователя 4, где дешифратор

18 преобразует их в унитарный код, в котором "0" соответствует текущему адресу (фиг.5 з-к). Элементы И 19 складывают этот код с кодом состояния регистра 6 и результат через элементы ИЛИ 21 поступает на информационный вход блока 5 памяти, в котором записывается по сигналу 1.5 по адресу, заданному на выходе 11 (фиг, 5л-н).

Затем по сигналу 1.6 этот код заносится в регистр 6(фиг. 5 о-р). При этом "0" на выходе триггера 9 блокирует работу шифратора 7, на его выходе запроса устанавливается "1" и коммутатор 8 постоянно подключает выход блока 5 к информационному входу регистра 6.

Режим регенерации задается установкой "1" на входе 13 (фиг.6а). Снимается сброс со счетчика 2, коммутатор 3 подключает к выходу 11 информационный выход счетчика, а к выходу 12 — информационный выход шифратора 7. Запись в блок 5 памяти блокируется, Блок 1 начинает генерировать синхросигналы (фиг. 6б,г). По состоянию счетчика (фиг.бе) из блока 5 выбирается байт признаков внешнего обращения к памяти, который по сигналу 1.6 (фиг.6г) заносится в регистр 6 (фиг.6 о-р). Если в байте эти признаки присутствуют, то по положительному фронту сигнала 1,4 (фиг. 6б) триггер 9 устанавливается в "0", и на выходе запроса шифратора 7 также устанавливается "0" (фиг.6 д), на его информационном выходе формируется код, соответствующий первому из "0" в разрядах регистра 6 (фиг,бж). Сформированный код с выходов 11 и 12 поступает на регенерацию динамической памяти и с выхода 12 — на вход дешифратора 18, По совпадению уровней "0" на обоих входах соответствующего элемента

20 эквивалентности на его выходе устанавливается "1". На выходах прочих элементов

20 сохраняется состояние соответствующих разрядов регистра 6. Поскольку сигнал запроса щифратора 7 к этому моменту оказывается сброшенным, выходы элементов 20 через коммутатор 8 подключены к информационному входу регистра 6 и сформированный код по следующему сигналу 1.6 заносится в регистр. Шифратор 7 формирует новый код по следующему признаку об. ращения. Процесс продолжается до установки в "1" всех разрядов регистра.

Поскольку код 111 формируется шифратором как при наличии "0" на последнем иэ его информационных входов, так и отсутствии

25 на регенерацию, и устройство вновь перей30

55 такового, последний из разрядов регистра 6 не задействуется.

При установке в "1" всех разрядов регистра выход запроса шифратора 7 устанавливается в "1", чем разрешается модификация счетчика 2 сигналом 1.4 и за- пись в регистр следующего байта признаков из блока 5. Если в следующем байте также присутствуют признаки обращения, сигнал запроса шифратора сбрасывается, дальнейшая модификация счетчика блокируется и коммутатор 8 вновь подключает выходы элементов 20 к информационному входу регистра 6, Если признаки внешнего обращения отсутствуют, модификация счетчика продолжается, при этом на информационном выходе шифратора сохраняется код 111.

После перехода счетчика 2 в состояние

111 он вырабатывает сигнал переноса (фиг.бс), который сбрасывается по следующему переключению счетчика, которое произойдет после снятия последнего иэ "0" в разрядах регистра. После сброса сигнала переноса будет сброшен и сигнал запроса дет к работе в режиме внешнего обращения.

Таким образом, в устройстве устанавливаются признаки внешних обращений по внешним адресам и адреса регенерации впоследствии формируются в соответствии с этими признаками, без затрат времени на регенерацию незадействованных адресов.

Формула изобретения

1. Устройство для регенерации динамической памяти, содержащее блок синхронизации, счетчик регенерации, адресный коммутатор, преобразователь кода адреса, блок памяти, регистр и приоритетный шифратор, информационный вход которого подключен к выходу регистра и информационному входу преобразователя кода, выход запроса приоритетного шифратора подключен к входу разрешения счета счетчика регенерации, информационный выход приоритетного шифратора подключен к первому входу первой группы информационных входов адресного коммутатора, второй вход первой группы информационных входов которого подключен к информационному выходу счетчика регенерации, входы второй группы информационных входов адресного .коммутатора являются адресными входами устройства, первый выход адресного коммутатора подключен к адресному ахо-. ду блока памяти и является первым адресным выходом устройства, второй выход адресного коммутатора подключен к адресному входу преобразователя кода адреса и.является вторым адресным выходом устройства, управляющий вход адрес1587с 94

7 ного коммутатора является входом запроса на регенерацию устройства и подключен к входу сброса счетчика регенерации и к первому входу блока синхронизации, второй вход которого является входом стробирования устройства, первый выход блока синхронизации является выходом окончания регенерации устройства, второй выход бло.ка синхронизации подключен к входу счета счетчика регенерации, третий выход блока синхронизации подключен к входу записи блока памяти, четвертый выход блока синхронизации подключен к синхровходу регистра и является выходом подтверждения устройства, третий вход блока синхронизации подключен к выходу переноса счетчика регенерации, первый выход преобразователя кода адреса подключен к инфсрмационному входу блока памяти, о т л и ч а ю щ е ес я тем, что, с целью повышения быстродействия устройства, в него введены второй коммутатор и триггер,. выход котооого подключен к входу разрешения приоритетного шифратора, информационный вход и вход сброса, триггера объединены и подключены . к входу сброса счетчика регенерации, синхровход триггера подключен к второму выходу блока синхронизации, выход второго коммутатора подключен к информацис нному входу регистра, первый информационный вход второго коммутатора подклюен к выходу блока памяти, второй информационный вход второго коммутатора подключен к второму выходу преобразователя кода, управляющий вход второго коммутатора под5 ключен к выходу запроса приоритетного шифратора, управляющий вход преобразователя кода является входом начальной установки устройства, вход разрешения записи блока памяти подключен к первому

10 входу блока синхронизации.

2. устройство поп.1, о тл и ч а ю ще ес я тем, что преобразователь кода адреса содержит дешифратор, элементы И, элементы эквивалентности и элементы ИЛИ, выхо15 ды которых являются первым выходом преобразователя, первые входы элементов

ИЛИ объединены и являются управляющим входом преобразователя, вторые входы элементов ИЛИ подключены к выходам соот20 ветствующих элементов И, первые входы которых подключены к первым входам соответствующих элементов эквивалентности и к соответствугощим выходам дешифратора, вторые входы элементов И подключены к

25 вторым входам соответствующих элементов эквивалентности и являются информационным входом преобразователя, входы дешифратора являются адресным входом преобразователя, выходы элементов экви30 валентности являются вторым выходом преобразователя.

1587594 б д г д

ФиО

1587594

Составитель С.Шустенко

Техред M.Моргентал Корректор Н,Король

Редактор Е.Папп

Производственйо-издательский комбинат "Патент", r, Ужгород, ул.Гагарина, 101

Заказ 2425, . Тираж 484 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5