Динамическое запоминающее устройство с коррекцией ошибок

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть использовано в качестве оперативной памяти с коррекцией ошибок. Цель изобретения - уменьшение времени восстановления работоспособности устройства достигается введением в него блока формирования отказов и его выполнение на элементах И, счетчике и элементе НЕ. Это позволяет не только выявлять отказавшие ячейки памяти, но и выдавать их адреса в процессор. 1 з.п. ф-лы, 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 G 11 С 29/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) 1133625 (21) 4490068/24-24 (22) 03.10.88 (46) 23.08.90. Бюл, М 31 (72) В.А.Корнышев и P.À.Волосников (53) 681.327.66(088.8) (56) Авторское свидетельство СССР

М 1133625, кл. G 11 С 29/00, 1983. (54) ДИНАМИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ

УСТРОЙСТВО С КОРРЕКЦИЕЙ ОШИБОК е

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, может быть использовано в качестве оперативной памяти с коррекцией ошибок и является усовершенствованием устройства по основному авт.св, М 1133625.

Цель изобретения — уменьшение времени восстановления работоспособности устройства.

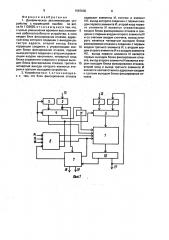

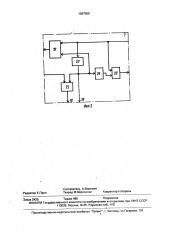

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2— функциональная схема блока фиксирования отказов.

Устройство (фиг. 1) содержит накопитель 1, счетчик 2, регистр 3 адреса, коммутаторы 4 и 5, блок 6 управления, блок 7 фиксирования отказов, формирователь 8 контрольных сигналов, регистр 9 регенерации, блок 10 коррекции, дешифратор 11, адресный 12 и информационный 13 входы устройства, управляющие входы 14-16 и выходы 17 — 19 устройства. Блок 7 фиксирования отказов содержит элементы И 20 — 22, счетчик 23 и элемент НЕ 24.

„„ Ц„„1587600 А2 (57) Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть использовано в качестве оперативной памяти с коррекцией ошибок. Цель изобретения — уменьшение времени восстановления работоспособности устройства —. достигается введением в него блока формирования отказов и его выполнение на элементах И, счетчике и элементе НЕ. Это позволяет не только выявлять отказавшие ячейки памяти, но и выдавать их адреса в процессор, 1 з.п. ф-лы, 2 ил.

Устройство работает следующим образом.

По входу 15 на второй вход блока 6 управления поступает синхронизирующая серия, Сигнал обращения к памяти поступает по входу 14 на первый вход 9 блока 6 управления, Частота синхросерии в три раза больше частоты поступления сигналов обращения. При поступлении сигнала "Запись" по входу 16 на третий вход блока 6 управления на первом и втором его выходах появляются единичные уровни, которые поступают на управляющие входы накопителя

1 и под воздействием которых производится запись информации.

Если по входу 16 подается сигнал "Чтение" (нулевой уровень), то появляется единичный уровень только на втором выходе блока 6, который поступает на соответствующий вход накопителя 1 и под воздействием которого производится считывание информации.

По второму синхроимпульсу единичный уровень появляется только на втором входе блока 6 управления, который поступает на

1587600 соответствующий вход накопителя 1 и вызывает считывание информации, В этом такте происходит регенерация, считывание и контроль информации. В этом такте в случае обнаружения ошибки на втором выходе блока 10 коррекции появляется единичный уровень, который поступает на один из входов элемента И 21, на вход счетчика 23 и вход элемента И 20. Так как счетчик 23 считает до двух, то íà его выходе остается нулевой уровень, который поступает на выход элемента НЕ 24, На выходе этого элемента единичный уровень вызывает повторное считывание информации из накопителя 1, При обнаружении ошибки повторно считается, что произошел отказ ячейки памяти в накопителе. Сигнал об ошибке с второго выхода блока 10 коррекции поступает на один из входов элемента И 20. Теперь на выходе счетчика 23 появляется единичный уровень, который поступает на вход элемента И 22, вход элемента НЕ 24, вход элемента

И 21 и на выход 19 устройства, С выхода элемента И 21 через второй выход блока 7 фиксирования отказов единичный уровень поступает на соответствующий вход блока 6 управления.

При этом появляются единичные уровни на первом и втором выходах блока 6 управления, которые поступают на управляющие входы накопителя 1 и производят запись информации.

Таким образом, промежуток обращения делится на три такта, В первом происходит запись или считывание информации, во втором — регенерация и чтение информации для ее контроля, в третьем — запись в память скорректированной информации, если в предыдущем такте при повторном считывании обнаружены ошибки. Первый синхроимпульс по второму входу блока 6 формирует единичный уровень на третьем его выходе и обеспечивает подключение через коммутаторы 4 и 5 подачу на адресные и информационный входы накопителя 1 соответствующих сигналов. Нулевой уровень этого сигнала подключает соответственно выход счетчика 2 и выход регистра 9 регенерации. Передним фронтом этого сигнала происходит добавление единицы к содержимому счетчика 2.

В цикле записи на вход 13 подается информация, подлежащая записи в накопи. тель 1. В формирователе 8 контрольных сиг. налов происходит формирование дополнительных битов кода Хэмминга, по= зволяющих обнаружить и исправлять одиночные ошибки. С выхвда блока 8 информационные биты и биты кода Хэмминга подаются на один из входов коммутатора

25 гистр 9 регенерации, Сигнал об ошибке с соответствующего выхода блока 10 поступа30

55

5. Единичный сигнал с третьего выхода блока 6 управления подключает через первый коммутатор 4 на адресные входы накопителя 1 и на вход дешифратора 11 содержимое регистра 3 адреса, а через второй коммутатор 5 на информационные входы накопителя 1 подключаются выходы формирователя

8. flop воздействием управляющих сигналов с соответствующих выходов блока 6 в накопителе I происходит запись информации.

В цикле считывания с входа 12 на вход регистра 3 адреса 2 поступает код-адреса, с входа 14 — сигнал обращения и с входа 16— сигнал считывания. Работа адресной части аналогична циклу записи. flop воздействием управляющего сигнала с второго выхода блока 6 управления в накопителе 1 происходит считывание информации по адресу, принятому из регистра 3. Считанные биты информации и биты кода Хэмминга поступают в блок 10 короекции, где в случае обнаружения единичной ошибки производится ее исправление и выдача на выход 17. Одновремено эта информация заносится на реет на вход блока 7, в котором производится повторное обращение к накопителю 1. Если при повторном считывании опять обнаружена ошибка,то разрешается прохождение адреса с выхода регистра 3 адреса, Если ошибка не обнаружена при повторном считывании, то нулевой уровень с выхода блока 10 коррекции поступает на вход блока У и закрывает его, препятствуя органиэации считывания информации еще раз.

Во втором такте блок 6 управления нулевым уровнем на третьем выходе подключает через коммутатор 4 на адресные входы накопителя 1 и входы дешифратора 11 содержимое счетчика 2, в результате чего происходит считывание из накопителя 1 информации в блок 10 коррекции. С соответствующего выхода блока 10 коррекции исправленная информация записывается в регистр 9 регенерации. В случае обнаружения ошибки блок 10 коррекции выдает сигнал на вход блока 7, Работа блока 7 аналогична предыдущему такту.

Таким образом, в предалагаемом устройстве происходит выявление отказавших ячеек памяти и выдача адреса отказавших ячеек в процессор. Выдача адреса отказавшей ячейки на индикацию позволяет принять меры по устранению неисправности, т.е. уменьшает время восстановления, что в свою очередь приводит к росту коэффициен- . та готовности устройства.

1587600

Формула изобретения

1. Динамическое запоминающее устройство с коррекцией ошибок по авт. св. М 1133625, о т л и ч а ю щ е е с я тем, что, с целью уменьшения времени восстановления работоспособности устройства, в него введен блок фиксирования отказов, адресный вход которого соединен с выходом регистра адреса, второй выход блока коррекции соединен с управляющим входом блока фиксирования отказов, первый выход которого соединен с вторым управляющим входом накопителя, четвертый вход блока управления соединен с вторым выходом блока фиксирования отказов, третий и четвертый выходы которого являются вторым и третьим выходами устройства.

2.Устройство поп.1,отл ича ю щеес я тем, что блок фиксирования отказов содержит элементы И, счетчик и элемент

НЕ, выход которого соединен с первым вхо. дом первого элемента И, второй вход первого элемента И является управляющим

5 входом блока фиксирования отказов и соединен с первым входом второго элемента И и со счетным входом счетчика, выход которого является четвертым выходом блока фиксирования отказов и соединен с первым

10 входом третьего элемента И, с вторым входом второго элемента И и с входом элемента

НЕ, выход первого элемента И является первым выходом блока фиксирования отказов, выход второго элемента И является вто15 рым выходом блока фиксирования отказов, второй вход и выход третьего элемента И являются соответственно адресным входом и третьим выходом блока фиксирования отказов.

1587600

Составитель А.Воронин

Техред M. Моргентал Корректор Н.Король

Редактор Е.Пап п

Производственно-.издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101

Заказ 2425 Тираж 485 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5