Устройство для асинхронного сопряжения каналов связи

Иллюстрации

Показать всеРеферат

Изобретение относится к технике связи. Цель изобретения - повышение точности сопряжения путем уменьшения фазовых флуктуаций при наличии нескольких переприемов. Устройство содержит блок 1 памяти, блок 2 управления, передатчик 3 команд согласования, фазовый детектор 4. Цель достигается введением блока 5 задержки, определителя 6 момента нестандартной коррекции, коммутатора 7 импульсов коррекции и анализатора 8 условий согласования. Устройство обеспечивает переприем двоичного сигнала из одного цифрового тракта в другой, обеспечивая девять типов коррекции, три из которых являются стандартными. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (19) (И) (Д1) Н 04 1 3/00!

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Так

vucm иокиша жала саглас

ЩФ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО.ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4376405/24-09 (22) 08.02,88 (46) 23.08.90. Бюл. У 31 (72) А.В.Савчук (53) 621.395.44 (088.8) (56) Авторское свидетельство СССР

N 748896, кл. Н 04 J 3/08, 19 77. (54) УСТРОЙСТВО ДЛЯ АСИНХРОННОГО

СОПРЯЖЕНИЯ КАНАЛОВ СВЯЗИ (57) Изобретение относится к технике связи. Цель изобретения — повышение точности сопряжения путем уменьшения фазовых флуктуаций при наличии не2 скольких переприемов. Устр-во содержит блок 1 памяти, блок 2 управления, передатчик 3 команд согласования, фазовый детектор 4. Цель достигается введением блока 5 задержки, определителя 6 момента нестандартной коррекции, коммутатора 7 импульсов коррекции и анализатора 8 условий согласования. Устр-во обеспечивает переприем двоичного сигнала из одного цифрового тракта в другой, обеспечивая девять типов коррекции, три из которых являются стандартными.

2 ил.

1587653

Изобретение относится к технике связи и может быть использовано в многоканальных системах с временным разделением каналов для передачи информации по цифровым трактам сис5 тем передачи с импульсно-кодовой модуляцией.

Целью изобретения является повышение точности сопряжения путем уменьшения фазовых флуктуаций при наличии нескольких переприемов.

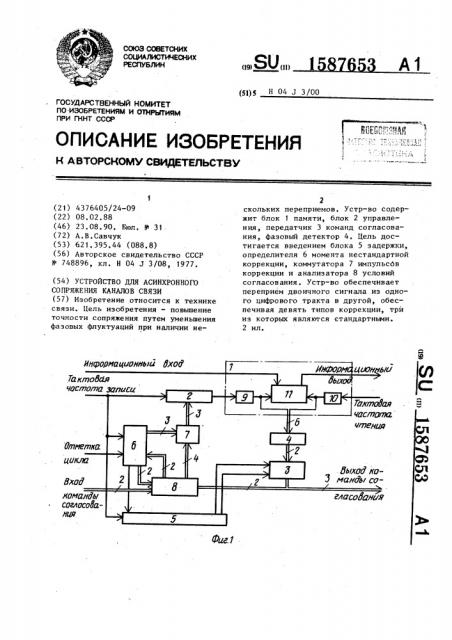

На фиг. 1 приведена структурная схема устройства, на фиг. 2 — таблица типов коррекций. 15

Устройство содержит блок памяти, блок 2 управления, передатчик 3 команд согласования, фазовый детектор 4, блок 5 задержки, определитель

6 момента нестандартной коррекции, коммутатор 7 импульсов коррекции, анализатор 8 условий согласования.

Блок 1 памяти содержит счетчик

9 записи, счетчик 10 чтения и узел

11 опера 7ивной памяти. 25

Устройство работает следуюшим образом.

На информационный вход поступает сигнал, структура цикла которого cdответствует рекомендации Х.51 МККТТ.

Для передачи двоичного информацион30 ного сигнала, несинхронизированного с аппаратурой цифрового тракта, используется двустороннее согласование скоростей. С этой целью цикл

35 имеет переменную длину и содержит

2560ф1 бит. Он разделен на четыре одинаковых субцикла, в каждом из которых передается трехбитовая команда согласования (КС), а последний бит в четвертом субцикле является согласующим битом (СБ).

Известная система согласования скоростей обеспечивает три типа коррекции в соответствии с КС: исключить

СБ ("-") отсутствие коррекции ("0") и добавить СБ ("+"). Предлагаемое устройство обеспечивает переприем двоичного сигнала из одного цифрово. го тракта в другой, при этом, каK показано на фиг, 2, необходимо учи50 тывать одновременно две команды согласования — КСР и КСТ. ГГоэтому число типов коррекции равно 9 (т.е. числу размещений из трех КС по две) и лишь три из этих девяти типов коррекции (4, 5 и 6 на фиг. 2) являются стандартными. Остальные шесть типов коррекции нестандартны.

Так, 1-й и 9-й тины коррекции заключаются в том, что принятая КС не выполняется, а из одного цифрового тракта в другой передается без изменения укороченный-или удлиненный цикл, при 2-м и 8-м типах коррекции выполняются операции, которые не соответствуют ни KCP ни КСТ, а при

3-м или 7 — м типах коррекции выполняются операции, вовсе не предусмотренные стандартом: соответственно добавляются или исключаются два согласующих бита (СБ).

Рассмотрим работу предлагаемого устройства на примере нестандартной коррекции третьего типа. В этом случае KCP имеет вид (Р1, Р2, РЗ) (001) и два бита Р1 = О и РЗ = 1 поступают на третий вход анализатора

8 условий согласования. На второй его вход поступают два бита Т1 = 1 и ТЗ = 0 (фиг.2) передаваемой КСТ, которая имеет вид (Т1, Т2, ТЗ) (100). КСТ вырабатывается в передатчике 3 команд согласования в зависимости от выходного сигнала фазового детектора 4, на вход которого поступают сигналы адресных счетчиков блока 1 памяти. Фазовый дискриминатор будет вырабатывать сигнал рассогласования до тех пор, пока блок

2 управления не выполнит "добавление" или "исключение" импульсов на входе счетчика адресов записи и, следовательно, не устранит причину появления сигнала рассогласования. Это происходит в момент коррекции, который определяется отметкой цикла, поступающей от блока цикловой синхронизации по шине Отметка цикла на второй вход определителя 6. В результате на третьем его выходе появляется импульс запуска блока 5 задержки, который обеспечивает последовательность операций в передатчике 3 команд согласования: после того, как КС появится на выходе передатчика 3 под воздействием импульса на фиксирующем его входе и произведена соответствую-. щая операция в блоке 2, в результате которой устраняется сигнал рассогласования на выходе детектора 4, необходимо "стереть сигнал рассогласования из памяти передатчика ) с помощью импульса, который поступает на его вхбд промежуточной записи с первого выхода блока задержки. В нашем примере в соответствии с КСР входной информационный сигнал имеет

5 1 укороченный цикл, в нем исключен СБ.

Выходной же информационный сигнал, появляющийся на втором выходе блока

1 памяти, должен иметь в соответствии с КСТ удлиненный цикл, в нем должны быть переданы два СБ. Эти два бита должны быть добавлены точно в те позиции входного информационного сигнала, которые определяются отметкой цикла, поступающей на второй вход определителя 6. Определитель 6 формирует импульсы, совпадающие во времени с моментами нестандартной коррекции. В результате логической обработки КСР, КСТ и этих импульсов на первом и втором выходах анализатора 8 появляются сигналы управления коммутатором 7 и определителем 6.

Сигналы управления коммутатором 7 обеспечивают прохождение через него на вход блока 2 управления тех импульсов с выхода определителя 6, которые необходимы для данной конкретной коррекции.

В нашем примере один из этих импульсов совпадает с 639-м битом четвертого субцикла и-го цикла, а второй — с 1-м битом первого субцикла (n+1)-ro цикла входного информационного сигнала. Блок 2 управления добавляет в сигнал тактовый частоты записи дополнительные тактовые импульсы на соответствующих тактовых интервалах. Выходной сигнал блока 2 управления подается на вход счетчика адресов записи блока 1 памяти.

В результате в ОЗУ блока 1 памяти

639-й и 1-й биты входного информационного сигнала записываются дважды: как информационные биты и как согласующие биты. Следовательно, выходной информационный сигнал будет содержать удлиненный цикл в точном соответствии с КСТ = (Т1, Т2, ТЗ) (100).

Остальные типы коррекции выполняются аналогично.

587653

Формула изобре тени

Устройство для асинхронного согфяжения каналов связи, содержащее последовательно соединенные блок управления, блок памяти, фазовый детектор и передатчик команд согласования, выход которого является выходом команды согласования устройства, информационный вход и информационный выход которого являются соответственно информационным входом и информационным выходом блока памяти, тактовый вход считывания которого является первым тактовым входом устройства, второй тактовый вход которого является первым входом блока управления, о т л ич а ю щ е е с я тем, что, с целью повышения точности сопряжения путем

2О уменьшения фазовых флуктуаций при наличии нескольких переприемов, введены последовательно соединенные определитель момента. нестандартной коррекции, анализатор условий согла25 сования и коммутатор импульсов коррекции, а также блок задержки, вьиоды которого соединены с вторыми входами передатчика команды согласования, выход которого подключен к вторым входам анализатора условий согласования, вторые выходы которого подключены к первым входам определителя момента нестандартной коррекции, вторые выходы которого соединены с вторыми входами коммутатора импульсов коррекции, выходы которого соединены с вторыми входами блока управления, первый вход которого соединен с вторым входом определителя момента нестандартной коррекции и первым входом блока задержки, второй вход которого подключен к третьему выходу определителя момента нестандартной коррекции, третий вход которого, а также третий вход анализатора условий согласования являются соответственно третьим тактовым входом устройства и входом команды согласования.

1587653

Составитель В,Паницкий

Редактор С.Пекарь Техред П.Сердцокова Корректор Л.Пилипенко

Заказ 2428 Тираж 528 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035,. Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул„ Гагарина, 101