Устройство для суммирования двух чисел с плавающей запятой

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, может быть использовано при реализации арифметических устройств электронных вычислительных машин с плавающей запятой. Цель изобретения - упрощение устройства. Предложенное устройство содержит два регистра, вычитатель порядков, сдвигатель, сумматор мантисс, блок нормализации, два коммутатора порядков и два коммутатора мантисс. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

PECi1YBËÈH (51)5 G 06 P 7/50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4609228/24-24 (22) 23.11.88 (46) 30.08.90. Бюл. ¹ 32 (71) Тернопольский финансово-экономический институт (72) З.И.Домбровский, M.A.Дуда и Л.А.Узлова (53) 681.325.5(088.8) (56) Авторское свидетельство СССР

¹ 1259248, кл. G 06 F 7/38, 1964.

Авторское свидетельство СССР № 1290300, кл, G 06 F 7/50, 1985.

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств вычислительных машин с плавающей запятой, .Целью изобретения является упрощение устройства для суммирования двух чисел с плавающей запятой.

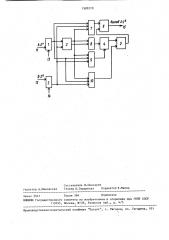

На чертеже представлена схема устройства для суммирования двух чисел с плавающей запятой.

Устройство для суммирования двух чисел с плавающей запятой содержит регистры 1 и 2, вычитатель 3 порядков, сдвигатель 4, сумматор 5 мантисс, блок 6 нормализации, коммутаторы 7 и 8 порядков, коммутаторы 9 и 10 мантиссы, входы ll и 12 слагаемых устройства, тактовые входы 13 и 14 устройства, выход 15 суммы устройства.

Устройство для суммирования двух чисел с плавающей запятой работает следующим образом.

SU„„1589270 А 1

2 (54) УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ ДВУХ

ЧИСЕЛ С ПЛАВАЮЩЕЙ ЗАПЯТОЙ (57) .Изобретение относится к вычислительной технике, может быть использовано при реализации арифметических устройств электронных вычислительных машин с плавающей запятой. Цель изобретения — упрощение устройства. Предложенное устройство содержит два регистра, вычитатель порядков, сдвигатель, сумматор мантисс, блок нормализации, два коммутатора порядков и два коммутатора мантисс. 1 ил.

Вначале определяется разность порядков. Для этого с выхода регистра 1 по- % а рядок Х первого слагаемого подается на первый вход вычитателя 3 порядков, с выхода регистра 2 порядок Y второго слагаемого подается на второй (, Д вход вычитателя 3 порядков. В вычита- Q© теле 3 порядков определяется разность {© порядков Х-Y в обратном коде. При этом, ф если Х > 7 (в этом случае запись pasности порядков в обратном коде совпадает с записью разности порядков с прямом коде), то на выходе переноса вычитателя 3 порядков будет единичный сигнал и в блок 6 нормализации через коммутатор 7 поступает больший порядок Х. При этом мантисса В второго слагаемого через коммутатор 9 поступает на информационный вход сдвигателя 4, мантисса А слагаемого через коммутатор 10 поступает на вход второго слагаемого сумматора 5 мантисс, а разность X-7 с выхода вычитателя.1589270 порядков через коммутатор 8 беэ изменения поступает на вход второго сдви1 а сдвигателя 4. В сдвигателе 4 осуществляется сдвиг мантиссы В второго слагаемого на величину разности порядков X-Y после чего сдвинутая мантисса В второго слагаемого поступает на вход первого слагаемого сумматора

5 мантисс. Мантисса А первого слага.е- 10 мого поступает на вход второго слагаемого сумматора 5 мантисс без сдви га. Далее сдвинутая мантисса В второ го слагаемого и несдвинутая мантисса

А первого слагаемого складиваются в 15 сумматоре 5 мантисс. С выхода сумма= тора 5 мантисс и коммутатора 7 мантисса и порядок результата поступают в блок 6 нормализации, в котором резуль1гат корректируется и передается на 20 выход 15 устройства. !

В случае, если Х <У то на выходе переноса вычитателя 3 порядков — нуле25 вой сигнал и в блок 6 нормализации через коммутатор 7 поступает порядок

При этом мантисса А первого слагаемого через коммутатор. 9 поступает на информационный вход сдвигателя 4, мантисса В второго слагаемого через ком- З0 мутатор 10 — на вход второго слагаемого сумматора 5 мантисс, а разность

Х-Y порядков поступает в коммутатор

8, где инвертируется, Инверсное значение разности Х-Y поступает на 35 вход кода сдвига сдвигателя 4. В сдвигателе 4 осуществляется сдвиг мантиссы А первого слагаемого на величину. модуля разности порядков Х-7, после. чего сдвинутая мантисса А первого слагаемого поступает на вход первого слагаемого сумматора 5 мантисс °

Мантисса В второго слагаемого поступает на вход второго слагаемого сумматора 5 мантисс без сдвига. Далее сдвинутая мантисса А первого слагаемого и несдвинутая мантисса В BTO рого слагаемого складываются в сумматоре 5 мантисс. С выхода сумматора

5 мантисс и коммутатора 7 мантисса 50 и порядок результата поступают в блок

6 нормализации, в котором результат корректируется, нормализуется и передается на выход 15 устройства.

Формула изобретения

Устройство для суммирования двух чисел с плавающей запятой, содержащее дв а регис тра, сдвигатель, сумма тор мантисс, вычитатель порядков, два коммутатора порядков, блок нормализации, причем выходы первого и второго слагаемых устройства соединены с информационными входами соответствующих регистров, управляющие входы которых подключены к первому и второму тактовым входам устройства, выход разрядов порядка первого регистра соединен с входом уменьшаемого вычитателя порядков и с первым информационным входом первого коммутатора порядков, второй информационный вход которого подключен к выходам разрядов порядка второго регистра и к входу вычитаемого вычитателя порядков, выход переноса которого соединен с управляющими входами соответственно первого и второго коммутаторов порядков, выход . первого коммутатора порядка соединен с входом порядка блока нормализации„ вход мантиссы которого соединен с выходом сумматора мантисс, вход первого слагаемого сумматора мантисс соединен с выходом сдвигателя, вход кода сдвига которого соединен с выходом второго коммутатора порядка, информационный вход которого соединен с выходом разности вычитателя порядков, выход блока нормализации является выходом результата устройства, о т л и ч а ю щ ее с я тем, что, с целью упрощения устройства, оно содержит первый и второй коммутаторы мантиссы, причем выходы разрядов мантиссы первого регистра соединены соответственно с первыми информационными входами первого и второго коммутаторов мантиссы, выходы разрядов мантиссы второго регистра соединены соответственно с вторыми информационными входами первого и второго коммутаторов мантиссы, выход переноса вычитателя порядков соединен с управляющими входами первого и второго коммутаторов мантиссы, выходы которых соединены соответственно с информационным входом сдвигателя и входом второго слагаемого сумматора мантисс.

1 589270

Составитель Н.Смосарев

Техред Л.Сердюкова Корректор Т.Малец

Редактор А.Маковская

Тираж 564

Заказ 2541 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4!5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101