Устройство для вычисления модуля комплексного числа

Иллюстрации

Показать всеРеферат

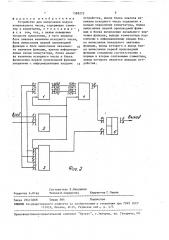

Изобретение относится к вычислительной технике и может быть применено в цифровых вычислительных машинах, специализированных вычислительных устройствах, устройствах цифровой обработки сигналов и вычислительных средах, построенных на больших интегральных схемах. Цель изобретения - повышение точности вычисления модуля комплексного числа. Устройство для вычисления модуля комплексного числа содержит коммутатор 1, блок анализа 2 величины исходного числа, блок вычисления 3 первой производной функции, блок вычисления 4 начального значения функции, сумматор 5 с соответствующими связями. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) А1 (51)5 С 06 F 7/552

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

1 (21) 4477659/24 — 24 (22) 29.08.88 (46) 30.08.90. Бюл, У 32 (72) В.A.Ìàêóøêèí, С.В.Красовский и Ю.Е.Белявский (53) 681.325(088.8) .(56) Авторское свидетельство СССР

9 877531, кл. G 06 F 7/552, 1981.

Авторское свидетельство СССР

В 1001085, кл. G 06 F 7/38, 1981. (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ

КОМПЛЕКСНОГО ЧИСЛА (57) Изобретение относится к вычислительной технике и может быть примене2 но в цифровых вычислительных машинах, специализированных вычислительных устройствах, устройствах цифровой обработки сигналов и вычислительных средах, построенных на больших интегральных схемах. Цель изобретения - повышение точности вычисления модуля комплексного числа. Устройство для вычисления модуля комплексного числа содержит коммутатор 1, блок 2 анализа величины исходного числа, блок 3 вычис" ления первой производной функции, блок

4 вычисления начального значения функции, сумматор 5 с соответствующими связями. 2 ил.

1589?72

f(X К)-а{Х К )+--.— --- (Х-Х ) f (ХО о, о о -,3Х о f {X0 Yo)

+ - — - — — -. (Y-Y ) ду о где Й(Х,Y ) — начальное значение о о функции;

8f (X. Yо) . 3f (X., Yо)

— — — - .ëò X ) .— — j — — (Y -Y ) 30 первая производная функции.

Устройство работает следующим образом.

Коды действительной и мнимой составляющих исходного комплексного числа поступают одновременно на информационные входы коммутатора 1, блока 2 анализа величины исходного числа и 40 блока 3 вычисления первой производной функции 3, При этом на выходе блока. анализа величины исходного числа 2 формируется сигнал управления коммутатором 1, блоком 3 вычисления пер- 45 вой производной функции и блоком 4 вычисление начального значения .функции причем уровень сигнала зависит

1 от величины обеих составляющих исходного комплексного числа.

Если обе составляющие исходного комплексного числа меньше определенного порогового значения Z то через коммутатор 1 на вход блока 4 вычисления начального значения функции поступают полные значения обеих состав55 ляющих исходного комплексного числа.

В блоке 4 вычисления начального значения функции проводится обработка входИзобретение относится к вычислительНой технике и может быть применено в

Цифровых вычислительных машинах, специализированных вычислительных устрой- 5 ствах, устройствах цифровой обработки сигналов и вычислительных средах, построенных на больших интегральных схемах.

Цель изобретения — повьппение точности вычислений.:

На фиг.1 представлена структурная схема устройства; на фиг.2 - пример

Конкретного исполнения.

Устройство содержит коммутатор 1„ 15 блок 2 анализа величины исходного чис4а блок 3 вычисления первой производйой функции, блок 4 вычисления начального значения функции и сумматор 5, В основу работы устройства положе- 20 но разложение функции в ряд Тейлора ных данных в соответствии с выражением

A= Х + (2) где X Y — полные значения составляюгде Х,Y — округленные до величин ДХ и L)Y значения составляющих исходного комплексного числа.

В блоке 3 вычисления первой производной функции проводится при этом обработка входных данных в соответствии с выражением

ХОДХ YOBY

К=- — -а — — + — —— Гх +т, / х +т (4) Полученные величины начального значения функции и первой производной функции поступают на входы операндов сумматора 5, с выхода которого снимается конечный результат вычисления модуля комплексного числа, полученный в соответствии с выражением,Г а о. Х дХ

11 = 1 Х +Y + — - — — — - + о о

Xo +Y

У,ВУ

+ (5)

+v, Величина пОрогового значения Z составляющих исходного комплексного числа для блока 2 анализа величины исходного чис,па определяется исходя из разрядности входов и выхода блока 4 щих исходного комплексного числа.

В связи с тем, что вычисление проводится с полными значениями составляющих исходного комплексного числа по оптимальному для цифровой техники алгоритму, то первая производная функция не вычисляется и имеет нулевое значение.

Если хотя бы одна из составляющих исходного комплексного числа больше определенного порогового значения

Z, то через коммутатор 1 на вход блока 4 вычисления начального значения функции поступают округленные до величины dX 8Y соответственно значения составляющих исходного комплексного числа. В блоке 4 вычисления начального значения функции проводится обра-" ботка входных данных в соответствии с выражением

А -: /Х 1, (3) 158927 вычисления начального значения функции таким образом, чтобы входные данные не превышали разрядности входов блока 4 вычисления начального эна5 чения функции, а результат полученный при вычислении в соответствии с выражением (2) или (3), не выходил эа .пределы разрядности выхода блока.

Величина округления Л Х (d Y) действительной (мнимой) составляющих исходного комплексного числа определяется исходя из разрядности входа блока 3 вычисления первой производной функции таким образом, чтобы совокупность используемых разрядов данных Х, Y 4 Х, ЛУ не выходила за о о пределы разрядности входов блока 3 вычисления первой производной функции.

Рассмотрим функционирование устрой- 20 ства на примере обработки восьмиразрядных комплексных чисел (фиг.2).

Восьмиразрядные (О-7р) коды действительной и мнимой составляющих исходного комплексного числа с входов 25 устройства поступают одновременно на входы коммутатора 1, выполненного на основе мультиплексоров "иэ 2 в 1", блока 2 анализа величины исходного числа, выполненного на основе ППЗУ с 30 организацией 1024xl, и блока 3 вычисления .первой производной функции 3, выполненного на основе ППЗУ с организацией 1024х4, причем на блок 2 анализа величины исходного числа посту пают старшие (5 — 7р) разряды обеих составляющих исходного числа, а на блок

3 вычисления первой производной функции поступают 1-й и 2-й разряды обеих составляющих исходного комплексно- 40

rо числа, соответствующие величине округления dХ (jlY) а также старшие (5-7р) разряды обеих составляющих исходного комплексного числа, соответствующие округленному значению

Хо (У ). Число используемых разрядов составляющих исходного комплексного числа определено разрядностью входов блока 3 вычисления первой производной функции. SO

В блоке 2 анализа величины исходного числа проводится сравнение обеих составляющих исходного комплексного числа с пороговым значением Z равным для данного случая 32 „, и вырабаты. вается сигнал управления коммутатором

1, блоком 3 вычисления первой производной функции и блоком 4 вычисления начального значения функции, при2 б чем если обе составляющие исходного числа меньше порогового значения Е, то сигнал управления имеет низкий уровень, если хотя бы одна из составляю-.. щих равна или больше порогового значения, — высокий уровень. Одновременно в блоке 3 вычисления первой производной функции проводится вычисление в соответствии с выражением (4).

Величина порогового значения определена разрядностью информационных входов блока 4 вычисления начального значения функции.

Если сигнал управления имеет низкий уровень, то через коммутатор 1, на . вход блока 4 вычисления начального значения функции поступают полные значения составляющих исходного комп — . лексного числа, занимающие в данном случае 0-4р, В противном случае на вход блока 4 нычисления начального значения функции поступают старшие (3-7р) разряды обеих составляющих исходного комплексного числа, т.е. их округленные значения.

В блоке 4 вычисления начального значения функции, выполненном на основе ППЗУ с организацией 2048х8, происходит вычисление в соответствии с Ъ выражением (3), если управляющий сигнал имеет низкий уронень, или (4), если высокий, Одновременно в блоке производится ограничение результата вычисления до величины 255 свяfo занное с разрядностью выхода блока.

Разрядность информационных входов блока 4 вычисления начального значения функции (О-9р) определяет величину порогового значения 2 для блока

2 анализа величины исходного числа таким образом, чтобы на каждую из составляющих приходилось по 5 разрядов (О-4р или 3-7р), что соответствует величине порогового значения Z=32 .

При этом старший разряд входа блока

4 вычисления начального значения функции является входом управления ранного блока.

Полученные результаты начального значения функции (8 разрядов) и первой проиэнодной функции (4 разряда) поступают на входы восьмираэрядного двоичного сумматора 5, с выхода которого снимается конечный результат вычислений н девятиразрядном коде (8 разрядов выхода сумматора и 1 разряд переполнения сумматора), I589272

ЛыА ж

С ос тав и тель В, Макушкин

Редактор А.Огар Техред Л. Сердюков а Коррек тор С. Черни

Заказ 2541/ДСП Тираж 564 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.Ужгород, ул. Гагарина,101

Формула изобретения

Устройство для вычисления модуля комплексного числа, содержащее сумматор и коммутатор, о т л и ч а ю щ

Ф с я . тем, что, с целью повышения точности. вычисления, в него введены блок анализа величины исходного числа, блок вычисления первой производной функции и блок вычисления начальноГо значения функции, причем информационные входы коммутатора, блока анализа величины исходного числа и блока вычисления первой производной функции соединены с информационными входами устройства, выход блока анализа величины исходного числа подключен к, входам управления коммутатора, блока вычисления первой производной функции и блока вычисления начального значения функции, выходы коммутатора подключены к информационным входам блока вычисления начального значения функции, выход которого и выход блока вычисления первой производной функции соединены соответственно с первым и вторым слагаемыми сумматора выход которого является выходом устройства.