Многоканальное устройство для приоритетного подключения абонентов к общей магистрали

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в многомашинных и многопроцессорных вычислительных системах. Цель изобретения - повышение быстродействия устройства. Устройство в каждом канале содержит триггеры 5-7, элементы И8-11, формирователи импульсов 12,13, элементы НЕ 14,15, элементы И-НЕ 16, 17, элемент задержки 18, блок 23 задержки. Устройство позволяет организовать подключение абонентов к общей магистрали в соответствии с их приоритетами, которые могут оперативно изменяться при настройке вычислительной системы. 2 ил.

СОЮЗ СОВЕТСНИХ

РЕСПУБЛИН ае аи

277 A2 (51)5 0 06 У 9/46

ОПИСАНИЕ И3ОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И. ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (61) 1458873 (21) 4639245/24-24 (22) 18,01,89 (46 ) 30.08.90. Бюп. У 32 (72 ) В. В. Туранинин, С, Н, Ази, В, В. важни кон и В. Г. 11опов (53) 681. 325 (088. 8) (56 ) Авторское свицетельство СССР

М"- 1458873, кл. 0 06 Е 9/46, 1987. (54 ) МНО Г(КАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ

ПРИОРИТЕТНОГО ПОДКЛЮЧЕНИЯ АБОНЕНТОВ

К ОБЩЕЙ МАГИСТРА 1И (57) Изобретение относится к вычислительной технике и может быть исполь2 зонано н многомашинных и многопроцессорных вычислительных системах, Цель изобр етения — повышение быстроцействия устройства. Устройстно в кажцом канале соцержит триггеры 5-7, элементы И 8-11, формирователи 12 13 импульсон, элементы НЕ 14, 15, элементы И вЂ” НЕ 16, 17, элемент 18 зацержки, блок 23 з ацержки ° .У стройство поз воляет организовать поцключение абонентон к общей магистрали н соответствии с их приоритетами, которые могут оперативно Hýìåíÿòüñÿ при настройке вычислительной системы. 2 ил.

1589277

Иэобрнтение относится к нычислительной технике, может быть примене.но в многомашинных и,многопроцессорных вычислительных системах исполь5 эующих цпя обмЕна цЕнными общую магистраль (ОМ) ° и является .Усонершенстнованием изобретения по авт. св..В 1458873, Цель изобретения - повышение быстроцейстния устройства за счет вре" меиного назначения максимально возможного приоритета одному из каналов, .которые на данном этапе функционирования устройства вь»целены н группу каналов ° претенцующих на захват OM„

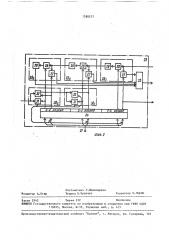

На фиг, 1 изображена структурная схема устройства; на фи г, 2 — струк. турная схема блока задержки (пример для вычислительной системы, включав- 20 щей четыре абонента ), Устройство соцержит (фиг. 1 ) шину

1 разрешения ОМ, шину 2 запрещения

ОМ, сигнальную шину 3, каналы 4, каждый. из которых включает триггеры 5-7, 25 элементы И 8-11, формирователи 12 и

13 импульсов, элементы HE 14 и 15, элементы И-НЕ 16 и 17, элемент 18 задержки, запросный вход 19 устройства, ответный вход 20 устройстна, группу кодовых нхоцон 21 устройства, выхоц

22 устройстна и блок 23 зацержки, Блок 23 задержки (фиг. 2) образуют регистр 24, элемент 1ЦИ 25, узлы 26 э ацержки (по коли честну Р аз рядов Р е гистра), каждый из которых содержит элементы И 27 и 28 3 элемент 29 задержки, и узлы 30 переноса (на один меньше, чем количество разрядов регистра) каждый из которых состоит из 40 элементов И 31 и 32.

Соединение ныходон соотнетстнующих элементов .каналов 4 на кажцой из шин 1-3 реализует функцию МОНТАЖНОЕ И, Устройство работает следующим образомом.

В исхоцном состоянии триггеры 5-7

° нахоцятся н нулевом состоянии на шинах 1-3 установлены сигналы логической ециниць», В случайные моменты времени источники информации (например, процессоры) по мере необходимости пере.дачи сообщений другим процессорам ныцают на регистры .24 через соответстнующие группы вхоцов 21 парафаэным кодом коцы приоритетов (которые не могут быть оцинаконымн, но при настройке вычислительной системп могут оперативно Изменяться ), а на соотнетствующие нхоцы 19 - сигналы, устананлинающие триггеры 5 соответствующих каналов 4 в единичное состояние (процессоры и ОМ на фиг. 1 не показаны ), Рассмотрим работу одного из каналов 4 (остальные каналы работают аналогично ), . Сигнал с единичного выхода триггера 5 через открытый элемент И 8 устанавливает триггер б н единичное» остояние, закрын;я при этом через шину

1 элементы И 8 нсех каналон 4. Сигнал с единичного ныхода триггера б через открытый элемент И 9 запускает формирователь 12 импульсов, который выдает одиночный импульс, поступающий на первый вход б1»ока 23, Поскольку на регистрах 24 блоков 23 различных каналов 4 установлены различные коды, то сигналы на первых выходах блоков 23 различных каналон 4 появляются в различное время (тем раньше, чем вьппе гриоритет процессора, подключенного к данному каналу ), Так, цля четырехпроцессорной вычислительной системы коцы приоритетон процессорон должны иметь следующий ниц: 111, 011, 001, 000 (коцы записаны н порядке возрастания приоритета), Если,например, н цанное время на OM претендуют дна процессора, имеющие первый и третий приоритеты, т. е. их коды приоритетон соответственно равны 000 и

011, то после поступления сигнала иа первый нхоц блока 23, на регистре которого установлен коц 000, на первом выходе этого олока 23 поянляется ециничный сигнал через время, которое обусловлено задержкой поступившего сигнала на элементе И 27 узла 26» и элемента ИЛИ 25 этого блока 23. На, первом выходе блока 23, на регистре

24 которого установлен коц 011, появ1 ляется сигнал через время, обусловленное прохожцением сигнала, поступающего на первый вход этого блока 23, через элемент И 28 и элемент 29 задержки узла 26», элемент И 28 и элемент

29 задержки узла 26» элемент И 27 узла 26 и элемент ЛИ 25 данного блока 23, После появления сигнала на первом выходе блока 23, имеющего максимальный приоритет, срабатывает элемент И 10 канала 4, к которому подключен наиболее приоритетный процессор, и через выход 22 этому процессо""

Ру выдается сигнал, увецомпяющий его о том, что OM захвачена и он может. передавать по ней информацию, Этот же сигнал переводит триггер 7 рассмат277

И 32 узлов 36 и 30„" переноса уста"" навлинает триггер первого разряца регистра 24 в нулевое состояние, т.е, временно придает цанному каналу 4 макS ъ снмальный приоритет, что собес е ина" ет в дальнейшем при захвате ON (после того, как ее освободит первый процессор ) исключение задержки сигнала (на первом ныходе блока 23) на элементах

И 28 и элементах 29 зацержки узлов

26, и 26 задержки. После того, как в третьем канале на втором выходе блока 23 появится единичный сигнал (он

15 появится при установке триггера первого разряда регистра 24 в нулевое состояние) на ныхоце элемента И-HE

16, а спецовательно, и на шине 3 устанавливается нулевой сигнал, что исключает формиронание новых импульсов на ныхоце формирователя 13 импульсов. фор мул а

Многоканальное устройство для приоритетного подключения абонентов к общей магистрали -по авт,св. У 1458873, о т л и ч а ю m е е с я тем, что, с

30 целью повышения быстроцействия, в кажцый канап устройства дополнительно ввецены цва элемента И-HE и элемент задержки, причем цополнительный второй выход блока зацержки соединен С пер"

35 ным входом первого элемента И-HE. второй и третий входы которого соецинеьы соответственно с ныхоцом нторого элемента НЕ и с единичным выходом второго триггера, ныхоц первого элемента Л-HE

4Q соединен с цополнительной сигнально шиной устройства, ныхоц второго формирователя импульсов соецинен через элемент задержки с перным нхоцом второго элемента И-HE второй ход и ны45 ход которого соединены соответственно с дополнительной сигнальной шиной устройстна и с цополнительным четвертым . входом четвертого элемента И, единичный выход первого разряда регистра

5Q блока задержки является дополнительным вторым ныхоцом блока задержки, 5 1589 риваемого канала в единичное состояние, устананлиная нулевой сигнал на шине 2, закрывая (так как шина 2 реал лизует функцию МОНТАЖНОЕ И) элементы

И 9 и 10 и открывая через элементы

HE 14, элементы И I! (по второму входу) всех каналов, При этом к моменту ныцачи сигнала с перного ныхоца блока

23 канала 4 (не захватившег OMJ, на регистре 24 которого устанонлен коц

011, элемент Л 10 этого канапа 4 закрыт, а на выхоце элемента И 11 (который открыт в данном канале 4 по первому входу единичным сигналом с ециничного выхода триггера 6, по третьему нходу - ециничным сигналом с выхода элемента НЕ 15, а по четвертому нхоцу — ециничным сигналом с выхода элемента И-НЕ 17, на первый нхоц кото" рого подан нулевой сигнал с выхода элемента 18 зацержки) поянляется ециничный сигнал (нысокий потенциал ), по. переднему фронту которого запускается формирователь 13 импульсов, ныдающий одиночный импульс, поступающий на элемент 18 зацержки и на нторой вход блока 23 цанного канала 4.

Этот сигнал через открытые элемент

И 32 узла 302 переноса и элемент Л 31 узла переноса 30< устанавливает .триггер второго разряда (фиг. 2) регистра 24 в нулевое состояние, т.е. временно придает цанному каналу 4 коц приоритета 001, После этого н данном. канале 4 с выхода элемента 18 зацержки на нхоц элемента И-HE 17 поступает одиночный импульс (ециничньгй сигнал ),. который приводит к кратковременному (на время цей TBHH импульса) появлению на выходе элемента И-НЕ 17 нулевого сигнала, а после того, как на ныходе элемента Л-НЕ 17 вновь появится ециничный сигнал, через элемент И 11 (ннонь запускает я по переднему фронту единичного сигнала) формиронатель13 импульсон, который выдает одиночный импульс, поступающий на элемент 18 задержки и на второй вход блока 23 данного канала 4.

Этот сигнал через открытые элементы из обретения

1589277

ФИ2. 8

Составитель Г,Пономарева

Техрец A,Кравчук Корректор С,Черни Pe.дактор А.Orap.

Заказ 2542 Тираж 572 Подписное

ВИИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ С СР

113035, Москва„ Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101